|

|

|||||||||||||||||||||||||||||||||||||||||||||

| Major activities |

1998

|

1999

|

2000

|

2001

|

|

Investigation of SLD languages |

SLDL(Rosetta)

|

SLDL(Rosetta)-Cont'd |

||

|

Research needs |

Meeting with designers

|

Questionnaire/Analysis needs

|

Analysis needs

|

-

|

|

Research seeds |

-

|

-

|

Research seeds

|

-

|

|

Proposal for the |

-

|

Initial Proposal SLD meeting(ASP-DAC) |

Refined Proposal |

Trend of System Level Design |

| Major activities |

2001

|

2002

|

|

|

Investigation of Standardization trends(Finished) |

-

|

||

|

Research and Investigation of the technology of SLD |

Design Methodology

|

-

|

Finished the activity

|

|

Modeling

|

-

|

Finished the activity

|

|

|

Estimation

|

-

|

Finished the activity

|

|

![]()

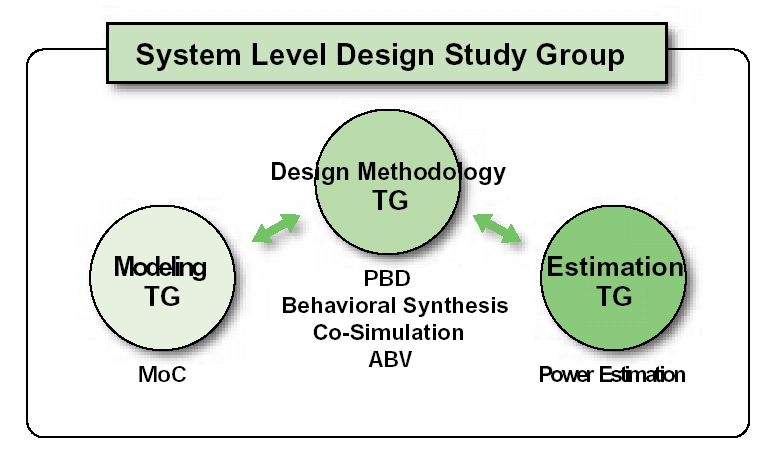

Based on the accumulated knowledge, extended research and investigation was conducted for 3 interested area in the proposed system level design flow by forming a task group for each area.

Design Methodology Task Group

To realize the proposed system level design flow, this group investigated today's available technology on behavioral synthesis, co-simulation and assertion based verification (ABV) towards platform based design(PBD) and proposed the usage and improvements for those technologies.

Modeling Task Group

For the purpose of the improvement of design productivity and quality, Modeling Task Group investigated Models of Computation and performed the characteristic comparison for those MoCs. Based on this result, the group further examined the applicable design phase and application area for those MoCs.

Estimation Task Group

Currently, low power design for SoC is relied on layout, circuitry and process technology and not matured yet in system level design arena. This group researched the power estimation techniques during the system level design phase, made an assessment in terms of utilization and practicality and made a proposal for the improvement of the technology.

1998 fiscal year

- EDA annual report 1998 published by EIAJ

1999 fiscal year

- EDA annual report 1999 published by EIAJ

- System Level Design Flow (1999 version)

![]() (407KB)

(407KB)

2000 fiscal year

- EDA annual report 2000 published by JEITA

- Technical report 2000 published by

JEITA (Japanese) ![]() (zip:

1,160KB)

(zip:

1,160KB)

- Biwako workshop paper (Japanese)

![]() (763KB)

(763KB)

2001 fiscal year

- EDA annual report 2001 published by JEITA

- Technical report 2001 was compiled

2002 fiscal year

- Activity report of SLD Study Group in the EDS Fair 2003 brochure

(Japanese) ![]() (1,822KB)

(1,822KB)

- EDA annual report 2002 (it will be published in July/2003 by JEITA)

![]()

Cadence Design Systems, Japan

Nobuhiro Irie

FUJITSU LIMITED

Masato Otsuka

Future Design Automation Co., Ltd.

Kundo Lee

InterDesign Technologies, Inc.

Dai Araki

Matsushita Electric Industrial Co., Ltd.

Kazuyoshi Takemura

Mentor Graphics Japan Co., Ltd

Siu-ki Wan (Co-chair)

MITSUBISHI ELECTRIC CORPORATION

Hiroyuki Yamamoto

Hitoshi Kimura

NEC Corporation

Hitoshi Kurosaka (Chair)

Nihon Synopsys Co., Ltd.

Yoichi Sugiyama

Oki Electric Industry Co., Ltd.

Kazuhiro Yoshinaga

Renesas Technology Corp.

Kazuhiko Kobayashi

RICOH COMPANY, LTD.

Yasutaka Tsukamoto

SANYO Electric Co., Ltd.

Hirofumi Saitoh

Seiko Instrument Inc.

Makoto Makino

SHARP CORPORATION

Masayuki Yamaguchi (Co-chair)

Sony Corporation

Takehisa Hashimoto

TOSHIBA CORPORATION

Nobuhiro Nonogaki

MITSUBISHI ELECTRIC CORPORATION

Mitsuhiro Yasuda (Adviser)

Kochi University of Technology

Masayoshi Tachibana (Guest professor)

Osaka University

Masaharu Imai (Guest professor)

Saitama University

Norihiko Yoshida (Guest professor)

![]()

![]()

![]()

EDA Home Page / ![]()

![]()

| Last updated :

Mar/12/2003

|

|