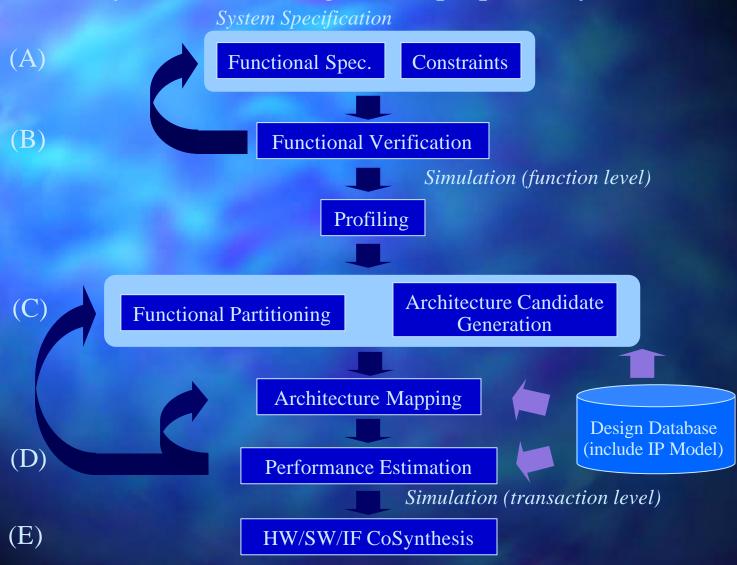

# System Level Design Flow proposed by SLD-SG

Masayoshi Tachibana (Toshiba Corp. Semiconductor Company)

Organized by EIAJ/EDA Technical Committee

## SLD Systems and Design Flow proposed by SLD-SG

#### System Level Description Algorithm **Functional Description** Profiled Profiled result (C) **Process Model Architecture Model** + BUS Configuration + HW/SW Block + Functional Block Profiled + Communication result Mapping (D) Transaction Level Model + Processing Time + Data Transfer Algorithm

Description and Model

## SLD Systems and Design: What to DO

### (A) & (B)

**Define System Specification**

What to DO: Describe required specification and design constraints

Technology: (Unified) System Level Description Language

System level verification technique

*Date* : 2000(?)

#### (C)

Functional Partitioning / Architecture Candidates Generation

What to DO: Generation of Architecture Candidates

Process modeling

Simulation and Profiling in functional level

*Technology*: Process model generation

Architecture model generation

Date: 2002~2003

## SLD Systems and Design: What to DO

(D) <u>Architecture Selection</u>

What to Do: Process-Architecture mapping

Performance estimation

*Technology*: Transaction level model generation

Process-Architecture mapping

Performance estimation

*Date*: 2002~2004

(E) <u>Interface to Implementation phase</u>

What to Do: HW/SW/IF CoSynthesis

*Technology*: Inter-process communication interface generation

HW/SW CoSynthesis

*Date* : 2004