### System Level Design Technologies and System Level Design Languages

#### SLD Study Group EDA-TC, JEITA

http://eda.ics.es.osaka-u.ac.jp/jeita/eda/english/project/sld/index.html

## Problems to Be Solved

### System Level Design Technologies

#### Research Target

- "EDA Technology Roadmap Toward 2002" EIAJ/EDA-TC/EDA Vision Study Group (1998)

- Universities/Research Centers

- POLIS http://www-cad.eecs.berkeley.edu/Respep/Research/hsc/abstract.html "Hardware-Software Co-Design of Embedded Systems, The POLIS Approach" Kluwer Academic Publishers(1997)

- OCAPI-xI http://www.imec.be/ocapi

- IpChinook http://www.cs.washington.edu/research/chinook/index.html

- Vendors

N2C

- CoCentric http://www.synopsys.com/

- http://www.coware.com/

- VCC http://www.cadence.com/

### Roadmap of EDA Technologies

|                                                                           |      |      |      |    | In the prediction, almost all technologies are in the trial |  |  |

|---------------------------------------------------------------------------|------|------|------|----|-------------------------------------------------------------|--|--|

| Items                                                                     | 1997 | 1998 | 1999 | 20 | phase in 2000 !!                                            |  |  |

| [System Level Design]                                                     |      |      |      |    | How in the real world?                                      |  |  |

| Standardization of system model                                           |      |      |      |    |                                                             |  |  |

| Standardization of system level design language(SLDL)                     |      |      |      |    |                                                             |  |  |

| Simulation of SLD Language                                                |      |      |      |    |                                                             |  |  |

| Performance estimation in system level design                             |      |      |      | Í  |                                                             |  |  |

| (application soft, compiler, performance estimation of HW, optimization ) |      |      |      |    |                                                             |  |  |

| High speed prototyping                                                    |      |      |      |    |                                                             |  |  |

| Formal verification (Specification - System)                              |      |      |      |    |                                                             |  |  |

| HW/SW partition                                                           |      |      |      |    |                                                             |  |  |

| System level library (IP core, middle ware, etc. )                        |      |      |      |    |                                                             |  |  |

| Decision support of system level test strategy                            |      |      |      |    |                                                             |  |  |

| Tradeoff of analog/digital                                                |      |      |      |    |                                                             |  |  |

| [Architecture Design]                                                     |      |      |      |    |                                                             |  |  |

| Standardization of architecture model                                     |      |      |      |    |                                                             |  |  |

| Standardization of architecture description language                      |      |      |      |    |                                                             |  |  |

| Estimation in architecture level (area, delay, power,)                    |      |      |      |    |                                                             |  |  |

| Decision of RTL constraint                                                |      |      |      |    |                                                             |  |  |

| (area, timing, power, budgeting of floor plan )                           |      |      |      |    |                                                             |  |  |

| Formal verification (\$ystem - Architecture )                             |      |      |      |    |                                                             |  |  |

| Validation/Simulation                                                     |      |      |      |    |                                                             |  |  |

| Architecture synthesis                                                    |      |      |      |    |                                                             |  |  |

| Co-synthesis                                                              |      |      |      |    |                                                             |  |  |

| Decision support of architecture level test strategy                      |      |      |      |    |                                                             |  |  |

| (test method/area/length of test )                                        |      |      |      |    |                                                             |  |  |

| DFT in architecture level                                                 |      |      |      |    |                                                             |  |  |

$\square$  :trial use  $\square$  :preceding use  $\blacksquare$  :practical use

Cited from EIAJ/EDA Technology Roadmap Toward 2002

## Design Tools (1) by Universities and Research Centers

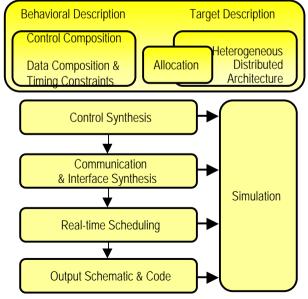

#### POLIS (UCB, U.S.A.)

·Co-design Environment for embedded system based on the CPU and DSP

Supporting functional design to prototyping

Architecture exploration by mapping behavior to architecture

•Accurate and high-level performance estimation using a fuzzy instruction set

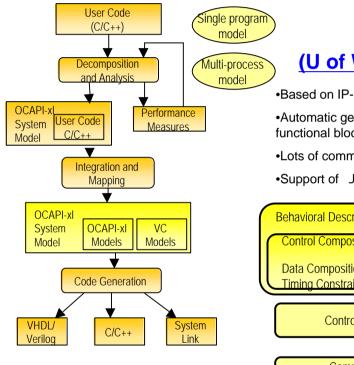

**OCAPI-xI (IMEC, Belgium)**

•C++ model which can describe HW and SW uniformly

•Optimal block partition using a performance analysis

Automatic generation of VHDL / Verilog-HDL / C

#### **IpChinook** (U of Washington, U.S.A.)

•Based on IP-based/Reused-Design methodology

•Automatic generation of control and I/F between functional blocks

- Lots of communication protocol libraries

- •Support of Java Pia C

© JEITA 2001 All rights reserved

# Design Tools (2)

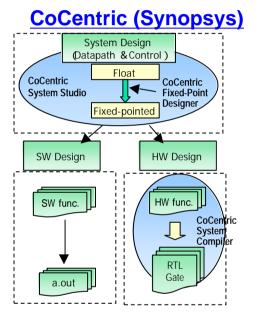

#### by Vendors

•Support HW side and co-verification of SOC Design

Conversion from float to fix-pointed

HW Synthesis from behavior (Verilog,VHDL)

Supporting SystemC

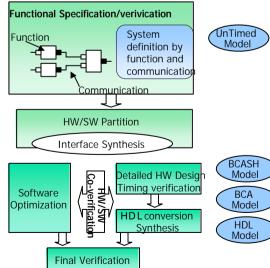

#### N2C (CoWare)

- •Supporting functional level to implementation

- •System Definition in Untimed, BCASH, BCA abstraction levels by original C-based language (CoWareC)

- •Communication refinement

- •Interface synthesis between HW and SW

- Supporting SystemC (in future)

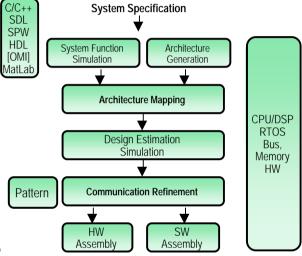

#### VCC(Cadence)

- •Architecture exploration by mapping function to architecture

- •Performance estimation using a fuzzy instruction set

- •Supporting IP reuse

- •Communication synthesis

- •Interface to implementation

### Summary of EDA Trend

- May be solved in near future...?

- Function Verification

- Architecture Mapping

- Performance Estimation

- Interface Synthesis

- HW/SW Co-Verification

- Unsolved Problems

- Function Partition

- High Speed Estimation

- Estimation of Area, Cost, and Power

- Standardized Description of system specification, constraints

- etc. . . .

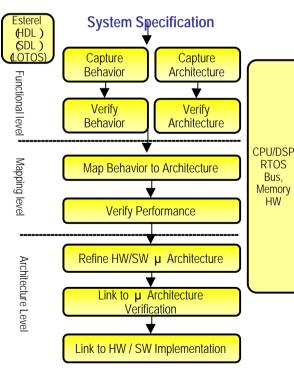

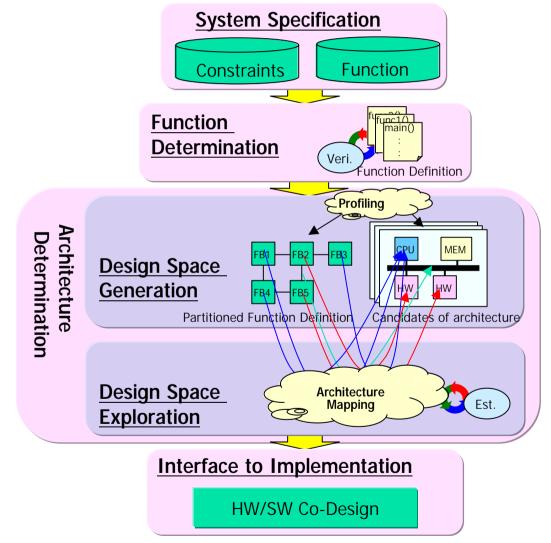

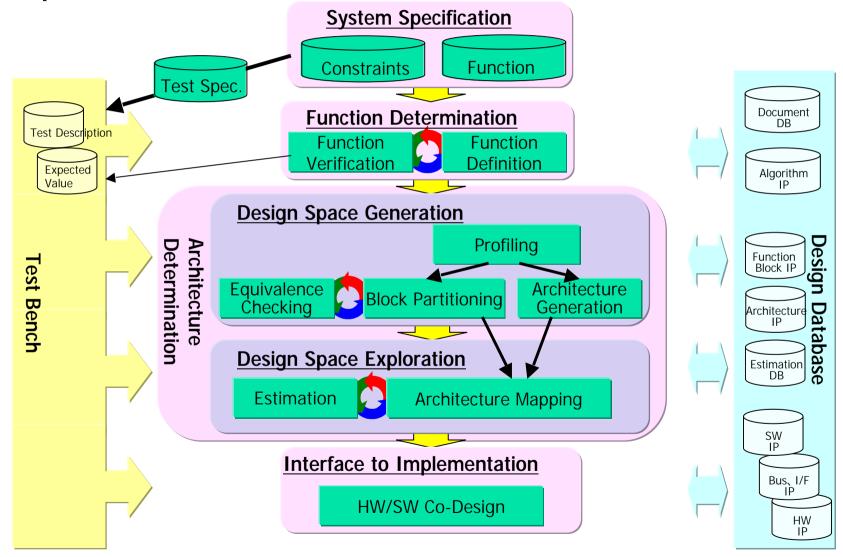

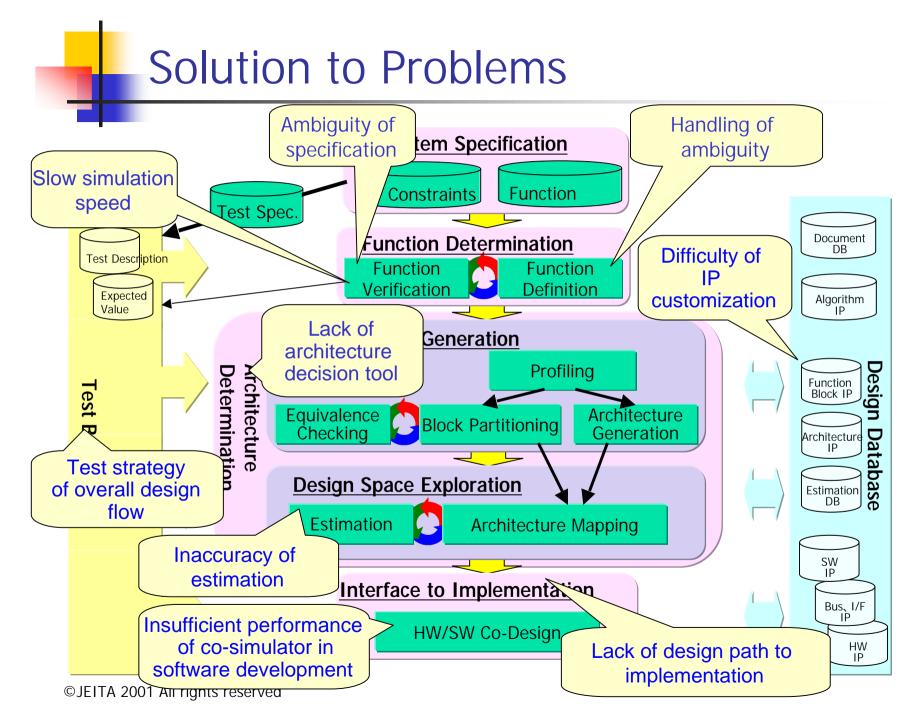

## Proposed Design Flow

©JEITA 2001 All rights reserved

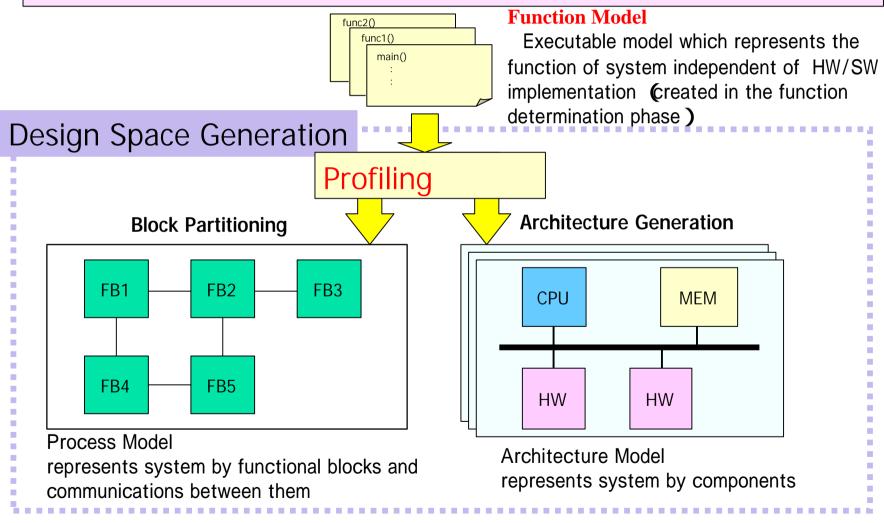

## **Design Space Generation**

Block partitioning and architecture generation from function model

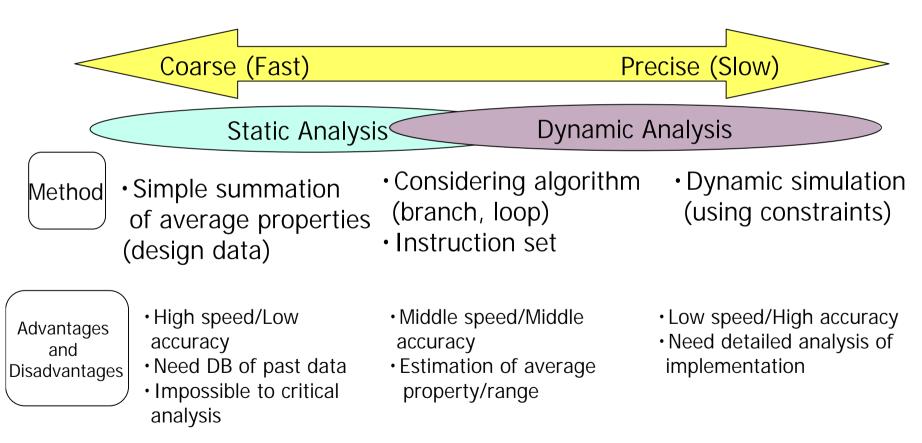

## Profiling

Analyze function models statically/dynamically and extract information for block partitioning and architecture generation

| Class                           | Information                                                                                                              | Usage (in design space generation)                                                                                              |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Number of<br>Variable<br>Access | <ul> <li>Number of read/write</li> <li>Access position</li> <li>Read-write distance</li> </ul>                           | <ul> <li>Choice of algorithm</li> <li>Decision of block candidates</li> <li>Selection of memory/register</li> </ul>             |

| Amount of<br>Data<br>Transfer   | <ul> <li>Number of <u>(bits)*(number of exec.)</u><br/>of read/write</li> <li>Amount of parameters</li> </ul>            | <ul> <li>Decision of partitioning units</li> <li>Decision of HW/SW partitioning</li> <li>Selection of comm. protocol</li> </ul> |

| Amount of<br>Calculation        | <ul> <li>•Execution count of lines</li> <li>•Execution count of blocks</li> <li>•Execution count of functions</li> </ul> | <ul> <li>Decision of partitioning units</li> <li>Performance estimation on<br/>HW/SW</li> </ul>                                 |

| Statistical<br>Analysis         | •Type and count of<br>arithmetic/control instructions                                                                    | <ul> <li>Choice of processor</li> <li>Refinement of instruction set</li> </ul>                                                  |

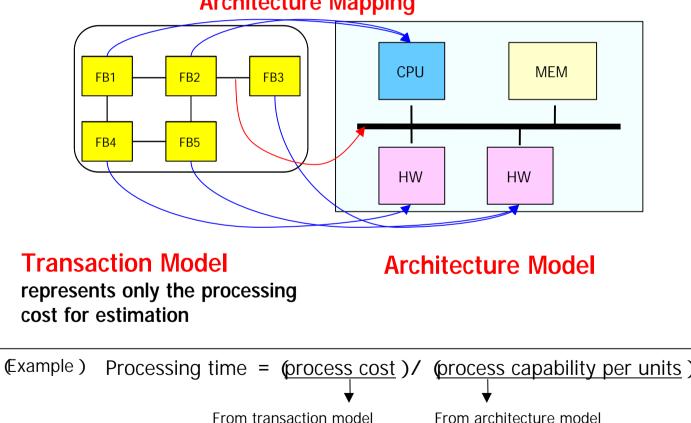

## **Design Space Exploration**

Mapping each functional block to a component and select the optimum architecture which satisfies constraints

#### **Architecture Mapping**

Tradeoff of transaction model

## Technology Map of Tools

|                                |                             | e verification is<br>rted by all tools                                        |       | N     | lo tool su | pport |       |       |

|--------------------------------|-----------------------------|-------------------------------------------------------------------------------|-------|-------|------------|-------|-------|-------|

| Design                         | Phase                       | Tech                                                                          | Tool1 | Tool2 | Tool3      | Tool4 | Tool5 | Tool6 |

| System Specification           |                             | Function<br>Constraints                                                       | ×     | ×     | ×          | ××    | ×     | ×     |

| Function Det                   | ermination                  | Function Definiti<br>Function Verificatio                                     |       |       |            |       |       |       |

|                                | Design Space<br>Generation  | Profiling<br>Block Partitioning<br>Architecture Generati<br>Equivalence Check | ×     | ×     | ×          | ×     |       |       |

|                                | Design Space<br>Exploration | Architecture Mapping<br>Performance Estimation                                |       |       |            |       |       | ×     |

| Interface to<br>Implementation | on                          | Interface Synthesi<br>HW/SW Co-D                                              | ×     |       | ×          |       |       |       |

| Test Bench                     |                             | Test Ben rate                                                                 |       | N     |            |       |       |       |

Some tools support this phase but speed/accuracy of the estimation is insufficient : automated by the tool

: tool has supporting function

: tool does not have supporting function

× : not covered by the tool

No tool supports the test bench generation

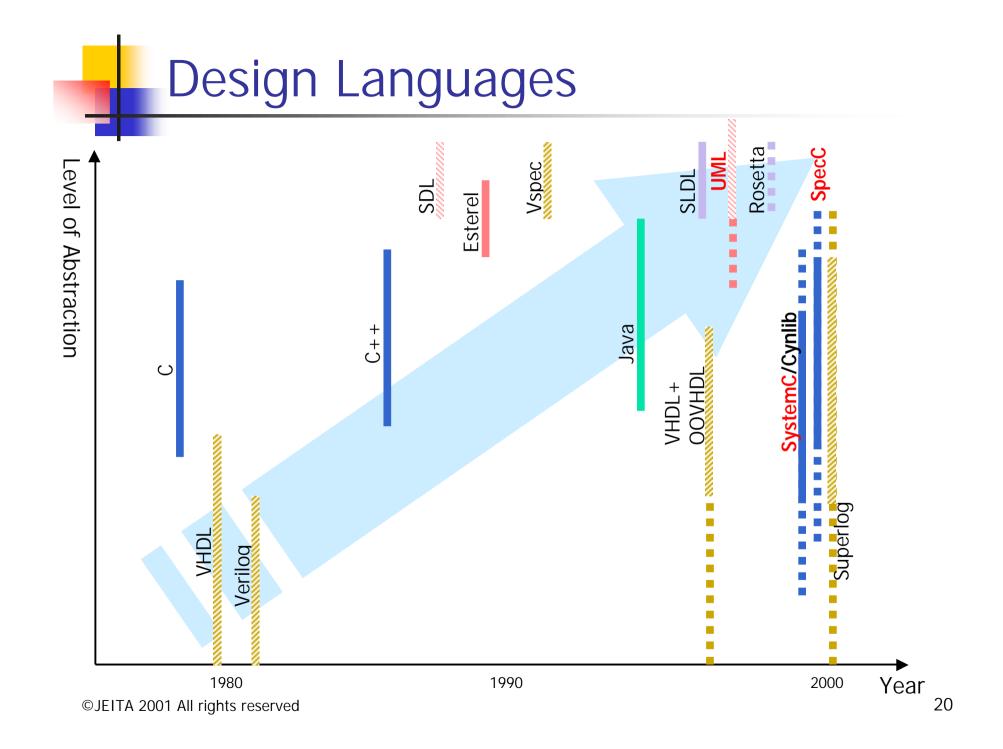

#### Investigation of System Level Design Languages

#### Background

- Important role for system level design flow

- Standardization activities (OSCI, STOC, Accellera)

#### Objectives

- Understand standardization activities (SystemC, SpecC, UML, etc. )

- Evaluation of the proposed design flow

- Feedback to standardization groups

## SystemC

- Background

- Proposed based on the technologies of Synopsys Inc., CoWare Inc., Frontier Design Inc. (Sept 1999)

- Features

- Representation from system level to HW/SW by adding dedicated class libraries, and without enhancing C/C++ grammar

- Availability of standard C/C++ development environment

- Less readability of description

- Developed from HW design using C/C++ to system level

- Easy to move from HDL environment

- Trends

- Open SystemC Initiative (OSCI) promotes standardization

- More than 70 of EDA vendors, IP vendors, semiconductor companies join to OSCI (Apr 2000)

# SpecC

- Background

- Developed by Prof. Gajski in UCI (1997)

- Features

- Unified description of HW/SW by enhancing ANSI-C grammar

- High readability

- Needs special tools and environment

- Clear design methodology which covers over system modeling to architecture determination

- Trends

- SpecC Technology Open Consortium (STOC) promotes the standardization

- System houses, embedded software tool vendors have strong interest

- Background

- Developed as modeling language for complicated large system

- Started the standardization since 1996 by OMG \*1

- Unification of existing object-oriented modeling methods

- Features

- Visual language with high modeling ability

- Visual and multi-viewed system modeling use case, class, component, layout, state chart, sequence, activity, collaboration

- Scheme for describing constraints

- Methodology of applying HW design is incomplete.

- Trends

- Wide use in business software

- Started to use in embedded software trial phase for HW design

<sup>1</sup> Object Modeling Group \*<sup>2</sup> Booch Method, OMT Method, OOSE Method

ID=Set 值=0

Class Diagram

## Evaluation Results

| Language                                                                                                                                                  | SystemC (v2.0)                                                     | SpecC (v1.0)                                                       | UML (v1.4)                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|

| System Specification<br>Function<br>Constraints                                                                                                           | ×<br>× not supported                                               | ×<br>× not supported                                               | visual description constraint language                       |

| Function Determination<br>Function Definition<br>Function Verification<br>Architecture Determination<br>Profiling<br>Block Partition<br>Equivalence Check | O less readability<br>available C++ env.                           | clear methodology<br>tool environment<br>unified HW/SW desc.       | only for SW<br>only state chart<br>× not supported<br>×<br>× |

| Architecture Generation<br>Architecture Mapping<br>Estimation                                                                                             | only structure<br>transaction model NG<br>insufficient methodology | only structure<br>transaction model NG<br>insufficient methodology | ×<br>×<br>′ ×                                                |

| Interface to Implementation<br>HW/SW Co-Design                                                                                                            | support until RTL                                                  | planned to support<br>Accellera's RTL model                        | × not supported                                              |

| Test Bench Generation<br>IP Design                                                                                                                        | 0                                                                  | 0                                                                  | only specification                                           |

©JEITA 2001 All rights reserved

#### Summary of System Level Design Languages

- SystemC

- Representation from system level to HW/SW by adding dedicated class libraries and without enhancing C/C++ grammar

- Need to clarify the methodology

- Strong support for implementation, but need to consider the architecture generation and the estimation

- SpecC

- Unified description of HW/SW by enhancing ANSI-C grammar

- A key to prevalence is to arrange special design environment to implementation

- Methodology for system modeling exists, but weak for the architecture generation and later stages

- UML

- Large ability of function/constraint description by visual modeling

- Need to consider design phases after architecture design