主査 NECエレクトロニクス 黒坂 均 |

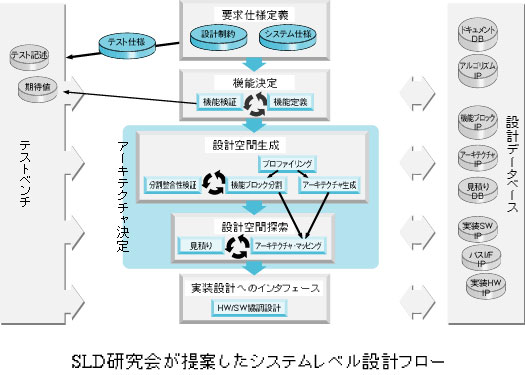

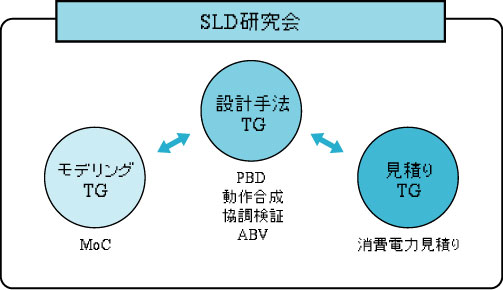

| ■概要 大規模化、複雑化するシステムLSIを効率的に開発することは、従来の設計手法では難しくなってきている。実際、SLD研究会が実施したアンケート結果からも設計のボトルネックの6割を、時間と人の不足、EDAツールの能力不足、設計対象の複雑化などが占めており、現状の設計手法についての問題が指摘されている。この状況を打開するために、例えば、ハードウェア設計においては、RTL設計から動作レベル設計へ設計抽象度を上げるといったパラダイムシフトが必要となってきている。一方で、SystemC、SpecCをはじめとするシステムレベル設計言語の普及活動や、LSIメーカなどによるC言語ベース設計の成功事例報告などにより、システムレベル設計が現実のものとして注目されるようになってきた。このような動きの中、JEITA参加企業をはじめとする日本企業は、システムレベル設計手法の効果を享受することで設計競争力を向上させることができると考えている。SLD研究会では設計生産性向上に貢献することを目的に、最新のシステムレベル設計に関する動向を世に伝え、設計者の要求をシステムレベル設計に関連する標準化活動などに反映させる活動を行っている。 ■これまでの成果 SLD研究会は1998年11月に発足以来、以下の活動を行ってきた。 ・動向調査 SystemC、 SpecC、 UMLを主に、C言語ベースやHDLベースなどの各種システムレベル設計言語の調査、産学で提案されているシステムレベル設計ツールの調査を行った。2001年度はシステムレベル設計に関して研究している機関(IMEC, GSRC, STARC)、標準化活動を行っている団体(Accellera, VSIA, Sydic Telecom)について内容を調査し、技術マップとしてまとめた。 ・ニーズ分析と設計フローの提案 1998年度から1999年度にかけて実施した設計者懇談会および設計者アンケートの結果を分析し、ニーズを満たすシステムレベル設計フローを提案した。  ・システムレベル設計環境検討 システムレベル設計フローをニーズ/シーズの両方から改善し、主な言語や設計ツールでの適用化検討を行った。提案についてはEDAベンダのツールにも反映されている。 ・対外発信 活動成果について「EDAアニュアルレポート1998、1999、2000、2001」(JEITA発行)、「システムレベル設計手法の提案とシステムレベル設計言語の適用化検討」(2001年JEITA発行)でまとめ、また、琵琶湖WSでの発表(2000年11月)を行った。この成果はSASIMI2001でも参照されている。また、主要な活動成果を英文化し、アニュアルレポートとホームページに掲載した。 ■2002年度のタスクグループ活動 本年度はこれまでの活動成果を踏まえてシステムレベル設計の3つの課題に着目し、タスクグループ(TG)に分かれて詳細な検討を行っている。  設計手法TG: 研究会が提案した設計フローをより現実的なものにするために、プラットフォームベース設計(PBD)を前提とした動作合成、協調検証、アサーションベース検証(ABV)の既存技術について調査し、改善提案および利用提案を行う。 モデリングTG: 設計効率と設計品質の向上を図ることを目的として、システム設計で用いられる計算モデル(Model of Computation、以下MoC) について調査し、各MoCの特徴比較を行う。その結果をもとに、各設計フェーズおよびアプリケーションに適したMoCの検討を行う。 見積りTG: SoCの低消費電力化設計は、レイアウト・回路・プロセスレベルでの技術が中心となっているのが現状であり、システムレベルでの低消費電力化設計技術は未成熟である。本TGでは、システムレベル設計における消費電力見積り技術の調査と、実用性・実効性の観点での評価と改善提案を行う。 (参加メンバ) 17社19名、他客員3名(主査:黒坂 均/NECエレクトロニクス) (研究会URL) http://eda.ics.es.osaka-u.ac.jp/jeita/eda/english/project/sld/index.html |

JEITA/EDA技術専門委員会ホームページに戻る |