# **JEITA**

# EDAアニュアルレポート 2008

Annual Report on Electronic Design Automation

- 65nmから45nmテクノロジ世代のEDA技術の進展に向けて -

2009年5月発行

作 成

EDA技術専門委員会

EDA Technical Committee

発 行

社団法人 電子情報技術産業協会 Japan Electronics and Information Technology Industries Association

# 【巻頭言】

# 「65nmから45nmテクノロジ世代のEDA技術の進展に向けて」

EDA技術専門委員会 2008年度 委員長 山田節

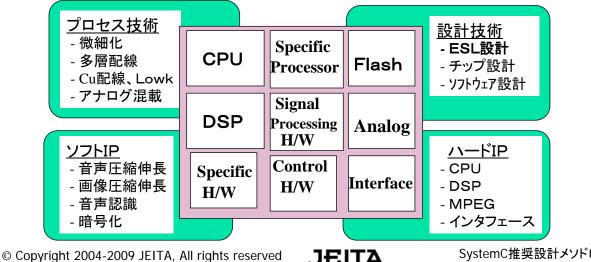

現在および近い将来のユビキタス社会を構築していく上で、基幹となる半導体産業への期待が高まっている。なかでも、半導体の設計に関する技術は、LSIの高密度化、高集積化、高性能化、低消費電力化の要求を支える重要な役割を担っており、より一層の技術向上を図る必要がある。

半導体加工の超微細化の進展に伴い、設計上流では超大規模システム LSI の機能・論理の設計・検証問題、設計下流では SI(Signal Integrity) や DFM(Design For Manufacturing)問題、そしてこれをつなぐインプリメンテーションの難易度の飛躍的増大への対応である。

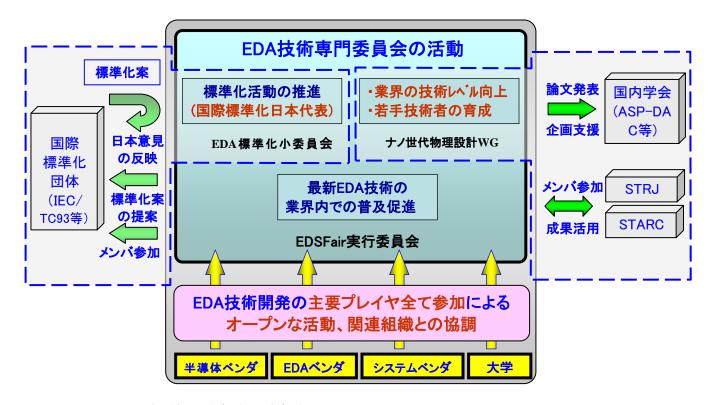

EDA 技術専門委員会は、電子情報技術産業協会(JEITA)における業界活動組織の一つとして、電子機器の設計自動化(EDA: Electronic Design Automation)に関わる様々な活動を行っている。特に、電子機器の機能・性能を決定するシステム LSI 設計技術に関して、以下の 3 つの領域を推進している。

第1の活動の領域は、システム LSI 設計技術に関する調査・検討と課題解決手法の提案である。本年度は、製造ばらつきに起因するリーク電流変動の低減法などのプロセス微細化に伴う設計課題とその課題解決手法を、ナノ世代物理設計ワーキンググループが検討を行った。

第2の活動領域は、EDA技術に関する標準化活動と関連機関、団体への協力と貢献である。IEC、IEEE 等の国際的な標準化活動に対し EDA 標準化小委員会を中心に、標準化提案の検証、技術提案・交流会議などを行なっている。設計記述言語 SystemC および SystemVerilog の IEEE 標準化では、本委員会の各ワーキンググループが、2005 年末の標準化に貢献し、その後も両標準の普及推進活動と、追加標仕様の検討、提案を行っている。二つの標準化グループが存在し混迷している Power Format は、PowerFormat ワーキンググループが業界としての検討を行い、IEEE.p1801 への投票を行った。また、EDA 標準化小委員会は電子情報通信学会内の IEC/TC93 国内委員会/WG2(ハードウェア設計記述言語)としての標準化活動も行っており、2008 年 11 月には IEC/TC93 国際会議(シンガポール)に参加し、国際標準化の課題を議論してきた。

最後に、第3の活動領域は、EDA技術および標準化の普及、推進のためのイベント開催、支援である。本年度も、2009年1月にパシフィコ横浜にてEDSFair2009(Electronic Design and Solution Fair 2009)を開催した。EDSFair は、電子機器の設計技術に関する、国内唯一の総合的な展示会であり、時開催のFPGAコンファレンスおよびシステム・デザイン・フォーラム 2009と合わせ、特設ステージでの当委員会企画イベントも含めて積極的・精力的に、企画、出展者誘致、来場者誘致活動を行った。その結果、最新のEDA技術と関連情報との出会いの場として、LSI設計者・電子機器設計者をはじめとした1万人に近い方々に参加頂いた。

次の図でこれらの委員会活動と関係する団体の関係を示す。

IEC/TC93 : 国際電気標準会議/設計自動化 ASP-DAC : Asia South Pacific-Design Automation

Conference

STRJ : 半導体技術ロードマップ委員会 STARC : 半導体理工学研究センター

#### 図-1 EDA技術専門委員会と関連組織との関係

EDA 技術専門委員会は、上図の関連組織・団体との密な連携のもと、技術検討、標準化、そしてそれらの普及促進という3つの活動領域の活動を通じ、65nm から45nm テクノロジー世代の「システム・オン・チップ時代」の電子情報機器業界に対し、さらには地球温暖化などの世界規模での課題に対し、設計技術の面で貢献し、「システム・オン・チップ時代」がもたらす産業界の変革を乗り越えて、日本の電子情報機器業界の発展に寄与すべく、本年度21社約60名の業界各社・有志メンバーの参画で運営してきた。

「システム・オン・チップ時代」に入り、半導体および電子機器が切り拓く素晴らしい未来が今後も 広がることを確信しつつ、2009年度も積極的な活動を展開していきたい。

本冊子「EDAアニュアルレポート2008」は、EDA技術専門委員会の2008年度年次報告として、上記3つの活動領域について、活動成果をまとめたものである。

Webにも各種報告を掲載しているので、ご覧いただきたい。

(http://eda.ics.es.osaka-u.ac.jp/jeita/eda/index-jp.html)

# 2008 年度 JEITA/EDA 技術専門委員会 委員一覧

| 委員長 | 山田節 | 三洋電機㈱                      | デジタル技術研究所    |

|-----|-----|----------------------------|--------------|

| 女貝以 |     | — 什 电 / <b>茂</b> / / / / / | / イン/四次附列元/7 |

担当課長(LSI設計技術担当)

副委員長 太田 光保 パナソニック㈱ セミコンダクター社

システムLSI事業本部

商品開発センター

設計第三開発グループ 参事

副委員長 江田 努 ローム㈱ YTC開発システムユニット

LSI企画推進G 次席技術員

監事 齋藤 茂美 ソニー㈱ 半導体事業本部 設計基盤技術部門

企画部第1課 統括課長

幹事 吉田 正昭 NECエレクトロニクス㈱ 基盤技術開発本部

設計技術開発部

シニアプロフェッショナル

幹事 西本 猛史 シャープ㈱ 電子デバイス事業本部

NB事業化推進センター

NBプロジェクトチーム 副参事

幹事 熊谷 敬 セイコーエプソン㈱ 半導体事業部 I C基盤技術部

部長

幹事 南 文裕 ㈱東芝 セミコンダクター社

システムLSI設計技術部

設計メソドロジ技術開発 担当主査

幹事 河村 薫 富士通マイクロエレクトロニクス㈱

テクノロジ開発統括部

主席部長

幹事 秋山 俊恭 ㈱ルネサステクノロジ 製品技術本部 設計技術統括部

副統括部長

| 委員 | 長野 義史 | ㈱エッチ・ディー・ラボ                 | 代表取締役社長                                                        |

|----|-------|-----------------------------|----------------------------------------------------------------|

| 委員 | 川原 常盛 | コーウェア(株)                    | 取締役 営業技術本部長                                                    |

| 委員 | 下出 隆文 | 三洋半導体㈱                      | SS事業本部 SS事業推進統括部<br>設計技術部 課長                                   |

| 委員 | 山城 治  | ㈱ジーダット                      | 取締役                                                            |

| 委員 | 野坂 啓介 | ㈱図研                         | SoC事業部イノベーション営業部                                               |

| 委員 | 平尾 栄二 | 凸版印刷㈱                       | 半導体ソリューション事業本部<br>事業企画部 部長                                     |

| 委員 | 安井 孝史 | 日本ケイデンス・デザイン・               | システムズ社<br>TFO Director                                         |

| 委員 | 飯島 一彦 | 日本シノプシス㈱                    | 技術本部 本部長                                                       |

| 委員 | 牧 克眞  | マグマ・デザイン・オートメ               | ニーション(株)<br>営業ディレクタ                                            |

|    |       |                             |                                                                |

| 委員 | 瀬谷 和宏 | 丸紅情報システムズ㈱                  | 製造ソリューション事業本部<br>事業本部長補佐                                       |

| 委員 |       | 丸紅情報システムズ㈱<br>メンター・グラフィックス・ | 事業本部長補佐                                                        |

|    |       | メンター・グラフィックス・               | 事業本部長補佐 ジャパン(株) テクニカルセールス部 テクニカルディレクター 電子デバイスカンパニー 画像LSI開発センター |

| 委員 | 三橋明城男 | メンター・グラフィックス・<br>(株)リコー     | 事業本部長補佐<br>ジャパン(株)<br>テクニカルセールス部<br>テクニカルディレクター<br>電子デバイスカンパニー |

特別委員 小島 智 NECシステムテクノロジー㈱

PF統括本部 CWB事業推進室

テクニカルマーケティング

ディレクター

特別委員 浜口加寿美 パナソニック㈱ セミコンダクター社

システムLSI事業本部

商品開発センター

設計第三開発グループ

チームリーダー

特別委員 中森 勉 富士通マイクロエレクトロニクス㈱

テクノロジ開発統括部

第一設計技術部

プロジェクト課長

特別委員 長谷川 隆 富士通マイクロエレクトロニクス㈱

共通技術本部 設計共通技術統括部

第1設計部 部長

特別委員 金本 俊幾 ㈱ルネサステクノロジ 製品技術本部 設計技術統括部

S I P・アナログE D A 技術開発部

物理検証技術開発グループ主任技師

客員 神戸 尚志 近畿大学 理工学部 電気電子工学科

教授

客員 今井 正治 大阪大学 大学院 情報科学研究科

情報システム工学専攻 教授

客員 岡村 芳雄 ㈱半導体理工学研究センター

執行役員・開発第2部長

客員 若林 一敏 日本電気㈱ 中央研究所

ビジネスイノベーションセンター

EDA開発センター研究部長

# 略語一覧

# [1] 団体・組織の名称

| Accellera |                                                                     |

|-----------|---------------------------------------------------------------------|

|           | VIとOVIを統合した、設計記述言語の標準化に関連する活動機関                                     |

| ANSI      | American National Standards Institute                               |

|           | 米国の標準化国家機関                                                          |

| ASP - DAC | Asia and South Pacific Design Automation Conference                 |

|           | アジア・太平洋地域でのEDA関連の国際学会(1995年に始まる)                                    |

| CENELEC   | European Committee for Electrotechnical Standardization             |

|           | EC(欧州委員会)の電気電子分野に関する標準化機関                                           |

| DAC       | Design Automation Conference                                        |

|           | 米国で行われるEDA関連の国際学会                                                   |

| DASC      | Design Automation Standardization Committee                         |

|           | IEEEの下部組織で設計自動化に関する標準化委員会                                           |

| ECSI      | European Electronic Chips & Systems design Initiative               |

|           | 欧州の設計自動化に関する標準化機関                                                   |

| EDIF Div. | Electronic Design Interchange Format Division                       |

|           | EIAの下部組織で電子系の惜報データ交換規格の検討機関                                         |

| EIA       | Electronic Industries Alliance                                      |

|           | 米国の電子業界団体(AssociationをAllianceに改称)                                  |

| JEITA     | Japan Electronics and Information Technology Industries Association |

|           | 社団法人電子情報技術産業協会(電子業界団体)                                              |

| ICCAD     | International Conference on Computer Aided Design                   |

|           | CADに関する国際学会                                                         |

| IEC       | International Electrotechnical Commission                           |

|           | 電気電子分野に関する国際標準化機関                                                   |

| IEEE      | Institute of Electrical and Electronics Engineers,Inc.              |

|           | 米国の電気電子分野の国際的な学会組織                                                  |

| IPC       | Institute for Interconnecting and                                   |

|           | Packaging Electronic Circuits Industry Association                  |

|           | 米国のプリント回路に関する業界組織                                                   |

| ISO       | International Organization for Standardization                      |

国際標準化機関

IVC International Verilog Conference

OVIが主催するVerilog HDL国際学会

JPCA Japan Printed Circuit Association

社団法人日本プリント回路工業会

OSCI Open SystemC Initiative

SystemC の標準化団体

OVI Open Verilog International

Verilog - HDLに関連する技術の標準化と普及推進組織

SEMATECH Semiconductor Manufacturing Technology Initiative (Consortium)

半導体技術を向上するために始まった米国の官民プロジェクト

Si2 Silicon Integration Initiative

設計環境の整備促進を支援する米国の非営利法人(旧CFI)

VASG VHDL Analysis and Standards Group

DASC傘下のVHDL標準化に関するワーキンググループ

VITAL VHDL Initiative Toward ASIC Libraries

VHDLライブラリ標準化団体

VSIA Virtual Socket Interface Alliance

LSIの機能ブロックのI/F標準化を目指している業界団体

# [2] 標準化・規格に関する技術用語

ALF Advanced Library Format

OVIで検討されたIPをも含むASICライブラリのフォーマット

ALR ASIC Library Representation

ASICライブラリ表現

CALS Computer Aided Logistics Support (1985)

Commerce At Light Speed (1995)

CHDS Chip Hierarchical Design System

SEMATECHが要求仕様を作成した0.25-0.18um世代設計システム

CHDStd Chip Hierarchical Design System technical data

CHDSで使用するデータモデルの標準化

DCL Delay Calculation Language

遅延計算のための記述言語

DPCS Delay and Power Calculation System

IEEE1481として標準化推進されている遅延と消費電力の計算機

構仕様

EDI Electronic Data Interchange

電子データ交換

EDIF Electronic Design Interchange Format

EIAの下部組織で検討されている電子系の情報データ交換規格

ESPUT European Strategic Program for Research and

Development in Information Technology

欧州情報技術研究開発戦略計画

HDL Hardware Description Language

ハードウェア記述言語

IP Intellectual Property

流通/再利用可能なLSI設計資産(本来は知的財産権の意)

JIS Japanese Industrial Standard

日本工業規格

SDF Standard Delay Format

遅延時間を表記するフォーマット

SLDL System Level Design Language

システム仕様記述言語

STEP Standard for the Exchange of Product Model Data

CADの製品データ交換のための国際規格

VHDL VHSIC (Very High Speed Integrated Circuit)

Hardware Description Language

IEEE1076仕様に基づくハードウェア記述言語

VHDL-AMS VHDL-Analog and Mixed-Signal (Extensions)

DASCの中で進められているVHDLのアナログ及びミックストシ

グナルシステムへの拡張

1. EDA技術専門委員会の活動

# 1.1 2008 年度 JEITA/EDA 技術専門委員会 事業計画

**委員会の名称** EDA 技術専門委員会(Electronic Design Automation Technical Committee)

委員会の目的 EDA に関連する技術およびその標準化の動向を調査し、その発展、推進を図り、

もって国内外の関係業界の発展に寄与する

**委員会の構成** 会員会社/委員 21 社/24 名

特別委員6名客員4名

委員会の役員

委員長: 三洋電機 山田 節

副委員長(正): パナソニック

副委員長 (代行):ローム江田 努監事:ソニー齋藤 茂美

下部組織の役員

EDA 標準化小委員会 主査 パナソニック 太田 光保

SystemC WG 主査 富士通マイクロエレクトロニクス 長谷川 隆

SystemVerilogWG 主査 パナソニック 浜口 加寿美

Power Format WG 主査 富士通マイクロエレクトロニクス 中森 勉

ナノ世代物理設計 WG主査 ルネサステクノロジ 金本 俊幾

EDSFair 実行委員会 委員長 富士通マイクロエレクトロニクス 河村 薫 EDSFair 企画 WG 主査 ソニー 齋藤 茂美

SDF WG 主査 ローム 江田 努

<方針>

1.情報収集力の強化(PowerFormat 取組

みの反省)

IEEE-SA の加入継続

IEEE/DASC への加入検討

国際会議(TC93, DASC)への積極的参

加と国内開催(WG2)

標準化団体との定期的な会議開催

2.委員会活動の活性化

委員会を主体にした運営 EDSFair に 係 る JESA,ASP-DAC,FPGA/PLD

Conf.

などとの連携を再構築とイベント

運営の見直し

HP を活用したドキュメントの電子

化(情報共有強化) ペーパーレス化の推進

3.委員会の継続的発展

新公益法人制度への対応

予算の最適運用

#### EDA 技術専門委員会メンバと担当 (敬称略)

委員長: 三洋電機 山田 節 EDSFair/ASP-DAC 小委員会 主査、ASP-DAC 支援 副委員長:パナソニック 太田 光保 EDA 標準化小委員会 主査 (IEC/TC93 WG2 国内 主査)

国際標準化対応支援委員会 委員 (IEC/TC93 担当)

副委員長:ローム 江田 努 SDF WG 主査、EDA標準化小委員会 副主査、内規改訂、

EDSFair 実行委員、ASP-DAC2009 Designer's Forum

委員

監事:ソニー 齋藤 茂美 EDSFair 企画 WG 主査、EDSFair 実行委員

幹事: NEC エレクトロニクス 吉田 正昭 ホームページ、メールシステム、予算実績管理

幹事:シャープ 西本 猛史 ASP-DAC2009 Designer's Forum 委員

南 文裕

河村 薫

秋山 俊恭

EDSFair 企画 WG 委員

幹事:セイコーエプソン 熊谷 敬 アニュアルレポート、EDSFair 企画 WG 委員

システム·デザイン·フォーラム WG 委員

EDSFair 企画 WG 委員

EDSFair 実行委員長、SDF WG 委員

EDSFair 実行委員、広報パンフレット

委員:エッチ・ディー・ラボ

幹事:富士通マイクロエレクトロニクス

幹事:ルネサステクノロジ

委員:コーウェア 委員:三洋半導体

委員:ジーダット

委員:図研

幹事:東芝

委員:凸版印刷

委員:日本ケイデンス・デザイン・システムスで社

委員:日本シノプシス

委員:マグマ・デザイン・オートメーション 委員:マグマ・デザイン・オートメーション 長野 義史

川原 常盛

下出 隆文

山城 治

野坂 啓介

平尾 栄二

安井 孝史

飯島 一彦

船津 英世

牧 克眞

委員:丸紅情報システムズ 瀬谷 和宏

委員:メンター・グラフィックス・ジャパン 三橋 明城男 EDSFair 企画 WG 委員

委員: リコー

前野 酉治

委員: ローム

山本 一郎

特別委員:三洋半導体 黒川 敦 EDA 用語辞典担当

特別委員: NEC システムテクノロジー 小島 智 IEC/TC93/WG2 コンベナ、EDA 標準化小委員会 副主査

国際標準化担当

特別委員:パナソニック 浜口 加寿美 SystemVerilog WG 主査特別委員:富士通マイクロエレクトロニクス中森 勉 Power Format WG 主査特別委員:富士通マイクロエレクトロニクス長谷川 隆 SystemC WG 主査

特別委員:ルネサステクノロジ金本 俊幾 ナノ世代物理設計 WG 主査

客員:近畿大学神戸 尚志IEC/TC93 国内委員長、元委員長客員:大阪大学今井 正治上流設計識者、ASP-DAC リエゾン

客員: STARC 岡村 芳雄 元委員長

客員: 日本電気 若林 一敏 ASP-DAC リエゾン

事務局: JEITA

古川 昇

事務局: JEITA

岩渕 幸吾

# 活動計画の概要 <別紙-1 参照>

委員会の予算 会費 230,000 円 \* 22 社 =5,060,000 円

委員会の開催 年6回程度(予定日: 別紙-2 参照)

必要に応じて幹事会を開催する

担当事務局 JEITA/電子デバイス部

#### <別紙 - 1>

#### 活動計画の概要

### 1. EDA 技術の動向 & 関連情報の調査検討、課題解決への提案

- (1) 小委員会及び WG による技術動向とニーズ調査

- ・最先端テクノロジ : ナノ世代物理設計 WG

- ・設計言語 : EDA 標準化小委員会

- (2) 関連機関、団体、キーパーソン等との合同会議、意見交換、交流

- · STARC, STRJ 等

- (3) 国内外の学会,研究会,イベントへの参加と連携

- ・ASP-DAC2009, DAC2008, IEICE, 軽井沢ワークショップ

# 2. EDA に関する標準化活動への貢献と関連機関、団体への対応

- (1) EDA 設計言語およびモデル標準化のための技術的検討と提案

- ・SystemC, SystemVerilog, PowerFormat を継続

- ・Verilog-HDL,VHDL,A-HDL などは、EDA 標準化小委員会で必要に応じて対応

- (2) 国際的な関連機関、団体への参画・連携と標準化活動への協力

- ・IEC/TC93 国際会議(11 月@シンガポール)への参加

- ・WG2 会議を開催(6月@DAC(US), 1月@EDSFair(Yokohama), 2月@DVcon(US))

- ・IEEE/DASC,IEEE-SA, OSCI, Accellera, Si2 等との連携を強化

- ・IEEE/DASC への加入を検討

### 3. EDA 技術および標準化の普及推進のためのイベント実施、支援

- (1) 「EDSFair2009」(横浜)

- ・日本エレクトロニクスショー協会へ運営委託

- ・半導体部会/技術委員会を活用した各社への依頼とアナウンス

- ・ASP-DAC, FPGA/PLD Conference との連携と新企画の提案

- ・特設ステージの継続実施

- (2) 各種ワークショップ、講演会の開催

- ・「システム・デザイン・フォーラム 2009」を EDSFair2009 と同時開催

- (3) 「ASP-DAC2009」 (Yokohama)

- ・Designer's Forum との連携

#### 4. 委員会活動の広報

- (1) 広報パンフレットの配布@EDSFair2009

- (2) アニュアルレポートの発行(下記 HP でも公開)

- (3) WWW ホームページの公開

- (4) 活動成果の発表

- ・システムデザインフォーラム : 標準化活動

- ・学会での公演/学術論文 : ナノ世代

# <別紙 - 2>

# 2008 年度 JEITA/EDA 技術専門委員会 会合予定

| 年/月     | 技術専門委員会                                                                                                                                 | 懇親会 | 関連イベント                                                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------|

| 2008/4  | 4/25(金) (東京地区) 議事録 メンター<br>・08 年度事業計画説明、承認<br>・08 年度小委員会/WG 計画説明、承認<br>・07 年度会計収支と 08 年度会計予算説明、<br>承認<br>・07 年度版アニュアルレポート作成状況報告         | 0   | ・DATE2007(4/16-4/19) @ Nice<br>・軽井沢 WS (4/21-22) @軽井沢                     |

| 2008/5  |                                                                                                                                         |     |                                                                           |

| 2008/6  | 6/20(金) (東京地区) 議事録 図研<br>・小委員会/WG 進捗報告<br>・半導体部会/半導体技術委員会報告内容説明<br>・委員名簿更新内容確認<br>・予算消費状況                                               |     | • DAC2008 (6/8-6/13) @Anaheim,<br>California                              |

| 2008/7  |                                                                                                                                         |     | ・STARC Forum&Symp. (7/16-17)<br>@新横浜                                      |

| 2008/8  |                                                                                                                                         |     | ・DA シンポジウム 2008 (8/26-27)<br>@浜松                                          |

| 2008/9  | 9/19(金) (関西地区) 議事録 コーウェア<br>・小委員会/WG 進捗報告<br>・半導体部会/半導体技術委員会報告内容説明<br>・予算消費状況                                                           |     | ・TC93 国際会議 (11 月)<br>@シンガポール                                              |

| 2008/10 |                                                                                                                                         |     |                                                                           |

| 2008/11 | 11/14(金) (東京地区) 議事録 エッチ・ディ・・ラボ・小委員会/WG 進捗報告・半導体部会/半導体技術委員会報告内容説明・予算消費状況・EDSFair 用パンフレット作成手順説明                                           |     | ・ICCAD2008 (11/10-13)<br>@San Jose, California<br>・デザインガイア(11/17-19) @北九州 |

| 2008/12 |                                                                                                                                         |     |                                                                           |

| 2009/1  | 1/14(水) (東京地区) 議事録 マグマ・小委員会/WG 進捗報告・半導体部会/半導体技術委員会報告内容説明・09 年度体制協議・EDSFair 用パンフレット内容確認・アニュアルレポート作成分担・手順説明・予算消費状況                        |     | ・ASP-DAC2009 (1/19-21)<br>@Yokohama<br>・EDSFair2009 (1/22-23) @横浜         |

| 2009/2  |                                                                                                                                         |     |                                                                           |

| 2009/3  | 3/19(木) (関西地区) 議事録 沖<br>・半導体部会/半導体技術委員会報告内容説明<br>・08 年度小委員会/WG の年間活動報告<br>・08 年度予算消費状況<br>・09 年度事業計画説明<br>・09 年度プロジェクト/研究会の年間活動計画<br>説明 | 0   | ・SASIMI2009 (3/9-10) @沖縄<br>・DATE2009 (4/20-24)@ Nice, 仏                  |

### 1.2 2008 年度 JEITA/EDA 技術専門委員会ホームページ

#### 1.2.1 目的

電子情報技術産業協会(JEITA)の EDA 技術専門委員会の活動状況を公開し、EDA 技術の標準 化や技術調査に関するご理解とご協力をいただくことを目的とする。

#### 1.2.2 ホームページの詳細

2006 年度よりホームページを一新し、よりわかりやすく、また、欲しい情報に簡易にアクセスできるような構成に変更を行った。ホームページは日本語版の他、英語版も用意し海外からの利用者の利便性を考慮している。日本語版、英語版の切り替えは簡単にできるように構成されている。

#### (1) URL: http://eda.ics.es.osaka-u.ac.jp/jeita/eda/

大阪大学のご協力を頂き、大阪大学のサーバーにホームページを設置させていただいている。またデータの更新など、メンテナンスについてもご協力を頂いている。

(2) エントリーページの構成

日本語版、英語版はそれぞれ次のエントリーで構成されている。

日本語版: 英語版:

委員会の紹介 Introduction of a committee

委員会活動 Committee activity 公開資料ライブラリ Open data library

イベント・関連機関 Event・A related organization

お問い合わせ Inquiry サイトマップ Site map

#### (3) 委員会の紹介/Introduction of a committee

委員長挨拶、活動と成果、メンバーをサブエントリとする。本委員会の概要、前年度の活動内容・成果、本年度の活動計画、委員会メンバーを紹介している。

# (4) 委員会活動/ Committee activity

下記の研究会・小委員会等の活動状況を紹介している。

- EDA 標準化小委員会 (EDA 標準化小委員会の他、System WG、System Verilog WG、 PowerFormat WG の活動が紹介されている)

- ・ ナノ世代物理設計 WG

- · EDSFair 実行委員会

## (5) 公開資料ライブラリ/ Open data library

「公開資料ライブラリ」のページでは、EDA 技術専門委員会内の各委員会の活動報告や各委員からの発表資料等を適宜掲載している。主な掲載資料を以下に示す。なお、英語版も日本語版と同一の日本語資料を掲載している。

- ・ EDA 技術専門委員会(過去のアニュアルレポート)

- ・ EDA 標準化小委員会(IEEE-SA セミナー、Power Format 比較表など)

- ・ ナノ世代物理設計 WG (過去の資料)

- ・ EDSFair 実行委員会(システムデザインフォーラムの紹介)

- システムレベル設計研究会(旧サイトへのリンク)

- ・ その他(過去の委員会活動報告)

- (6) イベント・関連機関/ Event・A related organization

関連の会議としては、次の関係の深い EDA 関連技術委員会の紹介が行われている。

- · IEEE/DASC (電気電子学会/設計自動化標準化委員会)

- ・ IEC/TC93 (国際電気標準化会議/デザインオートメーション標準化技術委員会)

また、関連機関として本委員会に関連のある 17 機関の紹介があり、さらにそれぞれのホームページへのリンクが行われている。

- 14 -

# 1.3 2008 年度 JEITA/EDA 技術専門委員会 年間実績·予定表

| 月       |                       | EDA 技術専門委員会                          |

|---------|-----------------------|--------------------------------------|

| J A     | 幹事会                   | 委員会                                  |

| 2008年4月 |                       | 4/25 (金) 14:00-17:00 JEITA 402 会議室   |

| 5月      |                       |                                      |

| 6月      |                       | 6/20 (金) 14:00-17:00 JEITA 506 会議室   |

| 7月      |                       |                                      |

| 8月      |                       |                                      |

| 9月      | 9/19 (金) 11:00-13:00  | 9/19(金) 14:00-17:00 JEITA 関西支部 第2会議室 |

| 10 月    |                       |                                      |

| 11月     | 11/14 (金) 10:00-13:00 | 11/14(金) 14:00-17:00 JEITA 506会議室    |

| 12 月    |                       |                                      |

| 2009年1月 | 1/14 (水) 11:00-13:30  | 1/14 (水) 14:00-17:00 JEITA 502 会議室   |

| 2 月     |                       |                                      |

| 3月      | 3/19 (金) 10:00-12:30  | 3/19(金) 13:00-17:00 キャンパスプラザ京都 第2会議室 |

| 月        | EDA 標準化小委員会関連                                                |

|----------|--------------------------------------------------------------|

| 2008年 4月 | 4/22(火) 13:00-17:00 第1回 SystemC-WG JEITA 406 会議室             |

| 5 月      | 5/30(金) 10:00-12:00 第 1 回 EDA 標準化小委員会 機械振興会館 会議室             |

| 5 A      | 5/16(金) 13:00-17:00 第2回 SystemC-WG 龍名館 竹の間                   |

| 6月       | 6/20(金) 13:00-17:00 第3回 SystemC-WG JEITA 406 会議室             |

| 7月       | 7/25(金) 11:00-13:00 第 2 回 EDA 標準化小委員会 機械振興会館 会議室             |

| 7.73     | 7/18(金) 13:00-17:00 第4回 SystemC-WG JEITA 405 会議室             |

| 8月       |                                                              |

| 9月       | 9/19(金) 13:00-17:00 第5回 SystemC-WG 日本ケイデンス社 新横浜本社内会議室        |

| 10 月     | 10/2(金) 11:00-13:00 第3回 EDA 標準化小委員会 機械振興会館 会議室               |

| 10 月     | 10/17(金) 13:00-17:00 第6回 SystemC-WG JEITA 関西支部 第2会議室         |

|          | 11/26(水) 10:00-17:00 第1回 Power FormatWG 龍名館 龍の間              |

| 11 月     | 11/21(金)-11/22(土) 第7回 SystemC-WG(集中審議) 下呂ロイヤルホテル 雅亭          |

|          | 11/27(木) 11:00-13:30 第 4 回 EDA 標準化小委員会 機械振興会館 会議室            |

| 12 月     | 12/19(金) 14:00-17:30 第2回 SystemVerilog-WG 日本ケイデンス社 新横浜本社内会議室 |

| 12 /7    | 12/19(金) 13:00-17:00 第8回 SystemC-WG JEITA 404 会議室            |

| 2009年1月  | 1/16(金) 13:00-17:00 第9回 SystemC-WG 龍名館 龍の間                   |

| 2月       | 2/20(金) 13:00-17:00 第 10 回 SystemC-WG JEITA 501 会議室          |

| 3 月      | 3/26(木) 11:00-13:30 第 5 回 EDA 標準化小委員会 機械振興会館 会議室             |

| 3 月      | 3/19(金) 13:00-17:00 第 11 回 SystemC-WG 九段会館 4F あおいの間          |

| 月        | ナノ世代物理設計 WG 関連                                         |

|----------|--------------------------------------------------------|

| 2008年 4月 | 4/18(金) 13:00-17:00 第1回ナノ世代物理設計 WG 日本教育会館 902会議室       |

| 5月       | 5/23(金) 10:00-17:00 第2回ナノ世代物理設計WG 龍名館 竹の間              |

| 6 月      | 6/27(金) 13:00-17:00 第3回ナノ世代物理設計 WG JEITA 502会議室        |

| 7月       | 7/25(金) 13:00-17:00 第4回ナノ世代物理設計WG JEITA 関西支部 電子会館8階会議室 |

| 8月       | 8/29(金) 13:00-17:00 第5回ナノ世代物理設計WG JEITA 507会議室         |

| 9月       | 9/26(金) 10:00-17:00 第6回ナノ世代物理設計 WG JEITA 505、507会議室    |

| 10 月     | 10/24(金) 11:00-17:00 第7回ナノ世代物理設計WG JEITA 関西支部 第一会議室    |

| 11 月     | 11/28(金)-11/29(土) (集中審議) 第8回ナノ世代物理設計 WG ヴィラ伊豆 (富士通保養所) |

| 12 月     | 12/19(金) 13:00-17:00 第9回ナノ世代物理設計 WG JEITA 403会議室       |

| 2009年1月  | 1/16(金) 10:00-17:00 第 10 回ナノ世代物理設計 WG 龍名館 竹の間          |

| 2月       | 2/20(金) 10:00-17:00 第 11 回ナノ世代物理設計 WG JEITA 503 会議室    |

| 3月       | 3/27(金) 10:00-17:00 第 12 回ナノ世代物理設計 WG JEITA 405 会議室    |

| 月                                                                                                                                                                                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2008 年 4 月       4/25(金) 10:00~13:50 第 2 回実行委員会 JEITA5 階「501」会議室         5 月       5/30(金) 13:00~16:50 第 1 回企画 WG JESA 会議室         6 目       6/20(金) 11:00~14:00 第 2 回企画 WG JEITA 403⇒506 会議室 |  |

| 4/25(金) 10:00~13:50 第 2 回実行委員会 JEITA5 階「501」会議室 5 月 5/30(金) 13:00~16:50 第 1 回企画 WG JESA 会議室 6/20(金) 11:00~14:00 第 2 回企画 WG JEITA 403⇒506 会議室                                                  |  |

| 6/20(金) 11:00~14:00 第 2 回企画 WG JEITA 403⇒506 会議室                                                                                                                                              |  |

| 6   1   1   1   1   1   1   1   1   1                                                                                                                                                         |  |

| 6/27(金) 14:00~18:00 第 3 回実行委員会 JESA 会議室                                                                                                                                                       |  |

|                                                                                                                                                                                               |  |

| 7月 7/25(金) 13:00~16:30 第 3 回企画 WG JEITA 会議室                                                                                                                                                   |  |

| 8月 8/28(木) 14:00~18:30 第 4 回実行委員会 JESA 会議室                                                                                                                                                    |  |

| 9月 9/11(木) 10:00~13:30 第 4 回企画 WG JESA 会議室                                                                                                                                                    |  |

| 10月 10/9(木) 13:30~17:00 第 5 回実行委員会 JESA 会議室                                                                                                                                                   |  |

| 10 月 10/23 (木) 14:00~17:30 第 5 回企画 WG JESA 会議室                                                                                                                                                |  |

| 11/6(木) 14:00~17:30 委員長会議 JESA 会議室                                                                                                                                                            |  |

| 11月 11/19(木) 14:00~17:30 第6回企画 WG JESA 会議室                                                                                                                                                    |  |

| 11/28(金) 13:30~17:30 第 6 回実行委員会 JESA 会議室                                                                                                                                                      |  |

| 12月 12/12(金) 12:00~15:00 第7回企画 WG JESA 会議室                                                                                                                                                    |  |

| 2009年1月                                                                                                                                                                                       |  |

| 2/6(金) 10:00~12:00 幹部会議(次期体制) JESA 会議室                                                                                                                                                        |  |

| 2/19(木) 11:00~13:00 幹部会議(次期体制) JESA 会議室                                                                                                                                                       |  |

| 2月 2/19(木) 13:00~15:00 第 8 回企画 WG JESA 会議室                                                                                                                                                    |  |

| 2/27(金) 13:30~17:00 第7回実行委員会 JESA 会議室                                                                                                                                                         |  |

| 3月                                                                                                                                                                                            |  |

| 月       | システム・デザイン・フォーラム 2009WG 関連                                   |

|---------|-------------------------------------------------------------|

| 2008年4月 |                                                             |

| 5月      | 5/12(月) 15:00-18:00 第 1 回システム・デザイン・フォーラム 2009WG JESA 会議室    |

| 6月      | 6/20(金) 10:00-12:00 第2回システム・デザイン・フォーラム 2009WG JEITA 502 会議室 |

| 7月      | 7/23(水) 14:00-17:00 第3回システム・デザイン・フォーラム 2009WG JESA 会議室      |

| 8月      |                                                             |

| 9月      | 9/11(木) 14:00-17:00 第 4 回システム・デザイン・フォーラム 2009WG JESA 会議室    |

| 10 月    | 10/17(金) 10:00-12:00 第 5 回システム・デザイン・フォーラム 2009WG JESA 会議室   |

| 11月     |                                                             |

| 12 月    | 12/12(金) 15:00-17:00 第6回システム・デザイン・フォーラム 2009WG JESA 会議室     |

| 2009年1月 | 1/8(木) 15:00-17:00 第7回システム・デザイン・フォーラム 2009WG JESA 会議室       |

| 2月      | 2/19(木) 15:00-17:00 第 8 回システム・デザイン・フォーラム 2009WG JESA 会議室    |

| 3 月     |                                                             |

-16-

| 月            | 関連行事                                                                                    |

|--------------|-----------------------------------------------------------------------------------------|

| 2008年 4月     |                                                                                         |

| 5月           | 5/14(水) 9:30-18:00 IEEE SAセミナー 「Global Standards, Local Benefits」<br>ソニー (株) 本社 2階 大会議場 |

| 6月           | 6/10(火) IEC/TC93/WG2 会議 アナハイム                                                           |

| 7月           |                                                                                         |

| 8月           |                                                                                         |

| 9月           |                                                                                         |

| 10 月         | 10/28(火)-10/30(木) IEC/TC93 国際会議 IEC Asia-Pacific Regional Centre (IEC-APRC)             |

| 11 月         |                                                                                         |

| 12 月         |                                                                                         |

| 2009年1月      | 1/22(木) IEC/TC93 Secretary、JPN NC 意見交換会 パシフィコ横浜 会議室                                     |

| 2000 + 1 ) 1 | 1/23(金) IEEE DASC 会議 パシフィコ横浜 会議室                                                        |

| 2月           | 2/25(水) IEC/TC93/WG2 会議 サンノゼ                                                            |

| 3月           |                                                                                         |

-17-

2. 各技術委員会の活動報告

# 2.1 ナノ世代物理設計ワーキンググループ(Nano Scale Physical Design Working Group)

#### 2.1.1 目的

半導体デバイス・配線テクノロジの進化に伴い、新たな設計上の課題があらわれてきている。 また、これらの課題を解決するため各社が開発した手法やライブラリが、そのテクノロジが一般 化した後も標準化されず、設計環境の開発・サポートコスト低減の障害となる事例や、半導体ベンダと顧客との情報授受がスムーズに行えない事例が増えてきている。

上記課題を背景として、本ワーキンググループでは、次のような調査及び標準化を実施することにより、より効率的な設計環境の実現に貢献することを目的として活動を行っている。

- 次世代(45 ナノメータ)以降のテクノロジ・ノードにおける、LSI の物理設計・検証に関する 課題の抽出

- 半導体ベンダとその顧客との間でやり取りするライブラリや設計情報等を規定する、設計 ルール・ガイドラインの作成

- LSI の物理設計、検証手法の精度、互換性や効率を向上できるライブラリの標準化

- 各種ライブラリを用いて行う検証が十分な精度で行えるかを判定するための標準ベンチマ ークデータの作成

#### 2.1.2 活動内容

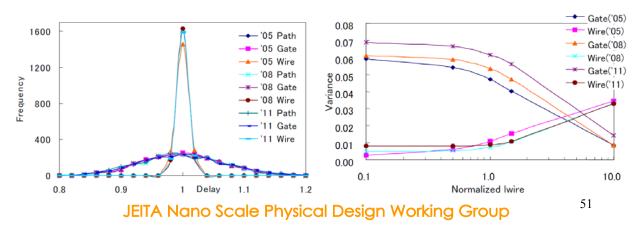

2007年5月から活動を開始し、今年度は、ばらつきに関わる下記のテーマを取り上げて調査や検討を行った。

- 製造ばらつきに起因するリーク電流変動の低減法

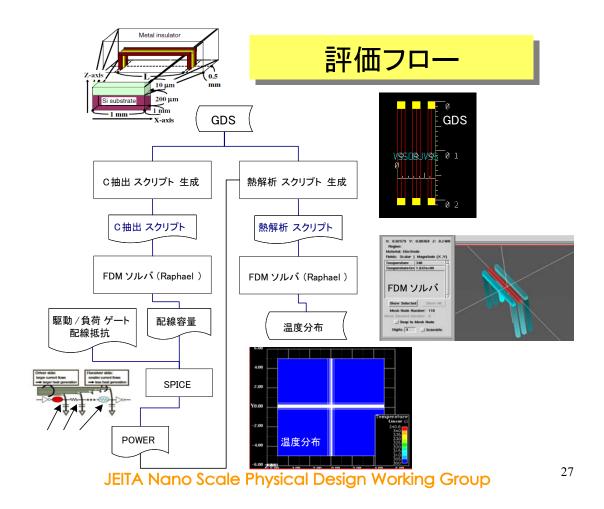

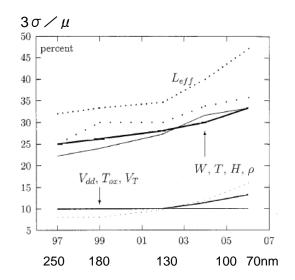

- 32nm プロセスにおける配線自己発熱の信号伝播遅延に対するインパクト調査

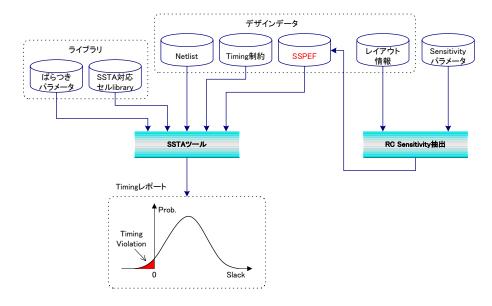

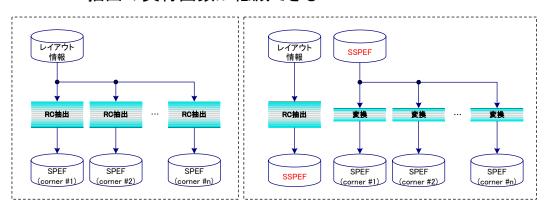

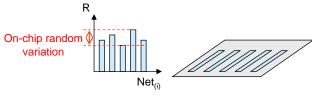

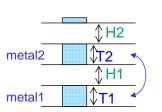

- 配線ばらつきの表現手段の調査、検討

今年度の活動の成果として、以下の2項目について調査を行い、有用な知見を得た。

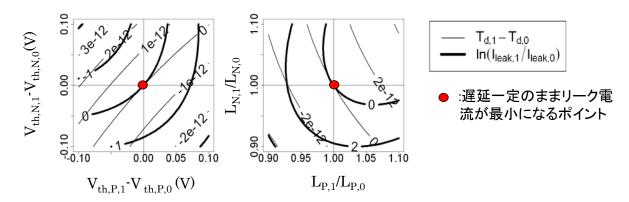

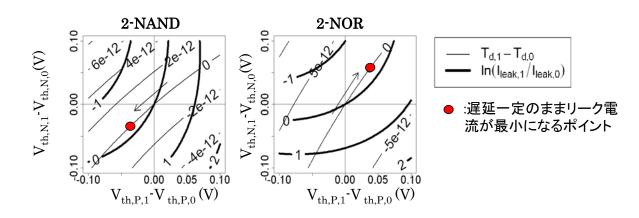

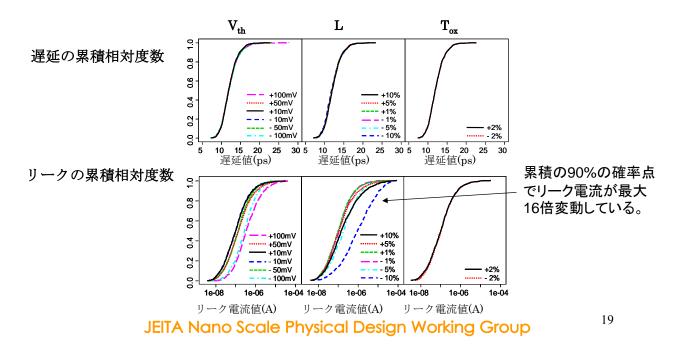

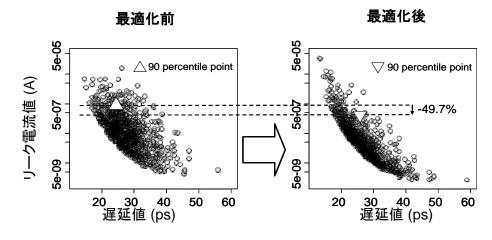

#### (1) 製造ばらつきに起因するリーク電流変動の低減アプローチ

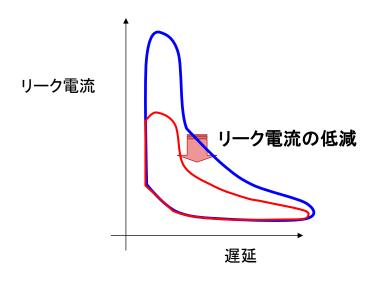

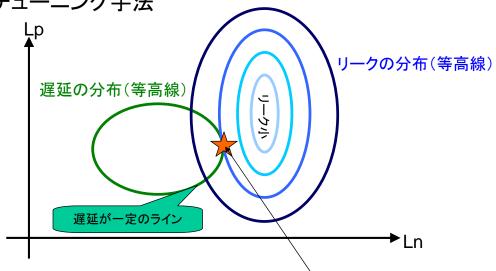

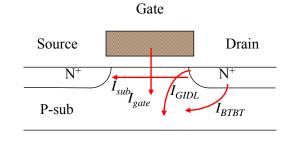

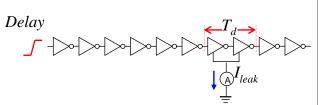

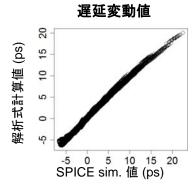

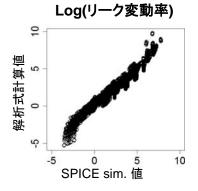

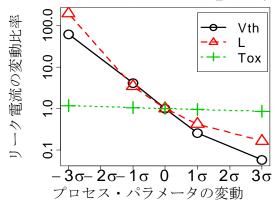

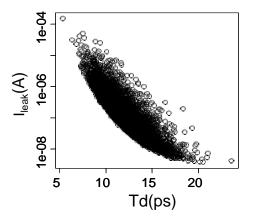

リーク電流はLSI 製品の商品価値を大きく左右する重要な因子である。プロセスばらつきによるリーク電流ばらつきは、チップ毎にリーク電流が異なる結果となり、リーク電流ばらつきを抑えることはLSI の品質を確保する上で重要である。本活動では、プロセスばらつきが遅延とリーク電流ばらつきへ与える影響に着目した。はじめにプロセスばらつきが遅延とリーク電流へ与える影響を評価するための解析式を導出し、遅延が一定でもリーク電流ばらつきが変動する場合を議論し、リーク電流ばらつきを低減する方法を提案した。提案するリーク電流ばらつき低減方法は、実験により、何も考慮しない従来の一般設計と比較して、歩留まり90%とした場合のリーク電流値に対して50%の低減効果があることを示した。

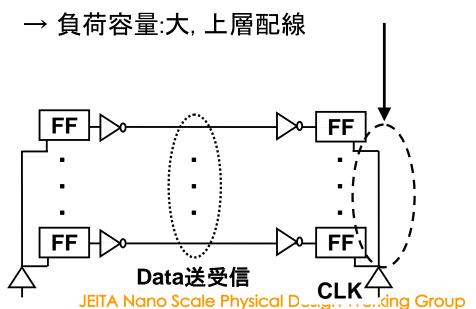

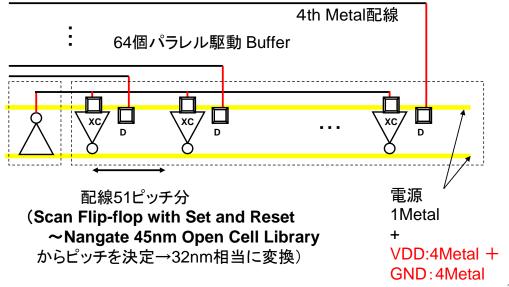

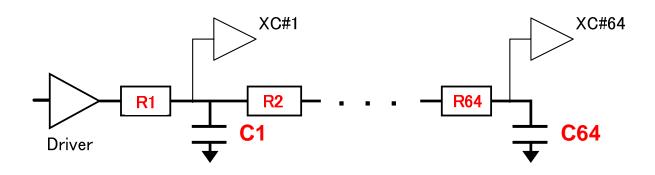

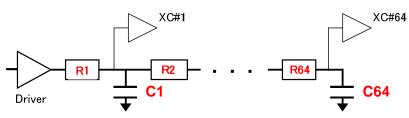

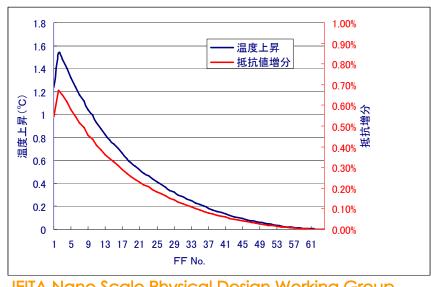

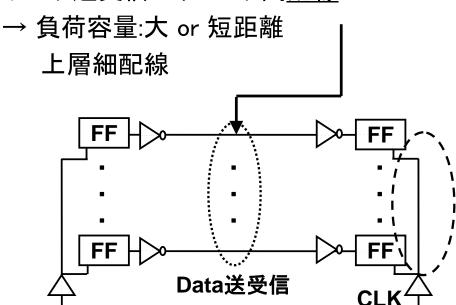

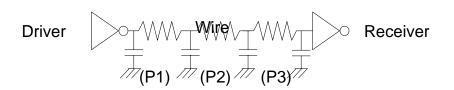

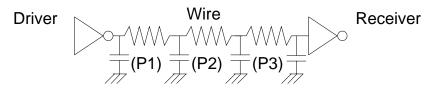

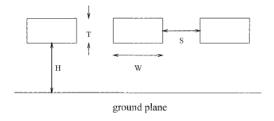

# (2) 32nm プロセスにおける配線自己発熱の信号伝播遅延に対するインパクト調査

現実的な物理的なパラメータを使用して、32nm プロセスにおける信号伝播遅延に対する配線自己発熱のインパクト評価を行った。配線自己発熱が顕著になると思われる回路構成の1つとして64 ビットのデータ伝送モデルを評価した。解析の結果、周囲の温度からの最大温度上昇は5.49 C、配線抵抗の増加は4.82%となり、それによる遅延時間増加は2.72%となった。想定した32nm プロセスに対しては、遅延マージンとして2.72%分に相当するインパクトを生じうることがわかった。また、実験結果は、配線自己発熱が大きな負荷を短距離配線で駆動する場合に顕著であることも示した。

これらの活動で得られた成果は、次のような形態により無償で一般に公開する。

- アニュアルレポート

- JEITA のホームページ

- 関連学会の研究会・学会における発表や論文誌への投稿

成果の詳細は本アニュアルレポートの付録に掲載した。また、今年度の成果の一部を以下の学会、 にて発表した。

[1] 「製造ばらつきに起因するリーク電流変動の低減アプローチ」,回路とシステム軽井沢ワークショップ,2009年4月.

また、本年度は EDS フェア/システムデザインフォーラムにおいて、プロセス微細化による製造 ばらつきの問題に対して、「最先端統計から見た 32nm ばらつき予測と設計法」をテーマとした、「ナノ世代物理設計フォーラム」を開催。

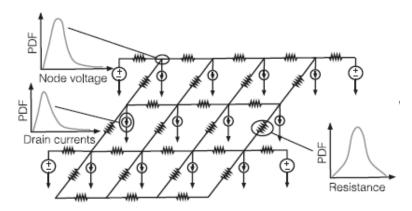

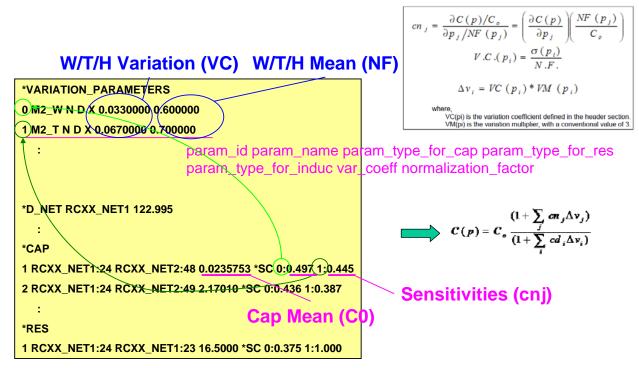

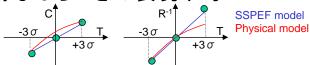

さらに、EDS フェア会期中に開催された IEEE DASC 会議に参加、配線ばらつきを表現する Sensitivity SPEF フォーマットの策定に対応する DPC-WG との連絡を開始した。

#### 2.1.3 関連機関の動向

米国に本部を置き、世界各国に多数の会員を持つ国際的な学会であり、電気および電子関連の標準化活動を長年にわたり実施している IEEE。その下部組織として、エレクトロニクス産業における設計自動化関連の標準化活動を行っている DASC (Design Automation Standards Committee がある。その中のワーキンググループのひとつに、P1481 Circuit Delay and Power Calculation (DPC) Working Group があり、本ワーキングのテーマのひとつである配線ばらつきの表現フォーマット(Sensitivity SPEF)策定を行っている。

一方日本では、半導体MIRAI(Millennium Research for Advanced Information Technology)プロジェクトが、ASRC(産総研次世代半導体研究センター)、ASET(技術研究組合 超先端電子技術開発機構)、Selete(株式会社 半導体先端テクノロジーズ)を中心とする産官学で共同し、半導体最先端技術の「壁」を克服する共通基盤としての役割を担っている。具体的には、半導体の微細加工において、45nmの技術世代以降の LSIの消費電力や処理速度といった基本的な性能を格段に向上させる技術を開発している。また、半導体理工学研究センターSTARC(http://www.starc.or.jp/)では、SoC設計技術等の先導開発(あすか 2)が行われている。

# 2.1.4 参加メンバー

主 査 金本俊幾 ㈱ルネサステクノロジ

副主査 中島英斉 NECエレクトロニクス㈱

同 高藤浩資 ㈱リコー

委員 黒川 敦 三洋半導体㈱

同 蜂屋孝太郎 ㈱ジーダット

同 古川 且洋 ㈱ジーダット

同 田中正和 パナソニック㈱

同 増田弘生 ㈱ルネサステクノロジ

同 佐 方 剛 富士通マイクロエレクトロニクス㈱

同 奥村隆昌 ㈱半導体理工学研究センター

客 員 佐藤高史 東京工業大学

客 員 橋本昌宜 大阪大学

- 20 -

#### 2.2 EDA 標準化小委員会

#### 2.2.1 EDA 標準化小委員会

# (1)発足の背景とミッション

JEITA/EDA 技術専門委員会の標準化活動は、1990年の EIAJ/EDIF 研究委員会設立に始まり、 当初は EDA に関するグローバルな重要課題に対して日本の業界を代表する唯一の機関として、 特に設計記述言語の仕様標準化とその啓蒙等に多大な貢献を果たしてきた。近年は活動の中心 が設計記述言語の普及定着と環境変化に応じて、先端的設計技術に関する調査・研究等にシフトしてきている。

システム設計メソドロジの革新が進展する中で、設計技術言語の国際標準化は依然として重要なテーマである。そこで、標準化関連の活動をより明確に位置づけるため、2000 年 11 月に本小委員会が設立された。

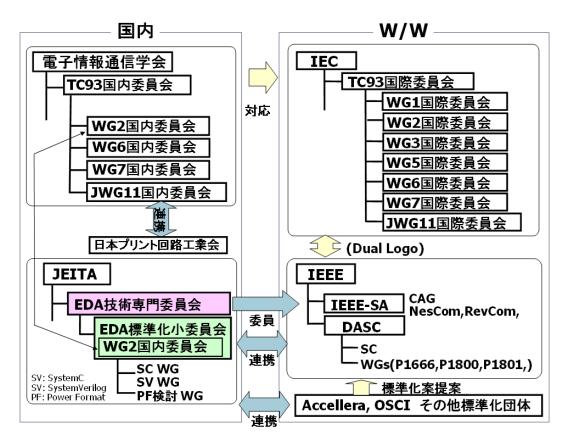

世界的にみれば EDA 関連の標準は IEC(International Electrotechnical Commission)と IEEE (The Institute of Electrical and Electronics Engineers)で議論、制定されてきた。 IEC ではデザインオートメーションを議論する TC(Technical Committee) 93、IEEE はコンピュータソサイエティの DASC(Design Automation Standards Committee)、および SA(Standards Association)である。これまでは IEEE で定められた標準を IEC でも追認するものも多かった。 2003 年より議論は IEEE の DASC/SA のワーキンググループでも、標準の制定は IEC と IEEE で同時にできるようになった(Dual Logo)。

国内では IEC の対応機関は、日本工業標準調査会(JISC: Japanese Industrial Standards Committee) である。また、TC 毎に国内委員会があり、電子情報通信学会や JEITA 内に組織化されている。TC93 とハードウェア設計記述言語関連のワーキンググループ(WG2)の国内委員会は電子情報通信学会にある。

本小委員会は IEC/T C93/WG2 国内委員会を兼ねて活動するという協調体制を 2002 年度に確立した (図-1 参照)。その結果、EDA 標準化小委員会の委員が IEC/T C93/WG2 の各種標準化提案を直接審議することができるようになった。

2003 年度には、SystemC および SystemVerilog の標準化を業界として検討・推進する目的で、それぞれワーキンググループを発足させた。2007 年度には、CPF(Common Power Format)と UPF(Unified Fower Format)の二つの Power Format の標準化案の議論と統一を目的に、検討ワーキンググループを発足させた。SystemC は、ますます重要性が認識されているシステムレベルの設計言語のひとつであり、SystemVerilog は IEEE1364(VerilogHDL)の後継・検証技術の拡張である。CPF/UPFの Power Format は、主にシステム LSI の低消費電力化設計の効率化を目的とした設計言語である。これらワーキンググループは、日本の標準化組織として、海外の関連団体と連携し、言語仕様の専門的な技術検討と改善提案を通じて、標準化へ貢献すること目指して活動を行っている。

図-1 EDA標準化小委員会と他の標準化組織との関係

以上のような発足の背景の中で、2002 年度に本小委員会は、そのミッションを以下のように 規定し、活動に取り組んでいる。

#### 目的:

EDA 標準化小委員会(以下本小委員会)は EDA(Electronic Design Automation)関連技術の標準化動向の調査、標準化の推進、標準の策定、標準案の調査、標準の保守・改定、などを推進し、もって国内外の関連業界の発展に寄与することを目的とする。

#### 活動内容:

本小委員会は EDA および関連技術の標準化に関して、

- 内外の動向を調査、検討し、

- ・技術および関連業界の発展に資する提案の必要性を模索し、

- ・必要かつ可能な場合には、関係機関に対して提案を行い、

- ・内外の標準化関連機関との連携・協調・協力を推進し、

- ・特に、デザインオートメーション/設計記述言語(TC93/WG2)WGの活動を支援し、

- ・また広報活動を行う。

# (2) 2008年度 EDA 標準化小委員会メンバー (2009年3月現在 敬称略)

主査 太田 光保 パナソニック(株)

副主査 江田 努 ローム(株)

副主査 小島 智 NEC システムテクノロジー(株)

(TC93/WG2 ココンベナ)

委員 吉田 正昭 NEC エレクトロニクス(株)

委員山田 節三洋電機(株)委員西本 猛史シャープ(株)

委員 熊谷 敬 セイコーエプソン(株)

委員齋藤 茂美ソニー(株)委員南 文裕(株)東芝

委員 河村 薫 富士通マイクロエレクトロニクス(株)

委員 秋山 俊恭 (株)ルネサステクノロジ

特別委員 相京 隆 (株)半導体理工学研究センター

(TC93/WG2 Member)

特別委員 長谷川 隆 富士通マイクロエレクトロニクス(株)

(SystemC WG 主査、TC93/WG2 Member)

特別委員 今井 浩史 東芝(株)

(SystemC WG 副主査)

特別委員 浜口加寿美 パナソニック(株)

(SystemVerilog WG 主査 TC93/WG2 Member)

特別委員 中森 勉 富士通マイクロエレクトロニクス㈱

(Power Format WG 主査)

特別委員 金本 俊幾 ㈱ルネサステクノロジ

(ナノ世代物理設計 WG 主査)

特別委員 星野 民夫 (株)アプリスター

(TC93/WG2 Member)

特別委員 石河久美子 富士通マイクロソリューションズ(株)

(TC93/WG2 Member)

客員

今井 正治

大阪大学

客員

神戸 尚志

近畿大学

(TC93 国内委員長)

#### (3)2008年度活動

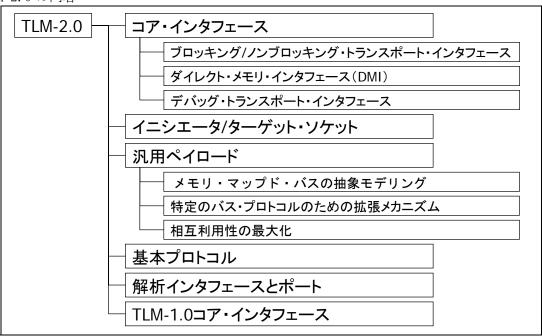

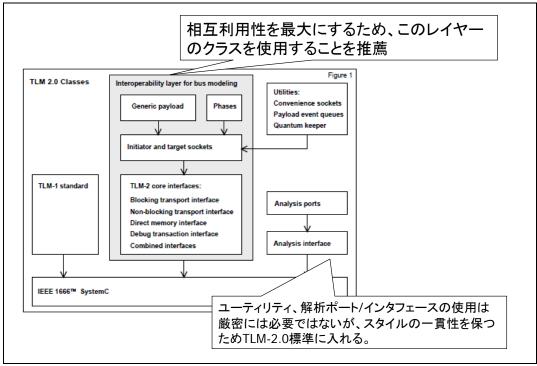

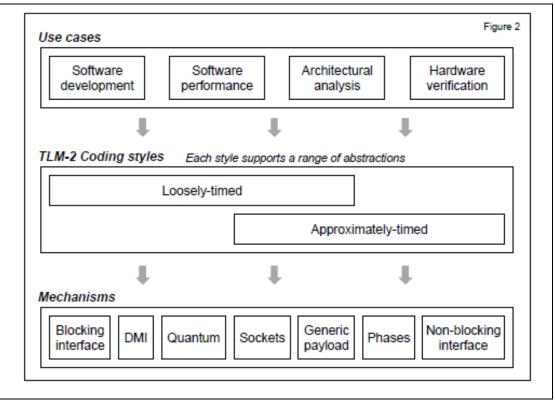

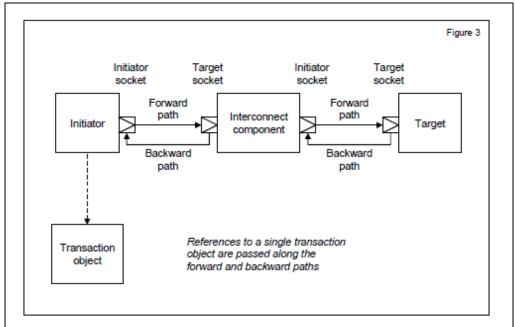

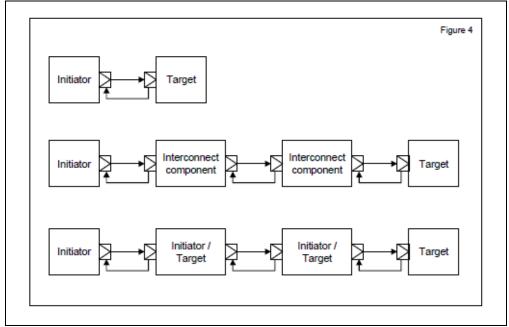

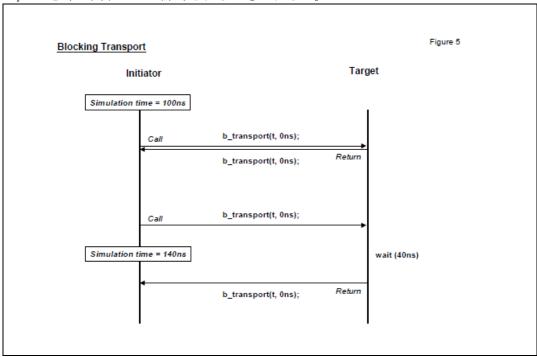

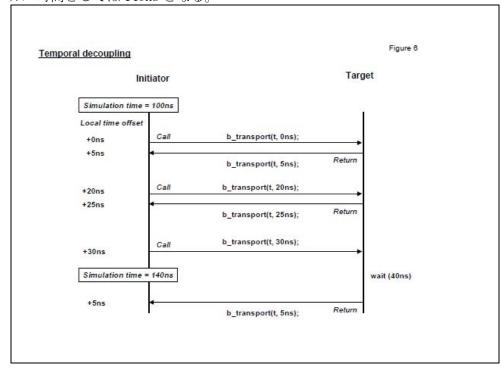

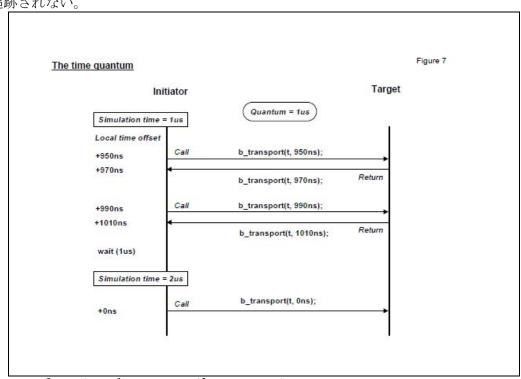

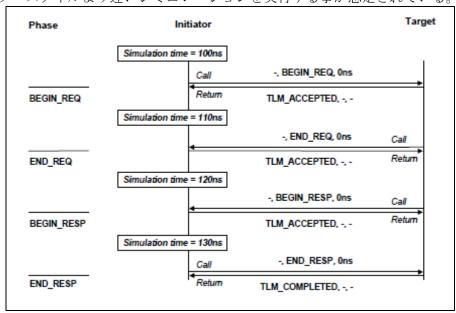

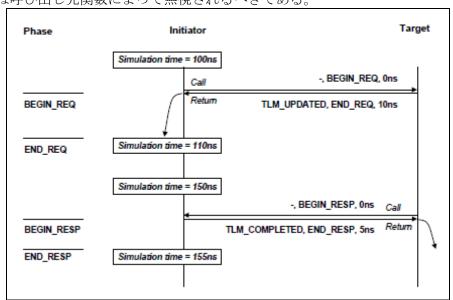

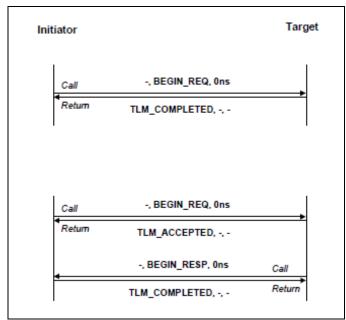

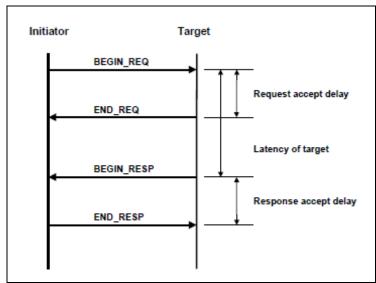

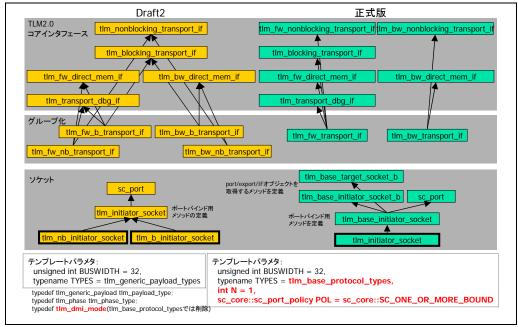

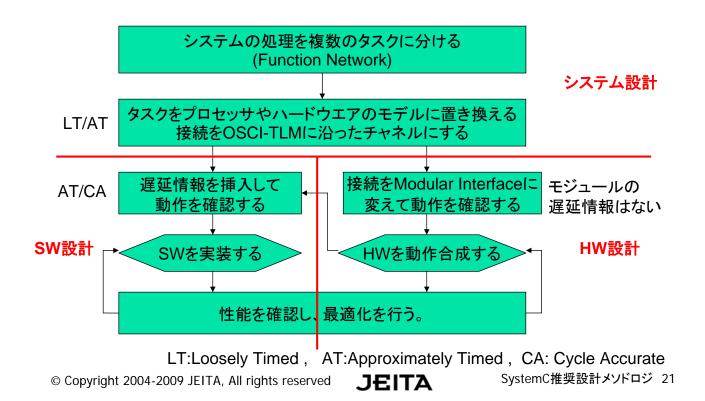

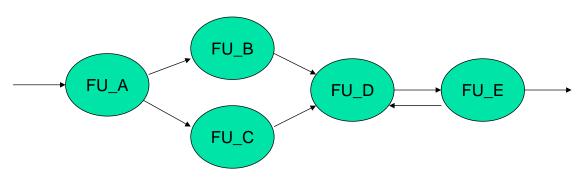

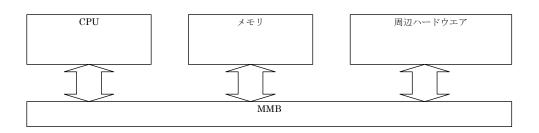

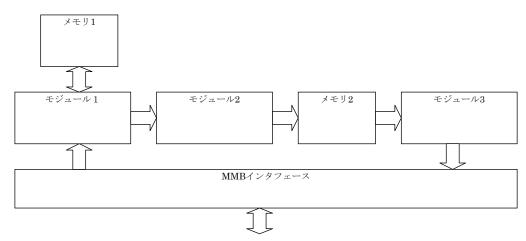

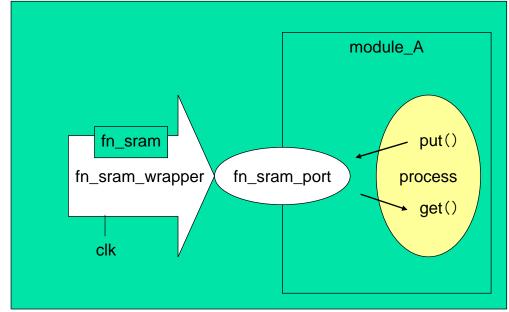

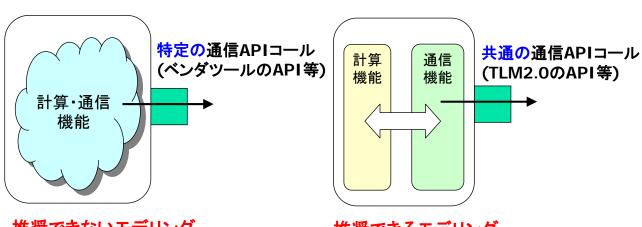

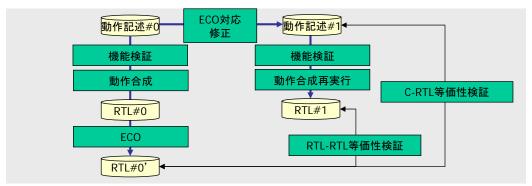

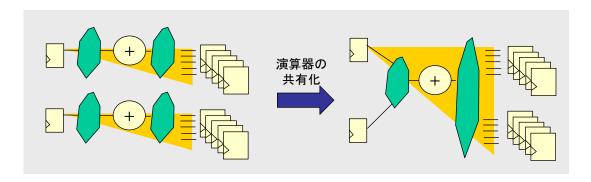

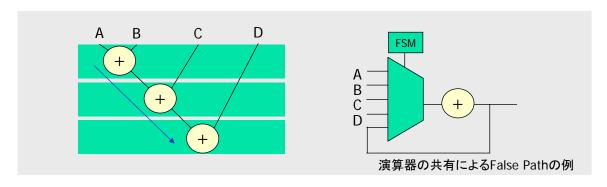

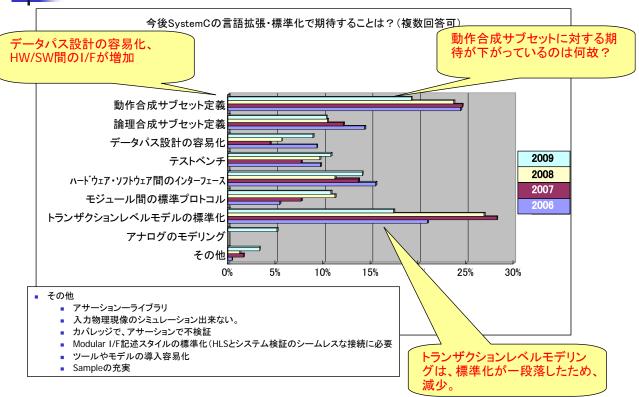

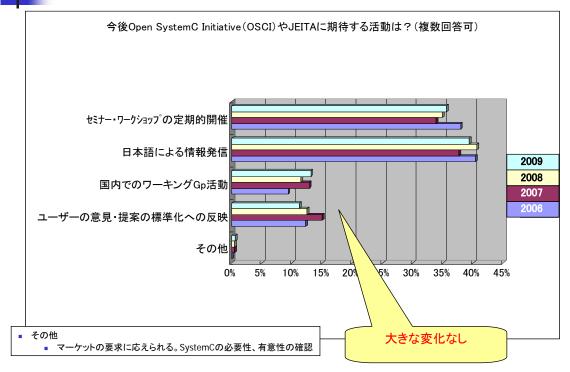

EDA標準化小委員会としては、年5回の会合を行い、傘下のSystemCワーキンググループ、 SystemVerilogワーキンググループ、Power Formatワーキンググループの活動状況の確認、標準 化関連課題の議論を行った。SystemC/SystemVerilogの両ワーキンググループは2005年末の SystemC、SystemVerilogのIEEE標準化に引き続き、新規標準化項目の調査検討、設計適用事例 の調査などの積極的な活動を継続した。具体的には、SystemCワーキンググループは、TLM2.0 の標準化の推進と合成サブセットの状況調査、および、推奨設計メソドロジのガイドライン作成に取り組んだ。また、最新SystemCに関わる技術の普及促進と標準化の推進を目的として、2009年1月のシステム・デザイン・フォーラム2009でSystemCユーザ・フォーラムを開催した。

SystemVerilogワーキンググループは、IEEE1364(VerilogHDL)とIEEE1800 (SystemVerilog)の統合ドラフトに対し、国内半導体業界の意向を反映させるべくレビューを行い、IEEE-SA標準案作成に貢献し、最終案に対して賛成投票を行なった。

昨年活動を開始したPower Formatワーキンググループでは、今年は、国内半導体業界の意向を反映させるべくIEEE P1801(UPF)の標準案についての調査と検討を行い、Si2が規定しているCPFとのインターオペラビリティに関する課題の指摘・修正案の提示を行なうと共に、反対投票を行なった。

また、関連する標準化関連の組織・団体とも、下記のような活発な交流を行った。

2008 年 10 月の IEC/TC93 シンガポール国際会議には、本委員会から TC93 国内委員会委員長である神戸客員、WG2 国際コ・コンベナの小島副主査、および小委員会主査の太田の 3 名が出席した。(詳細は 2.2.3 章 IEC/TC93 の (5) 項参照)

また、IEEE DASC の段階から標準の詳細についての論議が進む実態があることから、本年度より小島副主査を正規にメンバーとして登録し、深い連携がとれる体制をとった。また、2009年1月には、Victor Berman 議長他を招き、DASC の月例会議を日本で開催し、本小委員会からも多数が出席した。

更に、IEEE-SA との連携・協力の一環として、IEEE-SA One-Day Seminar(Tokyo Japan)において、小島副主査と長谷川 SystemC ワーキンググループ主査が、それぞれ「日本EDA標準化の推進状況」「The IEEE P1666 Project:日本国内における SystemC 標準化活動」というタイトルで講演し、我々の活動のアピールを行なった。

また、SystemC ワーキンググループは、TLM2.0 等の調査・検討で OSCI との連携を図っている。システム・デザイン・フォーラム 2009 では、OSCI から、後援と、TLM2.0 の最新状況に関するご講演とを頂いている。

# 2.2.2 IEEE/DASC(電気電子学会/設計自動化標準委員会)・IEEE-SA

#### (1)活動の概要

IEEE は米国に本部を置く電気、電子、情報、などの国際的な学会である。また、この分野の標準化活動を長年にわたり、しかも広範囲に実施している。DASC、SA は IEEE の下部組織として、エレクトロニクス産業における設計自動化関連の標準化活動を行っている。

活動の中心は、標準設計記述言語(HDL: Hardware Description Language)のVHDLとVerilog HDLに関連する設計と検証であり、タイミング情報、論理合成、算術関数とテストの標準化に注力している。これら設計言語に関連して、システムレベルまで適用範囲を拡大して、Analog Mixed Signal、ソフトウェアとハードウェア協調設計等の拡張の標準化を検討している。2005年には SystemCと SystemVerilog という高位設計技術言語、設計と検証を統合した記述言語の標準化作業が完了した。

### (2) JEITA/EDA-TC との関連

これまではEDA 技術専門委員会はIEEE/DASC のメンバーとして関連するWG に参加し、標準化案に日本の意見を反映してきた。2004年12月にはIEEE-SA の正式メンバーにもなり、IEEE の標準化活動に、ドラフトレビュー・標準化案の改善の提案・投票を通じて積極的に参加している。

特に、今年度は、EDSFair2009 合わせてに IEEE/DASC の月例会議を日本で開催した。(2008年1月23日) 会議には、米国からは Victor Berman 議長、Stan Krolikoski 副議長 Dennis Brophy 氏(Accellera Vice Chair)、本小委員会関係からは、太田主査、小島副主査、齋藤委員、山本委員、古井 TC93 国内幹事、長谷川特別委員、浜口特別委員、中森特別委員、金本特別委員、他ナノ世代物理設計WGからも委員3名が出席した。また、国外からの電話会議出席者も8名あり、計23名が出席し、盛会であった。

会議において、EDA 技術専門委員会からは、活動状況の紹介と、SystemC TLM2.0 の標準化のマイルストーン、IEEE1801 (Power Format) の balloting、Sensibity SPEF、AMS 関連言語のハーモナイゼーション等の状況確認を行なった。Sensibity SPEF については、WG の John Beatty 議長と金本特別委員がコンタクトをとることとなった。Berman 議長からは、各標準化団体間での標準の調整についての課題提起等があった。標準の調整に関する課題提起は、予ねてより、一つの分野には一つの標準を主張している JEITA の方針に合致しており、今後、重要となる案件である。

# (3)これまでの成果と現在の状況

#### (1)これまでの成果

DASC/SA ではこれまでに以下の標準化作業を行っており、そのうちのいくつかは、IEC でも標準として承認されている。

- (1) VHDL (Std-1076)

- (2) VHDL Analog Extensions (Std-1076.1)

- (3) VHDL Math Package (Std-1076.2)

- (4) VHDL Synthesis Package (Std-1076.3)

- (5) VHDL Timing (VITAL) (Std-1076.4)

- (6) Verilog HDL (Std-1364)

- (7) MVL-9 (Std-1164)

- (8) Waveform and Vector Exchange (WAVES) (Std-1029.1)

- (9) The RTL Synthesis Interoperability Standard (Std-1076.6)

- (10) The Delay and Power Calculation Standard (Std-1481)

- (11) The Open Model Fundations Standard (Std-1499)

- (12) SystemVerilog (Std 1800-2005)

- (13) Verilog (Std 1364-2005)

- (14) SystemC 2.1 (Std 1666)

#### ②現在の状況

2009年3月現在のDASCおよびSAとその傘下のWorking GroupとStudy Groupは以下のとおり。

- P1076 Standard VHDL Language Reference Manual (VASG)

- o VHDL-200x: the next revision

- o Issues Screening and Analysis Committee (ISAC)

- o VHDL Programming Language Interface Task Force (VHPI)

- P1076.1 Standard VHDL Analog and Mixed-Signal Extensions (VHDL-AMS)

- P1076.1.1 Standard VHDL Analog and Mixed-Signal Extensions Packages for Multiple Energy Domain Support (StdPkgs) - this group is now part of 1076.1

- P1076.4 Standard VITAL ASIC (Application Specific Integrated Circuit) Modeling Specification (VITAL) - This group is now part of 1076.

- P1481 Standard for Integrated Circuit (IC) Open Library Architecture (OLA) (IEEE1481R)

- P1647 Standard for the Functional Verification Language 'e' (eWG)

- P1685 SPIRIT XML Standard for IP Description (IEEE-1685)

- P1699 Rosetta System Level Design Language Standard

- P1778 ESTEREL v7 Language Standardization

- SystemVerilog Working Group

- P1800 SystemVerilog: Unified Hardware Design, Specification and Verification

Language (SV-IEEE1800) [cosponsored with IEEE-SA CAG]

- o P1364 Standard for Verilog Hardware Description Language (IEEEVerilog)

- P1850 Standard for PSL: Property Specification Language (IEEE-1850)

- P1801 Standard for the Design & Verification of Low Power ICs

# 2.2.3 IEC/TC93 (国際電気標準会議/デザインオートメーション)

#### (1)活動の概要

IEC は 1906 年に設立された国際標準化機関であり、本年が 102 年目ににあたる。設計自動化を取り扱う IEC/TC93 は 1992 年に設立された。TC93 の全体会議は毎年開催されており、スイス、英、仏、米、デンマーク、日、英、米、独、伊と開催されてきた。最近は、2002 年 10 月 中国・北京、2003 年 11 月・2004 年 10 月 米国・Piscataway、2005 年 9 月 日本・京都(奈良)、2006 年 9 月 ドイツ・ベルリン、2007 年 9 月米国・ガイザーズバーグでの開催があり、本年度は、10 月にシンガポールの IEC Asia-Pacific Regional Centre で開催された。

#### (2)TC93 の組織と参加国

2008 年 3 月現在 IEC の Web サイト (www. iec. ch) によれば、24 カ国が TC93 のメンバーとなっている。IEC のメンバー資格には、P(Participating) と 0(Observer) の二種類があるが、今年度、韓国が 0 メンバーから P メンバーに変わったことで、P メンバーが 4 カ国、0 メンバーが 20 カ国となった。韓国以外の P メンバーとしては、日本、中国、米国が登録されており、0 メンバーとして、オーストラリア、ベルギー、チェコ共和国、デンマーク、エジプト、フィンランド、フランス、ドイツ、ハンガリ、インド、アイルランド、イタリア、オランダ、ロシア、セルビア、シンガポール、スペイン、スウェーデン、ウクライナ、イギリスが登録されている。幹事国は米国(国際幹事: Victor Berman 氏)が、国際会議議長は日本(唐津氏)が担当している。

# (3)TC93 の組織とワーキンググループ(WG)

TC93 は 7 つの WG/JWG から構成されている。 特に、WG2、WG3、WG6、および WG7 は日本から 提案も含め積極的な貢献をしてきた。今までの各 WG の主な活動を示す。

**WG1:**モデルのハーモナイゼーション: (a) STEP Electrical (ISO 規格) と EDA 標準の整合性の検討、(b) EDIF と AP-210 との整合性の検討。(c) 言語間の I n t e r o p e r a b i l i t y の検討

WG2:ハードウェア設計記述言語: (a) VHDL 言語仕様、Verilog HDL の整合性等の検討、システム記述言語(SLDL)も議題に取り上げられてきた。(b) IC delay&power calculation system の検討。 日本からの提案 ALR 標準化; IS(国際規格)化完。現在は

SystemC, SystemVerilog, PowerFormat が中心。

WG3:設計データ交換表現: PDX(Product data eXchange)によるマテリアルデクラレーション関連への対応の議論。

JWG11:記述の XML 化の流れへの取り組み方の議論。

WG5: 規格適合性(コンフォマンス)テストの具体的事案の議論。

WG6: 再利用可能部品ライブラリ、日・米・欧の各プロジェクト間の仕様整合と連携の検討、日本からは JEITA/ECALS プロジェクトの成果を提案している。 IBIS も話題に取り上げられている。 最近は電子カタログの流通に関する規格案が議論の中心となっている。

WG7:システムテスト記述言語、ATML(Automatic Test Markup Language)の検討。

# (4) TC93 国内委員会と主要メンバー(2008 年 3 月現在。敬称略)

・ TC93 国際会議

議長: 唐津 治夢(SRI インターナショナル)

• 国内専門委員会

委員長: 神戸 尚志(近畿大学) \*

幹事: 古井 芳春 (STARC)

委員:太田 光保(パナソニック)\*、柴田 明一(JPCA)、高橋 満(日立)、山下 寛巳(SML)

・WG2:(ハードウェア設計記述言語) 主査: 太田 光保(パナソニック) \*

国際コ・コンベナ: 小島 智(NEC システムテクノロジー) \*

委員: 長谷川 隆(富士通マイクロエレクトロニクス) \*、浜口 加寿美(パナソニック) \*、 中森 勉(富士通マイクロエレクトロニクス) \*、山田 節(三洋) \*

- ・WG3:(設計データ交換表現) 主査:神戸尚志(近畿大学)\*

- ・WG6: (再利用可能部品ライブラリ) 主査: 高橋 満(日立、国際コ・コンベナー)

- ・WG7:(システムテスト記述言語) 主査:山下 寛巳(SML)

委員: 唐津 治夢(SRI インターナショナル、国際コ・コンベナ)

\*印はEDA技術専門委員会からの参加者

#### (5)TC93 シンガポール会議の報告

2008年の国際会議は、10月にシンガポールの IEC Asia-Pacific Regional Centre (IEC-APRC) で開催された。

従来、Pメンバー国としては日本と米国のみの参加も多かったが、本年は、中国と、新たに Pメンバー国として加わった韓国、および、0メンバー国シンガポールの計5カ国からの参加 があり、深い議論ができた。出席者は、米国から4名、日本からは7名、韓国・中国・シン ガポールからは、各1名の出席があった。

会議では、TC93 プレナリー会議、WG1, WG2, WG3, WG6, WG7, JWG11 の 7 会合が開催された。 WG 2 では、小島副主査から国際コ・コンベナとして、IEEE1076-2008/IEC61691-1-2 (VHDL)、 IEEE1800-2010/IEC61691-6-2 (Integration of System Verilog and VerilogHDL)、IEEE1801/ IEC61523-4 (Power Format), IEEE1481-1999/IEC61523-1-2 (DPC),

IEEE1497-2001/IEC61523-3-2(SDF)等の 2009 年以降に予定されているデュアルロゴ案件の報告・確認等が行なわれた。

JEITAからはEDA技術専門委員会の活動状況や、IEEE、Accellera、OSCI等との連携状況を紹介するとともに、Power Format に関する二つの標準化の動向に懸念を示し、インタオペラビリティの確保を求めた。

また、WG1 では、神戸国内委員長より、WG2 で標準が規定される前に、その言語やフォーマットを検討して、既存の標準とのインタオペラビリティを確認すべきであるとの提案が出され、WG1 の課題として残すこととなった。

# (6) IEC 規格投票について

本年は IEC 標準に関わる投票は無かったが、2009 年度以降、次の 5 件が IEEE 標準からのデュアルロゴとして、FDIS (Final Draft International Standard) 投票が行われる見込みである。

- 1) IEEE1076-2008 (VHDL)  $\Rightarrow$  IEC61691-1-2

- 2) IEEE1800-2010(Integration of System Verilog and VerilogHDL) ⇒ IEC61691-6-2

- 3) IEEE1801 (Power Format)  $\Rightarrow$  IEC61523-4

- 4) IEEE1481-1999 (DPC)  $\Rightarrow$  IEC61523-1-2

- 5) IEEE1497-2001 (SDF)  $\Rightarrow$  IEC61523-3-2

## 2.2.4 SystemC ワーキンググループ報告

# (1) 背景

ハードウェア記述言語によるシステムLSIの設計は、VHDL(IEEE 1076)やVerilog-HDL (IEEE 1364)の標準化へのJEITA(旧 EIAJ)の貢献とともに広く普及して、産業界で活用されている。一方、半導体の微細化技術は開発がさらに加速され、既に1000万ゲート規模のLSIが開発されるに至り、さらに抽象度の高いレベルからの設計が必須となってきている。1990年代半ばより複数のシステムレベル設計言語の提案が行われ、標準化推進団体が結成されたものもあった。この中で、C++言語を基本とするSystemCは広く半導体メーカ、システムメーカ、EDAベンダーの賛同を得て、Open SystemC Initiative (OSCI) が結成され、標準化のための言語仕様の策定と整備が進められてきた。

システムレベル設計言語としての要件を備えた System  $C_{2.0}$  のリファレンスシミュレータがまず  $C_{2.0}$  9 月にリリースされ、その後  $C_{2.0}$  9 月に言語参照マニュアル

(Language Reference Manual,以下LRM)が一般公開された。このLRMが2004年11月にOSCIよりIEEEに移管され、IEEE P1666として正式な標準化プロセスが開始された。並行してOSCIにて開発されていたSystemC 2.1の言語拡張仕様もIEEE P1666標準の一部として追加移管され、2005年12月にIEEE Std. 1666-2005としてSystemCのコア言語部分の標準化が完了した。

# (2) 目的

上記のように標準化が進められた SystemC は、SoC(System on Chip)の開発のためのシステムレベル記述言語として既に設計や検証に幅広く使われるようになり、欠くことのできない言語となってきている。設計言語は設計の基本となるもので、この標準化策定に早くから関わることは、産業界にとって次世代の設計手法を構築する上で非常に重要なことである。

本ワーキンググループは2003年10月に設置され、日本国内における唯一のSystemCの標準化関連組織として、IEEE P1666で進められるSystemC標準作業に対して日本の産業界として意見を述べ、国内事情・要求事項を取り込んだ形で国際標準化に貢献していく。また、SystemCに関連した調査結果をアニュアルレポートやユーザ・フォーラム等で積極的に情報発信を行うことで、SystemCを利用した設計手法の国内普及を図り、ひいては日本の産業界の国際競争力を高めることを目指す。

#### (3) これまでの成果

2003年10月に発足した後、これまでに次のような成果をあげた。

- ① SystemC 標準化活動

- 2003 年度は OSCI より 2003 年 5 月に一般公開された LRM についてレビューを行い、問題点を 62 件抽出し(うち 46 件については 2003 年度の活動報告書に一覧を記載)、IEEE 並びに OSCI に報告した。

- ・ 2004 年度は IEEE P1666 のメンバーとして活動を行い、IEEE 版の LRM(Draft)

をレビューし、43件の問題点をIEEEに報告した。

- 2005 年度は SystemC 2.1 が追加された IEEE P1666 版 LRM についてレビューを行い、19件の問題点を抽出し IEEE に報告した。2005 年 12月5日に IEEE Std. 1666-2005 として SystemC の基本言語部分の標準化が完了した。プレスリリースも発行され、EDA-TC/JEITA としてもコメントを掲載した。

- 2006 年度は OSCI よりリリースされた TLM(トランザクションレベルモデリング)

2.0 ドラフト1、及び合成サブセットドラフトについてレビューを行い、問題点や 要望事項をそれぞれ4件、57件 OSCI に伝えた。

- ・ 2007 年度は OSCI よりリリースされた TLM 要求仕様、用語集について分析を行い、 また 11 月にリリースされた TLM 2.0 ドラフト 2 についてレビューを行い、問題点 や要望事項を 10 件 OSCI に伝えた。

- 2008年度はOSCIよりリリースされたTLM 2.0正式版のユーザーズマニュアルについてレビューを行い、問題点や要望事項を7件OSCIに伝えた。(詳細は「4.2.4 OSCI TLM2.0 へのフィードバック」を参照)また、ユーザーズマニュアルの抄訳を作成し、本アニュアルレポートにて公開した。

# ② SystemC 技術調査

- ・ 2003 年 11 月度に集中審議を行い、本ワーキンググループ参加各社の SystemC 利用状況について紹介しあい、業界内の現状ステータスについて理解を深めた。

- ・ 2004 年度には、過去 5 年間に一般に公開されている SystemC 関連の論文や発表資料等 50 件の調査を行い、報告書を作成した。

- ・ 2005 年度は、SystemC 2.1、TLM(トランザクションレベルモデリング)、合成サブセットのテーマを定め、それぞれ分科会形式で掘り下げた調査を行った。

- ・ 2006年度はTLMに関する動向調査を実施し、結果をSystemCユーザ・フォーラム 2007にて公表。欧州ユーザと比較し、国内ユーザは低抽象度のモデルを利用する傾向が高いことを掴んだ。TLMの標準化の遅れにより再利用性があまり高くないことから、RTL設計に近いレベルでの利用に留まっていると予想される。欧州では標準化を持たずに社内でTLM標準化を行い、一丸となって利用を進めているようである。

- ・ SystemCを用いた高位合成を効果的に行うためには記述スタイルの標準化が望ま しいため、スタイルガイドの骨子を検討し、「合成スタイルガイド構成要件」として まとめ、アニュアルレポートにて公開した。

- ・ 2007年度はSystemCを用いた推奨設計メソドロジについて検討し、合成編について 審議を完了し、アニュアルレポートにて公開した。

- ・ 2008年度は引き続きSystemCを用いた推奨設計メソドロジについて検討し、昨年作成した合成編以外の部分について審議を完了し、本アニュアルレポートにて公開した。

# ③ SystemC 普及活動

- 2004年度より、それまでのOSCIから引き継いでJEITA EDA技術専門委員会の主催でSystemCユーザ・フォーラムを開催している。

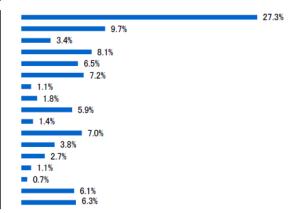

- ・ 2005 年 1 月 27 日に SystemC ユーザ・フォーラム 2005 を開催。受講料は無料。定員 200 名のところ 250 名弱の聴講者が訪れ、立ち見が出るほどの盛況であった。

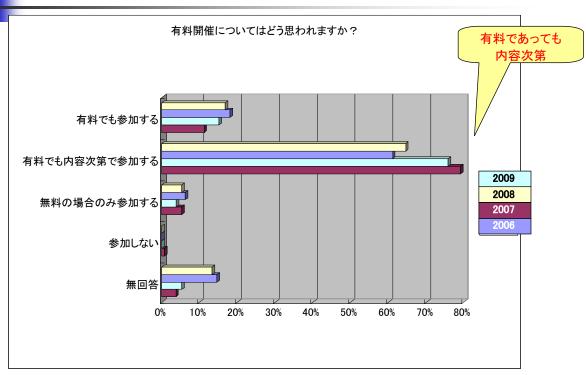

- ・ 2006 年 1 月 27 日に SystemC ユーザ・フォーラム 2006 を開催。今回より、受講料 を徴収することにした。(SystemC 単独の場合¥1,600、SystemVerilog と通しの場 合¥2,000) 定員 200 名のところ、事前予約では満員であったが、実際に会場に訪 れた聴講者は 172 名で前年比 30%減となった。 また、アンケートは 134 名の方に 記入いただけた。

- 2007年1月26日にSystemCユーザ・フォーラム2007を開催。前回より値上げした影響か、聴講者は前年比14%減の148名と減少した。また、アンケートは132名の方に記入いただけた。

- ・ 2008年1月25日に System C ユーザ・フォーラム 2008 を開催。今回は TLM に関するトピックを多くしたせいか、聴講者は前年比12%増の166名となった。また、アンケートは144名の方に記入いただけた。

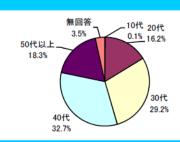

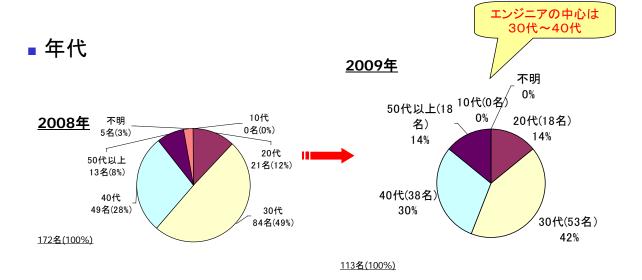

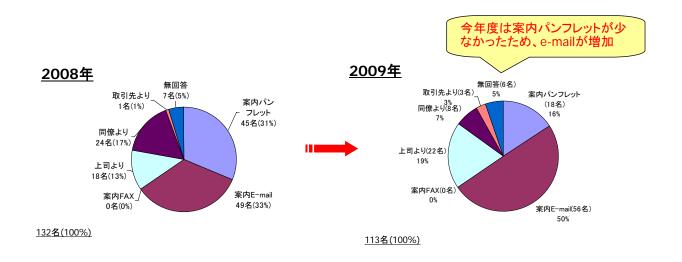

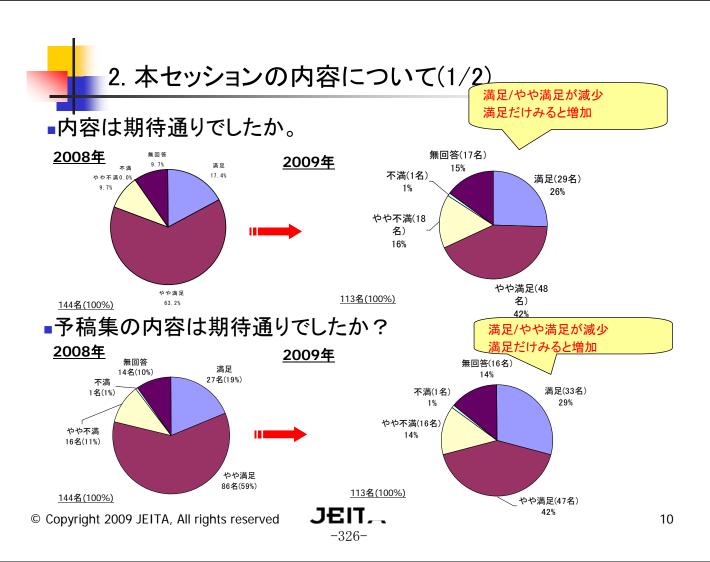

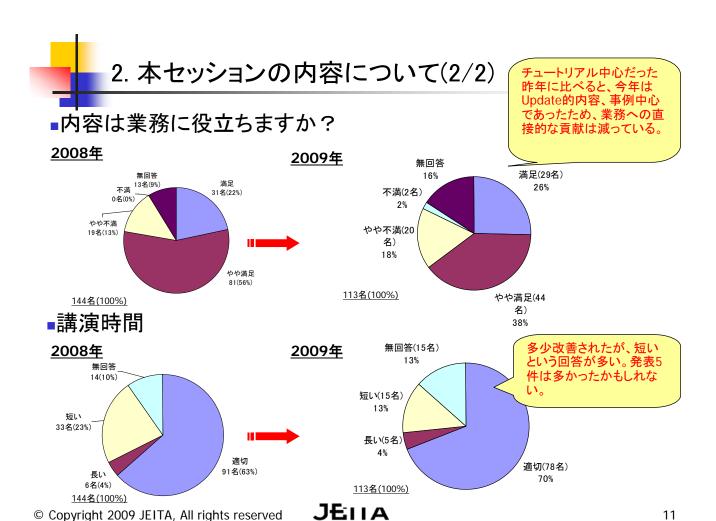

- ・ 2009 年 1 月 23 日に SystemC ユーザ・フォーラム 2009 を開催。今回は聴講者が前年比 26%減の 123 名と大幅に減少した。TLM 2.0 に関しては 2008 年夏に山場を越えており、SystemC そのものにおける大きな変化がなかった点と、景気の悪化もひとつの要因と考えられる。また、アンケートは 113 名の方に記入いただけた。

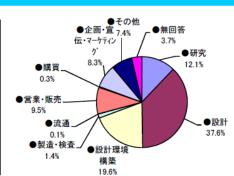

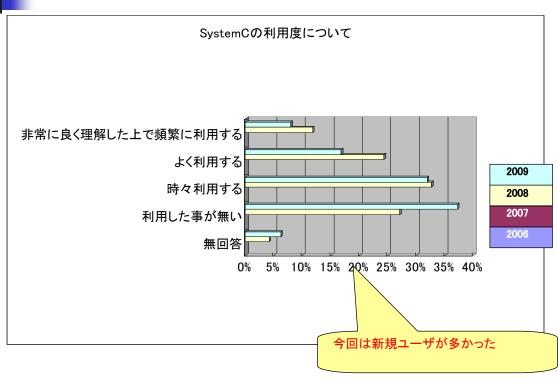

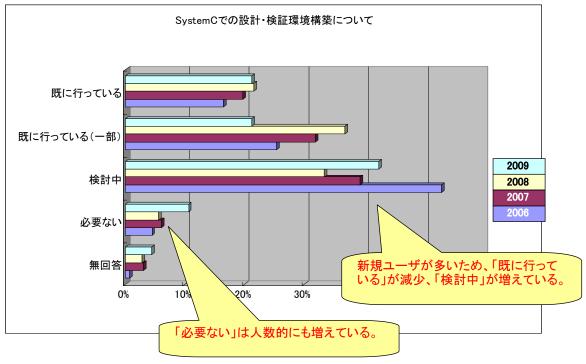

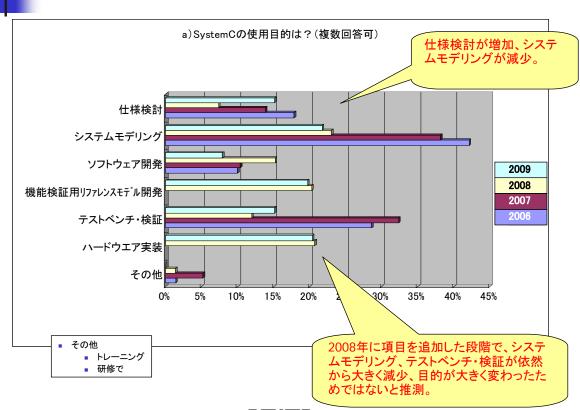

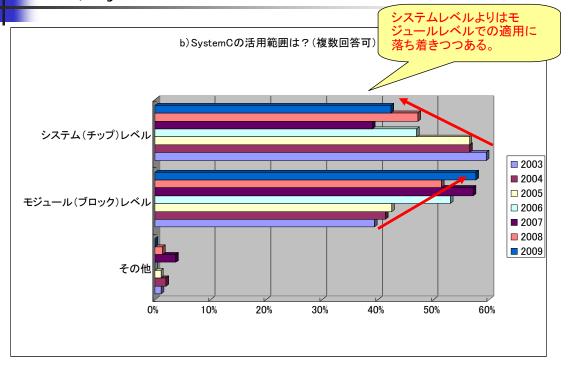

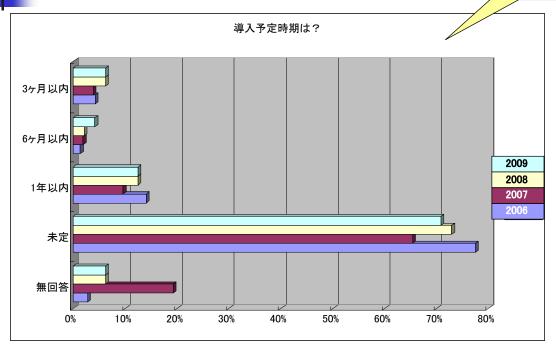

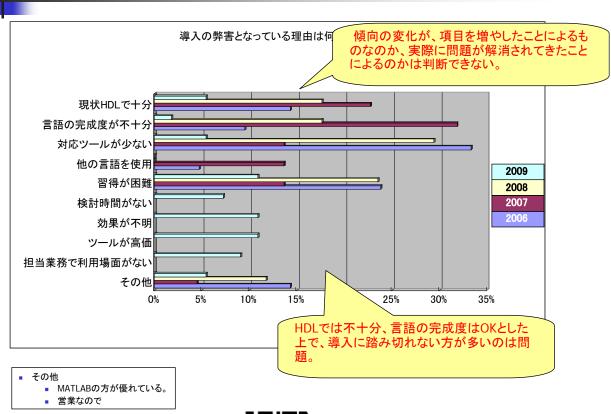

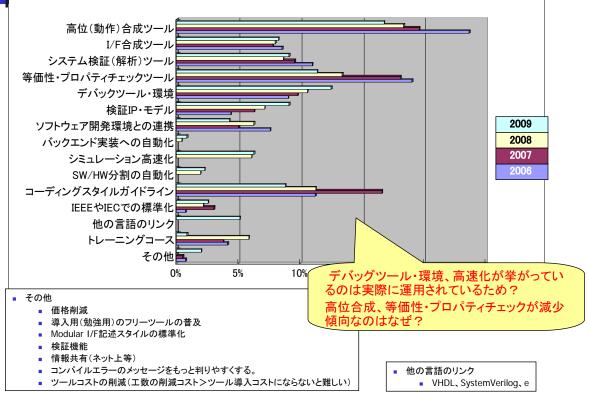

- 2009 年のアンケート調査結果から、次のような事が読み取れた。(詳細については 4.2.6 を参照)

- ▶ 今年度は SystemC の利用経験がない方の参加が多かった。

- ▶ 過去のアンケートで、SystemC を利用しない理由としては、「HDL で十分」「言語の完成度が低い」等の回答があったが、今回のアンケートでは、これらが大幅に減少する一方で、「効果が不明」「検討する時間がない」といった理由が多く挙がった。これについては、本アニュアルレポートにて公開した推奨設計メソドロジが貢献できるものと期待している。

- ➤ TLM の標準化が一段落したこともあり、標準化に対する興味よりは、適用事例に期待して参加する方が多かった。

# (4) 参加メンバー

主査長谷川 隆富士通マイクロエレクトロニクス㈱副主査今井 浩史㈱東芝委員中西 早苗NECエレクトロニクス㈱小島智NECシステムテクノロジー㈱

清水 靖介 OKIセミコンダクタ㈱

長尾文昭三洋半導体㈱柿本勝ソニー㈱

逢坂 孝司 日本ケイデンスデザインシステムズ社

西園寺 修日本シノプシス(株)竹村 和祥パナソニック(株)

牧野 潔 メンターグラフィクスジャパン㈱

大島 良紀㈱ルネサステクノロジ長谷川 裕恭㈱エッチ・ディー・ラボ

東島 清宏 コーウェア(株)

客員 今井 正治 大阪大学

(計 15 名)

#### 2.2.5 SystemVerilog ワーキンググループ

#### (1) 背景

昨今のLSI 設計において、一般的に使用されている Verilog HDL(ハードウエア記述言語)は、特定 ツールの独自言語として開発されたが、その後、OVI (Open Verilog International) による言語仕様 の公開を経て、標準化がなされた。

JEITA (旧 EIAJ) の EDA 技術専門委員会では、当時より Verilog HDL 標準化プロジェクトを設置し、継続的に言語仕様の技術検討・国際標準化に貢献してきた。

VerilogHDL は、1995 年に IEEE1364 として標準化承認がなされ、その 5 年後にはディープサブミクロン対応の機能が盛り込まれ、IEEE1364-2001 として改訂された。

その後、半導体の微細化技術はさらに進化し、1000 万ゲート規模の LSI が開発されるに至り、機能検証の網羅性と検証効率を飛躍的に向上させるために、新しいテストベンチ記述、アサーション/プロパティ記述など、いくつかの検証用言語が実用化された。

SystemVerilog は、Verilog HDLに新たな「デザイン記述構文」の機能追加と、「検証用言語」を追加したものである。デザインにおいて、Verilog HDLに比べ「記述量の削減」や「曖昧性の排除」といったメリットがあり、設計品質の向上が期待される。また検証においては、「網羅性」や「効率」の向上が期待される。Accelleraが、この言語仕様をSystemVerilog V3.1aとしてまとめ、IEEEでの標準化作業を経て、2005年にIEEE1800として標準化された。

現在は、Verilog HDLのIEEE1364 と、SystemVerilogのIEEE1800 をひとつの標準言語として統合するための標準化活動がされており、2009 年度中にIEEE1800 として標準化される計画である。 本ワーキンググループは、2005 年の初のIEEE1800-2005 と IEEE1364 を統合した改訂版IEEE1800-2009の標準化に取組んできた。

#### (2) 目的

日本の半導体業界の要望に沿った形で、SystemVerilog 言語の標準化を進めることが、国内の設計現場での適用容易性を高め、「設計品質の向上」そして「国際的な競争力確保」といった結果につながる。本ワーキンググループでは、業界各社から参加したエキスパートにより、SystemVerilog 言語仕様の技術的な検討を実施し「国際標準化に貢献すること」、SystemVerilog に関する最新の情報収集と発信、「日本国内での SystemVerilog の普及推進を図ること」を目的としている。

#### (3) 活動内容

#### ①グループ結成

03 年 10 月に、SystemVerilog言語仕様の技術検討・標準化を推進するためのタスクグループとして「SystemVerilogタスクグループ」を結成した。07 年度 4 月に「SystemVerilogワーキンググループ」に名前を変更し現在に至る。

#### ②IEEE1800-2005、IEEE1800-2009 言語仕様検討とIssue Listの提出(03~07年度)

IEEE1800-2005 の標準化に対し、04年8月に改善提案を含む32件のIssue List をまとめAccellera と IEEE に提出、IEEE1800-2009の標準化に対しては、07年5月に新たに35件のIssue ListをIEEE に提出した。

各提案については、全件が採択あるいは対応を完了するまで、状況チェックとフォローを実施した。

## ③国際的な情報収集・標準化組織との連携と投票(03~08年度)

04年と07年には、米国で開催された国際学会DVCon(Design & Verification Conference)にメンバを派遣し、最新技術動向の情報収集をおこなうとともに、IEEEのワーキンググループ会議参加により、日本での活動内容を報告した。

また、本ワーキンググループでの活動成果を IEEE の標準化作業に反映するため(提案の優先度をあげ投票権を得る)、IEEE の標準化機関 IEEE-SA に加入した。

そして、05年度、08年度のIEEE1800投票グループに登録し、それぞれ投票を実施した。

#### ④SystemVerilog/SystemCの対訳表の作成(05~06 年度)

SystemVerilog の専門用語に関し、多くの翻訳書や EDA ベンダが提供するユーザマニュアル類で多様な訳語が存在すると利用者の混乱を引き起こすため、標準的な訳語を定義することを目的として対訳表を作成した。SystemC ワーキンググループとも連携し、SystemC と SystemVerilog 共通の対訳表をひとつにまとめた。本対訳表を標準訳語として、出版社・EDA ベンダをはじめ、業界全体に公開し、適用されるよう推進した。対訳表は、2006 年度版アニュアルレポートに「SyetemC/SystemVerilog 専門用語対訳表」として掲載した。

#### ⑤SystemVerilogユーザフォーラムの開催(04~06 年度)

05年、06年、07年の1月に、EDS フェア併設の「システム・デザイン・フォーラム」のカリキュラムのひとつとして「SystemVerilog ユーザ・フォーラム」を3年連続開催した。

このフォーラムでは、Accellera・IEEE p1800-WG の標準化状況の説明、SystemVerilog の特徴・利点を広く周知させるための「SystemVerilog 言語チュートリアル」を3部に分けて実施した。

#### (4) 08 年度の主な活動内容

- ○08年6月 IEEEp1800/Draft5 (英語 1162 ページ)のレビュー35件の指摘・要望のうち、32件が対応済みであることを確認残り3件に対し、追加説明と再要求をIEEEp1800・WG に対して実施

- ○08 年 12 月 IEEEp1800/Draft8 (英語 1162 ページ)のレビュー 35 件の指摘・要望の全件が対応済みであることを確認

# ○08年3月 最終ドラフトを確認し投票を実施

本ワーキンググループは、この IEEE1800-2009 の投票をもって活動を終了した。

本ワーキンググループが IEEEp1800 に提出した Issue List(35 案件とその最新対応状況) を「SVTG-1 IEEEp1800-2009 Issue List」として付録に添付する。

# (6) 参加メンバ

| 主  | 査 | 浜  | П  | 加灵 | 詩美 | 松下電器産業㈱              |

|----|---|----|----|----|----|----------------------|

| 副主 | 查 | 明  | 石  | 貴  | 昭  | 日本シノプシス(株)           |

| 委  | 員 | 湯  | 井  | 丈  | 晴  | ㈱沖ネットワークエルエスアイ       |

|    | 同 | 後  | 藤  | 謙  | 治  | 日本ケイデンス・デザイン・システムズ社  |

| 同  |   | 土  | 屋  | 丈  | 彦  | ㈱東芝                  |

| 同  |   | 竹目 | 日津 | 弘  | 州  | 松下電器産業㈱              |

| 同  |   | 李  |    | 建  | 道  | メンター・グラフィックス・ジャパン(株) |

| 同  |   | 高  | 嶺  | 美  | 夫  | ㈱ルネサステクノロジ           |

| 同  |   | 杉  | 浦  | 正  | 志  | ㈱図研                  |

#### 2.2.6 PowerFormat 検討グループ報告

#### (1) 背景

近年、System-LSI に対する低消費電力化の要求はますます強くなってきている。 バッテリー 駆動の携帯機器用のみならず、環境保護の面から家電製品やサーバー用途に至るまで全ての領域で 低消費電力化は LSI 設計における最大の課題のひとつとなってきた。 一方で、性能向上の要求と プロセスの微細化によるチップあたりの回路規模の増加、さらにはリーク電流の増加が低消費電力 化を困難な問題にしている。

その結果、LSIインプリ時において従来から適用されてきたクロックゲーティングやマルチ Vth といった低消費電力技術に加え、マルチ VDD・パワーゲーティング・バックゲートバイアス等の高度な技術が一般に適用される割合が飛躍的に増加している。

市販のインプリツールでもこれらの技術のサポートが進んできたが、従来の RTL では表現する ことが出来ない電源接続(や分離)に関する情報を記述する共通のフォーマットが設計における重要なポイントのひとつになってきた。

2006 年 6 月、CADENCE 社は 十数社の半導体ベンダー、EDA ベンダーと共に PFI(Power Forward Initiative) を組織し、電源接続やマルチ VDD,パワーゲーティングを表現可能な標準形式 CPF(Common Power Format)を策定した。 一方、SYNOPSYS と MENTOR はこの動きに対抗し、Accellera で UPF(Unified Power Format) を作り、2つの「標準」フォーマットが出来てしまった。

現在、CPF は Si2 にて Rev 1.0 が公開され、CADENCE をはじめとしたインプリツール群で 2007 年初頭からサポートされている。 UPF は Accellera にて Rev 1.0 が公開された後、IEEE に引き継がれ IEEE-P1801 として標準化作業中である。 2007 年終り頃からシノプシス、メンターのツールでのサポートも始まっている。

複数のツール間で電源表現を共通にするべく作成された両フォーマットであるが、ベンダー毎に サポートしている PF (パワーフォーマット) が異なるため、皮肉にもコンバージョンや互換性と いった新たな問題を半導体ベンダーにもたらす結果となった。

## (2) 目的

日本を始め多くの半導体ベンダーでは、複数の EDA ベンダーのツールを使用して LSI 設計を行っているため、2つの「標準」PF の存在は今後障害となることが予想される。 フローのある部分のツールは CPF, 別の部分のツールは UPF が必要となれば、結局フォーマットのコンバージョンが必要となり、手間が減らず互換性も問題となる。

PF を統一し、全てのツールがそれをサポートするのが理想ではあるが、既に CPF/UPF 共に仕様が固まっており、Si2, Accellera 両陣営も統一化に対しては後ろ向きであるため、現時点では非常に難しい。 ツールへの CPU/UPF インプリメントも進んでしまっている状況である為、たとえ今

すぐフォーマットが統一されたとしても全ツールがそのサポートを完了するには1~2年の時間 が必要で、その間はやはり両フォーマット間のコンバージョンが必要となることが予想される。

以上の理由から、早急なフォーマットの統一は目指さず、両フォーマットのインターオペラビリティの確保を第一の目的とする。 また、IEEE P1801 へのフィードバック、投票を行う。

#### (3) 活動内容

ワーキンググループの結成とPF比較表の作成(08年度 下期)

08年10月に開始された IEEE P1801 (UPF) 投票に JEITAとして参加した。 具体的には 各委員によりドラフトをレビューし、特にCPFとのインターオペラビリティ保持の観点から 13件のフィードバック (改善提案を含む) を JEITAとして合意した。 このうち 4 件が採用され、ドラフトの最新版に反映された。

主な活動は以下のミーティングとメーリングリスト上にて実施した。

2008 年 11 月 26 日 第一回ミーティング IEEE P1801 ドラフトへの各社フィードバックすり合わせ、合意

2008年11月27日 IEEE P1801投票

#### (4) 関連機関の動向

IEEE では、P1801 の投票を 2008 年 11 月 27 日(第一回)、 2009 年 01 月 08 日(第二回)を 実施、2009 年 3 月に正式に規格化見込みである。

#### (5) 参加メンバ

主 査 中森 勉 富士通マイクロエレクトロニクス

副主査 南 文裕 東芝

委員安井卓也 パナソニック

同 井上善雄 ルネサステクノロジ

同 中村正昭 三洋半導体

同 熊野義則 リコー

同 山田陽一 セイコーエプソン

同山縣暢英ソニー

同 北原 健 東芝

客 員 神戸尚志 IEC/TC93 国内委員長 (近畿大学)

3. 各種イベント(主催/協賛)報告

#### 3.1 Electronic Design and Solution Fair 2009 (EDSFair 2009)

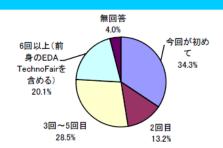

社団法人 電子情報技術産業協会(JEITA) 半導体部会主催により、2009 年 1 月 22 日(木)~23 日(金)の 2 日間、パシフィコ横浜にて、半導体に関連する設計、製造技術の専門性の高い情報を一堂に集めた展示会「Electronic Design and Solution Fair 2009 (略称:EDSFair 2009)」を開催した。

出展社数は、143社、来場者9,117人であった。

今回は、キャッチフレーズを 「未来を設計する!~先端技術を見て、聴いて、感じる2日間~」とし、新しいソリューションが求められる時代に対応した世界最先端技術・サービスの展示とともに、若手技術者向けのオープンセッション、国内外のベンチャー企業を集めたゾーンの設置、産学官の技術交流を深める企画、多彩なコンファレンス等を展開し、広く情報発信を行った。

キーノートスピーチでは、「より速く、より大きく、日本の創造的半導体技術」と題して、テラ・ヘル ツ帯の光通信技術や、損失の少ない送電や給電を研究されてきた、首都大学東京学長の西澤潤一先生にご 登壇いただき、300名が熱心に聴講した。

また、会場内の特設ステージでは、ベンダのエグゼクティブと日本のユーザ(設計者)とのパネルディスカッションを行い、開発現場が抱えているノイズと FPGA/PLD の課題について解決案をぶつけて討論した。また、前回に引続き、『今さら聞けないことがわかる!未来がわかる!』と題した若手エンジニアや元エンジニアの方向けの講演を行った。いずれのセッションも多数の聴衆を集め、立ち見がでるほどであった。

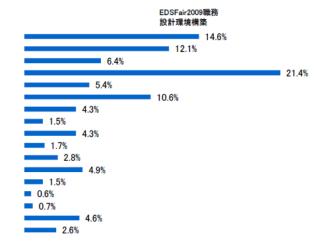

さらに、エンジニアが注目する最新技術やトピックスに関する展示をまとめた特別ゾーンとして、SI/PI/EMC 対策をテーマに、この問題の解決策を展示紹介する、「電磁界解析・SI/PI テクノロジ・ゾーン」、FPGA 関連の出展者を集めた、「FPGA ビレッジ」、近年日本への進出が目覚ましい、インドの半導体設計技術に関連する企業が集結した、「インド・パビリオン」を新たに設置した。また、昨年から引き続き、普段接することが少ない国内外のベンチャー企業のソリューションを集めた「新興ベンダエリア」や、産学官の技術交流を深める大学の研究発表の場となる「ユニバーシティ・プラザ」、EDA 開発に携わる国内のベンチャー企業が一同に集結し、日本企業ならではの「ものづくり力」を活かした技術や製品をアピールする、「JEVeC ビレッジ」の合計 6 つの特別ゾーンを会場内に設置した。

また、日頃多忙な来場者に、効率的、効果的に EDSFair を見学いただくためのサポートサービスとして、消費電力、コスト削減、技術課題を解決するソリューションが一目でわかる案内マップを提供する「コンシェルジュサービス」を新たに企画した。また、海外出展企業を見学希望する来場者に、日本の設計技術・EDA 技術の第一人者が、ツアー・ガイドとしてブースへ同行訪問し、各社の技術紹介・質疑応答を日本語でサポートする「ガイド・ツアー」を「インド・パビリオン」まで拡大させ実施した。各ツアーとも10~20 名の参加者がおり、訪問した新興ベンダからは非常によい企画と好評であり、参加者からも新興ベンダへアクセスするきっかけができたと大変好評であった。

#### 3.1.1 EDSFair2009の概要

(1) 開催期間:2009年1月22日(木)~1月23日(金) 2日間

(2) 場所:パシフィコ横浜(展示ホール、アネックスホール)

(3)主催:社団法人電子情報技術産業協会(JEITA)

協力: Electronic Design Automation Consortium (EDAC)

後援:経済産業省、アメリカ合衆国大使館、外国系半導体商社協会(DAFS)、横浜市経済観光局(順不同)

協賛:社団法人電子情報通信学会(IEICE)、社団法人情報処理学会(IPSJ)、社団法人日本電子回路工業会(JPCA)(順不同)

運営:有限責任中間法人日本エレクトロニクスショー協会 (JESA)

#### (4) 開催概況

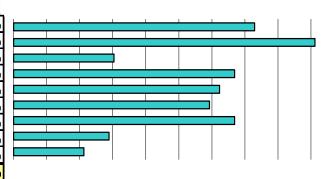

① 入場者数:9,117(前年10,431名)

- ② 出展者数:143 社/317 小間(前年169 社/339 小間)

- ③ 出展者セミナー: 104 セッション、延べ聴講者数 2,070 名(前年 101 セッション、3,225 名)

- ④ スイートルーム:6 社(前年6社)

- ⑤ ユニバーシティ・プラザ:22 ブース、22 大学研究室(前年21ブース、21 大学研究室)

- ⑥ キーノートスピーチ:聴講者数300名(前年355名)

- (7)併催

第 16 回 FPGA/PLD Design Conference: 8 セッション、聴講者数 349 名(前年 8 セッション、 515 名)

9同時開催

システム・デザイン・フォーラム 2009: 2 セッション、聴講者数 216 名(前年 2 セッション、 282 名)

ASP-DAC 2009 (Asia and South Pacific Design Automation Conference)/Designers' Forum

|          | // // // // // // // // // // // // // |        |      |  |

|----------|----------------------------------------|--------|------|--|

|          | 2009年                                  | 2008年  | 率    |  |

| 半導体・電子部品 | 3,747                                  | 4,736  | 79%  |  |

| 機器メーカ    | 2,250                                  | 2,660  | 85%  |  |

| ツールベンダ   | 579                                    | 563    | 103% |  |

| 設計関連サービス | 1,071                                  | 1,095  | 98%  |  |

| 商社・営業    | 437                                    | 428    | 102% |  |

| 出版・マスコミ  | 135                                    | 115    | 117% |  |

| その他      | 898                                    | 834    | 108% |  |

| 計        | 9,117                                  | 10,431 | 87%  |  |

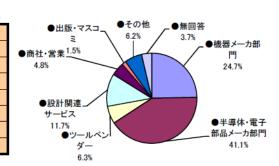

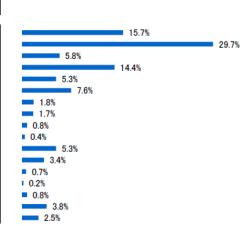

来場者業種内訳

世界経済が低迷する中で、来場者数が昨年より約13%減少し、2日間合計で9,117名となった。 大手電機メーカーが大幅な赤字を発表しい出張規制を行うなど、大変厳しい環境の中での開催となった。

## 3.1.2 出展カテゴリー

- (1)ハードウェア・ソリューション

- システム LSI、ASIC/ASSP、MPU/MCU/DSP、FPGA/PLD デバイス、他

- (2)ハードウェア開発環境(EDA)

- ①EDA/LSI 設計関連ツール

システムレベル設計 (RTL より高位)、論理設計 (RTL~ネットリスト)、論理検証、アナログ設計・検証、レイアウト、レイアウト検証・解析、LSI 信号解析、テスト設計 (DFT/BIST/ATPG など)、DFM 関連 (OPC/RET/PSM/LRC/TCAD など)、ASIC プロトタイピング、他

②PCB/SiP 設計関連ツール

回路図作成、アナログ設計・検証、レイアウト、SI/PI/EMC解析、電磁界解析、熱解析、他

(3)ソフトウェア・ソリューション

組込み OS、デバイスドライバ、ファームウェア、ミドルウェア、仮想開発環境・技術、他

(4)LSI テスト、計測器

LSIテスタ、PCBテスタ、計測器、他

- (5)IP コア、マクロ、セルライブラリ

- (6)組込みプロセッサ開発環境

リコンフィギャラブルプロセッサ、ICE、デバッガ、マイコン CASE、コンパイラ/クロスコンパイラ、シミュレータ、ハード/ソフト協調設計環境、他

(7) 設計サービス関連(LSI/PCB)

デザインセンタ、設計サービス、設計コンサルティング、試作・製造、IP流通サービス、他

- (8)設計インフラ (WS/PC、ネットワーク)

- (9)設計データ管理ツール

設計データ管理ツール、他

- (10)マスクメーカ、ファウンダリメーカ

- (11)大学(研究室)、コンソーシアム

- (12)PR 関連

出版物、他

#### 3.1.3 開会式

1月22日(木)午前9時40分より展示会場入口において開会式を執り行った。開会式への登壇者は次のとおりである。

・ご祝辞・テープカット:

経済産業省商務情報政策局情報通信機器課長 住田孝之様 アメリカ合衆国大使館上席商務官 マーク・ワイルドマン様 横浜市経済観光局長 塚原良一様

・主催者挨拶/テープカット:

社団法人 電子情報技術産業協会 半導体部会 部会長 岡田 晴基 社団法人 電子情報技術産業協会 専務理事 半田力

開会式終了後、登壇者および関係者による会場一巡が行われ、本年は下記のブースを訪問し、新技術・研究開発等の成果の説明をおこなった。

(株) 半導体理工学研究センター(STARC)、日本ケイデンス・デザイン・システムズ社、新興ベンダエリア、(株)図研、ユニバーシティ・プラザ(以上、見学順)

#### 3.1.4 出展者一覧

アーム(株)

(株)アイヴィス

アットデザインリンクス(株)

Accelicon Technologies Inc.

アトレンタ(株)

(株)アノーハ・ソリューションス・/エートップ。テック(株)

アパッチデザインソリューションズ(株)

(株)アプリスター

アルデック・ジャパン(株)

E2 パブリッシング(株)

伊藤忠テクノソリューションズ(株)

日本ヒューレット・パッカード(株)

ネットアップ(株)

日本アイ・ビー・エム(株)

シーティーシー・エスピー(株)

フォーステン・ネットワークス(株)

(株)アノーバ・ソリューションズ

マクニカネットワークス(株)

アジリティ・ジャパン(株)

イノテック(株)

Arteris Inc.

eASIC Corporation

Jazz Semiconductor

Novelics LLC

Rapid Bridge LLC

Target Compiler Technologies N.V.

ATE サービス(株)

Sigrity, Inc.

(株)エッチ・ディー・ラボ

エポック・マイクロエレクトロニクス

(株)沖ネットワークエルエスアイ

カーボン・デザイン・システムズ・ジャパン(株)

兼松エレクトロニクス(株)

カリプト・デザイン・システムズ(株)

コーウェア(株)

コ・フルエント デザイン

(株)コスモス・コーポレイション

CvberTec(株)

Jasper Design Automation

サイバネットシステム(株)

サン・マイクロシステムズ(株)

シーケンスデザイン(株)

情報処理装置等電波障害自主規制協議会

(株)シルバコ・ジャパン

(株)図研

NEC システムテクノロジー(株)

(株)スピナカー・システムズ

ベリフィック・デザイン・オートメーション

シリコン・デザイン・ソリューションズ

スプリングソフト(株)(旧社名; ノバフロー(株))

スペイシャル

タナーリサーチジャパン(株)

ChipVision Design Systems

DSM ソリューションズ(株)

Prolifi c,Inc.

DeFacTo Technologies SA

DCG システムズ(株)

デナリソフトウエア(株)

(株)電波新聞社

日経 BP 社

日本イヴ(株)

日本ケイデンス・デザイン・システムズ社

イノテック(株)

日本シノプシス (株)

日本ヒューレット・パッカード(株)

(株)ノア

LogicVision, Inc.

Nascentric, Inc.

Javelin Design Automation

Berkeley Design Automation, Inc.

パルシックジャパンリミテッド

(株)半導体理工学研究センター(STARC)

日立情報通信エンジニアリング(株)

フォルテ・デザイン・システムズ(株)

(財)福岡県産業·科学技術振興財団

マグマ・デザイン・オートメーション(株)

三菱電機エンジニアリング(株)

MunEDA GmbH

メンター・グラフィックス・ジャパン(株)

(株)モーデック

リード・ビジネス・インフォメーション(株)

OneSpin Solutions Japan K.K.

電磁界解析・SI/PI テクノロジ・ゾーン

アジレント・テクノロジー(株)

アンソフト・ジャパン(株)

(株)エーイーティー

日本ケイデンス・デザイン・システムズ社

PHYSWARE INC

HELIC, Inc.

FPGA ビレッジ/特定非営利活動法人 FPGA コンソーシアム

(株)アルティマ

特定非営利活動法人 FPGA コンソーシアム

**匠ソリューションズ(株)**

立野電脳(株)

東京エレクトロン デバイス(株)

(株)トーメンエレクトロニクス

特殊電子回路(株)

(有) ヒューマンデータ

富士エレクトロニクス(株)

プロトタイピング・ジャパン(株)

三菱電機マイコン機器ソフトウエア(株)

菱洋エレクトロ(株)

インドパビリオン

泉ネットワーク(有)

Wipro Limited

Kitatec KK.

コスミック・サーキット

Zensar technologies Ltd. & Zensar Advanced

technologies Co.

ナレッジアイティ(株)

ハ゜トゥニ・コンヒ゜ューター・システムス゛・リミテット゛

IC サービス (株)

新興ベンダエリア

**Analog Rails**

ALTOS DESIGN AUTOMATION

Incentia Design Systems, Inc.

EDXACT SA

nSys Design Systems Pvt Ltd

ENTASYS DESIGN, INC.

ENVIS CORPORATION

CONCEPT ENGINEERING GMBH

Certicom

Sidense Corp.

CLK DESIGN AUTOMATION, INC.

シリコン・フロントライン・テクノロジー (株)

シンテスト・ジャパン

SYNFORA

Z Circuit Automation

SOLIDO DESIGN AUTOMATION

DUOLOG TECHNOLOGIES

Dorado Design Automation, Inc.

Nangate

Pextra Corporation

POLYTEDA Software Corporation

Micrologic Design Automation Inc.

メガシス(株)

Rapid Bridge LLC

リアルインテント社

JEVeC ビレッジ

(株)アストロン

(株)礎デザインオートメーション

エイシップ・ソリューションズ(株)

ギガヘルツテクノロジー(株)

ケイレックス・テクノロジー(株)

(株)ジーダット

(株)ジェム・デザイン・テクノロジーズ

(株)システム・ジェイディー

(株)数理システム

TOOL(株)

日本 EDA ベンチャー連絡会(JEVeC)

50 音順 (※一字下げは共同出展)

#### 3.1.5 出展傾向

EDSFair2009 は、出展者数が 143 社となった。

|       | 出展者数  | 小間数    |

|-------|-------|--------|

| 2009年 | 143 社 | 317 小間 |

| 2008年 | 169 社 | 339 小間 |

| 2007年 | 154 社 | 348 小間 |

| 2006年 | 148 社 | 343 小間 |

| 2005年 | 119 社 | 336 小間 |

| 2004年 | 104 社 | 306 小間 |

| 2003年 | 99 社  | 320 小間 |

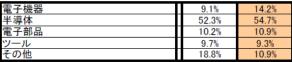

|                 | 2009年 |        | 2008年 |        |

|-----------------|-------|--------|-------|--------|

|                 | 社数    | 小間数    | 社数    | 小間数    |

| 通常出展            | 107 社 | 278 小間 | 115 社 | 294 小間 |

| 新興ベンダ (ブース) 出展) | 36 社  | 39 小間  | 54 社  | 45 小間  |

厳しい環境の中で、出展者数・小間数ともに大変厳しい数字となったが、新規出展者数は 35 社と昨年 の 29 社を上回った。また、今年の大きな特徴として、申込後のキャンセルが続いた。最終的に 7 社 10 小間がキャンセルとなった。

# 3.1.6 出展者セミナー

1 セッション 45 分間で、 $30\sim100$  名の適正人数のお客様に向けて集中 PR が行える出展者セミナールームを提供した。2009 年は 10 会場にて 104 セッションを開催した。

聴講者数: 2,070 名

#### 3.1.7 キーノートスピーチ

ーより速く、より大きく、日本の創造的半導体技術ー 首都大学東京 学長

#### 西澤 潤一

- (1) 日 時:1月22日(木)10:30~11:30

- (2) 場 所:アネックスホール

- (3) 聴講料:無料

- (4) 聴講者数: 300 名

#### 3.1.8 第 16 回 FPGA/PLD Design Conference

(1) 日 時:1月22日(木)·23日(金)

(2) 場 所:アネックスホール

(3) 聴講料:事前申込:10,500円(1日券)※消費税込

当日申込:12,600円(1日券)※消費税込

#### 聴講者数:

| セッション 1 | 53名  | セッション 5 | 37 名 |

|---------|------|---------|------|

| セッション 2 | 55 名 | セッション 6 | 35 名 |

| セッション 3 | 56 名 | セッション 7 | 38 名 |

| セッション 4 | 46 名 | セッション 8 | 29 名 |

EDSFair と併設の第 16 回 FPGA/PLD Design Conference が 1 月 22 日 (木) と 23 日 (金) の両日、アネックスホールにて開催され、全 8 セッションで合計 349 名の聴講者を集めた。

#### 1月22日(木)

セッション1 (10:00~11:20)

CPLD/FPGA の基礎と活用方法

大木 真一氏

[(株)武蔵野電波 / 東海大学 専門職大学院]

セッション2 (11:35~12:55)

FPGA 回路設計初心者のための開発トラブルシューティング

豊岡 治宏 氏

[三菱電機マイコン機器ソフトウエア(株) 第3事業部 開拓部 開拓第1課主査]

セッション3 (14:05~15:25)

FPGA に搭載された専用機能を有効活用する~RAM/MAC/PLL/DCM/SerialIO~ 井倉 将実 氏

[来栖川電工(有) 応用技術部 技術取締役]

セッション4 (15:40~17:00)

FPGAに CPU を搭載し、オリジナル SoC を実現する

~ FPGA を中心とした組み込みシステムの開発 ~

実吉 智裕 氏

[株式会社アットマークテクノ 代表取締役]

#### 1月23日(金)

セッション5 (10:00~11:20)

FPGA 高速 I/O を設計力で使いこなす ~DDR メモリ I/F, LVDS, PCI-Express の設計ポイント~ 櫻井 剛 氏

[三精システム株式会社 第1設計部 部長補佐]

セッション6 (11:35~12:55)

安心できる、高速 IO 系の基板設計初歩の初歩

金子 俊之 氏

[株式会社トッパン NEC サーキットソリューションズ 技術開発本部 設計部 スーパーバイザー]

セッション7 (14:05~15:25)

System Verilog による FPGA 設計

岩本 正美 氏

[匠ソリューションズ株式会社 代表取締役社長]

セッション8 (15:40~17:00)

プログラマブル・システム LSI 時代の到来 ・ 続々登場のミックスド・シグナル LSI の技術動向 三上 廉司 氏

[日本サイプレス(株) マーケティング・マネジャー]

#### 3.1.9 特別ゾーン

新企画:電磁界解析・SI/PI テクノロジ・ゾーン

いまや全ての設計者にとって必須の知識となった SI/PI/EMC 対策をテーマに取り上げた、「ここまでできる!最新電磁界シミュレーション技術と SI/PI/EMC 対策」テクノロジ・ゾーンは、基板上の信号劣化要因に対するソリューションを提供する電磁界解析ツール・ベンダおよびその関連企業が一同に集まりこの問題の解決策を展示、紹介した。

#### 出展者:

アジレント・テクノロジー(株) アンソフト・ジャパン(株) (株)エーイーティー 日本ケイデンス・デザイン・システムズ社 PHYSWARE INC Helic, Inc.

また、ゾーンに併設されたミニ・ステージにおいてシステム機器ユーザが SI/PI/EMC の課題に対する取組みをプレゼンテーション形式で紹介した。

- ◆1月22日(木) 12:00~12:20(19名)、15:00~15:20(28名) プレゼンター:パナソニックエレクトロニックデバイス株式会社 デバイスアプリケーションセンター 顧問 越智 敏 氏

- ◆1月23日(金) 13:00~13:20(44名)、15:10~15:30(42名) プレゼンター:ソニー(株)モノ造り本部 モノ造り技術部門 技術開発室 担当部長 村山 敏夫 氏

下記ゾーン参加者による、自社ソリューションを紹介するプレゼンテーションも両日行なわれた。 (22 日 5 回 合計 62 名、23 日 7 回 合計 121 名)

- 高速ディジタル信号の解析に最適な MW STUDIO による時間領域シミュレーション (株) エーイーティー

- Allegro にタイトに統合された、EMS 2D フルウェーブ・フィールドソルバ 日本ケイデンス・デザイン・システムズ社

- シミュレーションで設計期間短縮 アンソフトの SI、PI、EMI ソリューション アンソフト・ジャパン (株)

- High Speed, high capacity, true-parallel, 3D full-wave solution for chip-package-board SI, PI and EMI

パラレル処理と独自のアルゴリズムにより、フル・ウエーブ 3D フィールド・ソルバを実現した Physware のシグナルおよびパワー・インテグリティと電磁界解析のソフト PHYSWARE INC

■ An inductance aware RFIC design flow

VeloceRF によるプロセス設計キット(PDK)に統合したスパイラル・インダクタ自動生成及び伝送路 やインダクタ間で起きる相互インダクタンス解析ソリューション Helic, Inc.

# 新企画: FPGA ビレッジ

出展者を集めた、FPGA ゾーンを設置した。

また、FPGA/PLD Design Conference 実行委員会の協力のもと、特設ステージにおいてエグゼクティブセッションも開催した。

1月22日 (木): 15:45~17:15 『FPGA/PLD の未来と課題を探る』 ~ユーザの視点から FPGA/PLD の未来予測~

出展者:

(株)アルティマ

特定非営利活動法人 FPGA コンソーシアム

匠ソリューションズ(株)

立野電脳(株)

東京エレクトロンデバイス(株)

(株)トーメンエレクトロニクス

特殊電子回路(株)

(有)ヒューマンデータ

富士エレクトロニクス(株)

プロトタイピングジャパン(株)

三菱電機マイコン機器ソフトウエア(株)

菱洋エレクトロ(株)

## 新企画:インドパビリオン

近年、日本への進出が目覚ましい、インドの半導体設計技術に関連する企業が集結した、パビリオンを設置した。効率よくインド企業の最新情報、技術の見学が可能となった。

#### 出展者:

Izumi Network Yugen Kaisha

Wipro Limited

Kitatec KK.

コスミック・サーキット

Zensar technologies Ltd. & Zensar Advanced technologies Co

ナレッジアイティ(株)

Patni Computer Systems Ltd

#### 新興ベンダエリア

国内外新興企業 25 社の最新ソリューションが集まり、設計開発者向けに最新情報を紹介した。

#### 出展者:

IC サービス(株)

**Analog Rails**

ALTOS DESIGN AUTOMATION

Incentia Design Systems, Inc.

**EDXACT SA**

ENTASYS DESIGN, INC.

CONCEPT ENGINEERING GMBH

Sidense Corp.

Certicom

CLK DESIGN AUTOMATION. INC.

Silicon Frontline Technology, Inc.

シンテスト・ジャパン

**DUOLOG TECHNOLOGIES**

Z Circuit Automation

SOLIDO DESIGN AUTOMATION

#### **SYNFORA**

Dorado Design Automation, Inc.

nSys Design Systems Pvt Ltd

Nangate

Pextra Corporation

POLYTEDA Software Corporation

Micrologic Design Automation Inc.

メガシス(株)

Rapid Bridge LLC

Real Intent, Inc.

# JEVeC ビレッジ

日本の EDA の発展を目指して設立された「日本 EDA ベンチャー連絡会(JEVeC)」との協力による特別企画。EDA 開発に携わる国内のベンチャー企業が一同に集結し、日本企業ならではの「ものづくり力」を活かした技術や製品をアピールした。

#### 出展者:

(株)アストロン

(株)礎デザインオートメーション

エイシップ・ソリューションズ(株)

ギガヘルツテクノロジー(株)

ケイレックス・テクノロジー(株)

(株)ジーダット

(株)ジェム・デザイン・テクノロジーズ

(株)システム・ジェイディー

(株)数理システム

TOOL(株)

日本 EDA ベンチャー連絡会(JEVeC)

#### ユニバーシティ・プラザ

産学の交流を促進すると共に、大学研究機関による研究成果を発表する場とする企画である。設計技術 に関する研究成果を発表実演した。

#### 22 大学研究室

■ VLSI における新しい故障モデルに基づく故障検査法の開発

愛媛大学 大学院理工学研究科 電子情報工学専攻 情報システム工学講座研究室

■ ユビキタス・センサネットワーク向き低消費電力プロセッサ

大阪大学 大学院情報科学研究科 情報システム工学専攻 集積システム設計学講座 今井研究室

■ ディペンダブル再構成可能アーキテクチャとばらつき考慮設計技術

大阪大学 大学院情報科学研究科 情報システム工学専攻 尾上・橋本研究室

■ パターンマッチング回路の合成と応用について

九州工業大学 情報工学研究院 電子情報工学研究系 笹尾研究室

■ LSI 低消費電力テスト技術

九州工業大学 情報工学府 梶原 · 温研究室

■ アナログ LSI 回路設計自動化環境の構築

九州工業大学 マイクロ化総合技術センター 中村研究室

■ 高性能・低電力システム LSI アーキテクチャとその電力削減手法

九州大学 システム LSI 研究センター

■ 耐ソフトエラー設計支援ツールの開発

九州大学 大学院システム情報科学研究院 情報工学部門 安浦・松永・吉村研究室 九州大学 システム LSI 研究センター

豊橋技術科学大学 工学部 情報工学系 組込みシステム研究室

■ 次世代リコンフィギャラブルロジックとその設計支援技術

熊本大学 工学部 情報電気電子工学科/大学院自然科学研究科 情報電気電子工学専攻 末吉研究室

■ インテリジェント・ユビキタスセンサーLSI 技術

神戸大学 工学研究科 情報知能学専攻 プロセッサ・アーキテクチャ研究室

■ 高シグナルインテグリティ信号波形整形技術

筑波大学 システム情報工学研究科 コンピュータサイエンス専攻 安永研究室(集積システム研究室)

■ 動的再構成可能 LSI を活用したシステム構築および技術応用

筑波大学 大学院システム情報工学研究科 コンピュータサイエンス専攻 高度 IT 人材育成のための実践的ソフトウェア開発専修プログラム

■ LSI 設計のための開発環境

東海大学 専門職大学院 組込み技術研究科 清水尚彦研究室

■ キテレツ・アイディア・コンペ

東京工業高等専門学校

■ VDEC の活動紹介

東京大学 大規模集積システム設計教育研究センター

■ システムレベル設計記述の検証・デバッグ支援技術

東京大学 工学部電気電子工学科 藤田研究室

■ 組込み RTOS 向けアプリケーションの開発支援に関する研究報告 〜実行時ログの見える化〜 名古屋大学 大学院情報科学研究科 情報システム学専攻 高田・冨山研究室

■ ディジットシリアル演算を用いた再構成型プロセッサと科学技術用エンジンの紹介

広島市立大学 大学院情報科学研究科 情報工学専攻 コンピュータアーキテクチャ研究室

■ FPGA を用いたハイパフォーマンスコンピューティング

広島市立大学 大学院情報科学研究科 情報工学専攻 論理回路システム研究室

■ ダイナミック・アーキテクチャ型細粒度並列処理

広島市立大学 情報科学部 情報工学専攻 高橋隆一研究室

■ 多層プリント配線基板設計支援システム MULTI-PRIDE

広島大学 大学院工学研究科 情報工学専攻 アルゴリズム論研究室

■ FPGA を用いたシステム実現 --- エステティック・フィルタ, PLC, 高信頼性回路の実現 --- 明治大学 理工学部 情報科学科 理工学研究科 基礎理工学専攻 情報科学系 井口研究室

#### 新興ベンダプレゼンテーション

会場内に設置の特設ステージでは、国内外新興企業が、次々とプレゼンテーションを行った。

#### ◆1月22日

$12:00\sim 12:20$

Ultra-fast Characterization and library validation.

(206)Altos Design Automation,Inc. Mr.Jim McCanny CEO

**CDC** Venfication

(118) REAL INTENT, INC.

Mr. Naoto Kimura, Director, FAE Japan

#### ◆1月23日

$12:00\sim 12:20$

システム設計者のためのノイズ対策の勘どころ

(410)ギガヘルツテクノロジー株式会社

河村 隆二 氏, 代表取締役

## ケイレックスがご提供する EDA サービスのご 紹介

(412)ケイレックス・テクノロジー株式会社 今井 広明 氏,営業部長

$12:20\sim 12:40$

STILAccess(TM)によるテストコスト削減事例

(413)株式会社システム・ジェイディー

伊達 博 氏, 代表取締役

#### SiP Feasibility Study, Before CAD.

(411)Gem Design Technologies, Inc.

Mr.Hiroshi Murata, President

Anti-Counterfeiting: SOC Digital Content Protection and Management

(113)Certicom

Mr.Craig Rawlings,

Senior Director Product Management

$15:30\sim15:50$

Translation Service from India

(018)Izumi Network Yugen Kaisha

Mr.Hiroyuki Kanae

India IT Club

(020)Kitatec K.K.

Mr.Harsh Obrai

$15:10\sim15:40$

Functional ECO & MMMC Timing ECO

(120)Dorado Design Automation, Inc.

Mr.J.J. Hsiao. Executive VP

# PICO EXTREME-THE MOIST ADVANCED ALGORITHM SYNTHESIS

(112)SYNFORA

Mr.Atsushi Uria, Director of Technical Support

**DUOLOG's Chip Integration Platform**

(108) DUOLOG TECHNOLOGIES

Mr.Brian Clinton, Product Manager

$13:10\sim 13:30$

Micrologic Design Automation

(212)Micrologic Design Automation Mr.Danny Rittman PHD, CTO

#### Parasitics Analysis and Management

(109)EDXACT SA

Mr.Daniel Borgraeve, VP Sales

$13:30\sim 13:50$

# Automated Standard Cell Library Creation and Optimization

(210)Nangate

Mr. Yutaka Kumagai,

Partner Cubic Micro (Nangate

Representative)

$15:50\sim16:10$

情報共有化基盤(インテリジェント Hub)機能付き SaaS サービス

(019)The Knowledge IT 株式会社 ヘアント セティア 氏, 代表取締役

Process Variation Solutions for Transistor-Level Designers

(116)SOLIDO DESIGN AUTOMATION

Mr.Johnson Lau, Senior Director

#### 3.1.10 ガイド・ツアー

日本の設計技術・EDA 技術の第一人者が、ツアー・ガイドとしてブースへ同行訪問し、各社の技術紹介・質疑応答を日本語でサポートする「ガイド・ツアー」を「インド・パビリオン」まで拡大させ実施した。

□新興ベンダ・ツアー参加企業:19社

内訳:米国企業:9社、カナダ企業:3社、独企業:1社、アイルランド企業:1社 インド企業:1社、韓国企業:1社、仏企業:1社、デンマーク:1社、台湾企業:1社

実施回数:1月22日2回、1月23日2回

ツアー参加人数:各ツアーとも5-20名

□インドパビリオン・ツアー参加企業:6社 実施回数:1月23日1回 ツアー参加人数:30名弱

EDSFair2009では、ツアー方式のブース訪問を企画。ツアー・ガイドが引率して海外新興ベンダのブースを訪問、コミュニケーションのサポートを日本語で行うことにより、来場者が新興ベンダの技術を理解しやすいように支援を行った。

新興ベンダ・ガイド・ツアーでは、二人の設計技術のエキスパートがツアー・ガイドを努めた。1月22日は、米国D2S, Incの日本代表の吉田憲司氏、23日は、東芝のシステムLSI設計技術部長の樋渡有氏である。二人とも、LSI設計技術やEDAに精通し、講演経験も豊富なベテランである。また、インドパビリオン・ツアーには、インド電子機器コンピュータソフトウェア輸出振興会(ESC)日本代表のジェネシス株式会社代表取締役、西山 征夫 氏であった。

新興ベンダ・ガイド・ツアーおよびインドパビリオン・ツアーは、まず特設ステージにおいて、ツアー・ガイドによりツアーで訪問するベンダの企業紹介が行われ、各ベンダの代表者もステージ上で紹介した。ブース訪問に先立って、ベンダがどのような会社か、特徴とする製品や技術は何かを事前に理解してもらった。 企業紹介のスライドも日本語で準備されていたので、参加者にとっては、ブース訪問前にベンダについてある程度の知識を得ることができた。 ステージでの企業紹介が一通り終わると、ガイド・ツアーの旗のもと、ツアー・ガイドを先頭に紹介されたベンダのブースを訪問した。

各ブースでは、最初そのベンダの代表がパネルや、PCを使って製品や技術をさらに紹介。中には、日本語デモや、パンフレットなどの資料を準備していた企業もあり、出展者としてもこのツアーによるブース来場者を期待していた様子が見受けられた。 ツアー・ガイドは、必要に応じてベンダの説明を日本語に訳したり、また Q&A では参加者が聞きたいであろう質問を代わって行ったり、日本語でなされた質問を英語で伝えたり、また、回答を日本語で伝えたりと、ツアー参加者の技術の理解のためのコミュニーケションのサポートを行っていた。

各ツアーは、大まかに設計分野ごとでまとめられ各ツアーとも毎回 10-20 名の参加者があり、盛況であった。

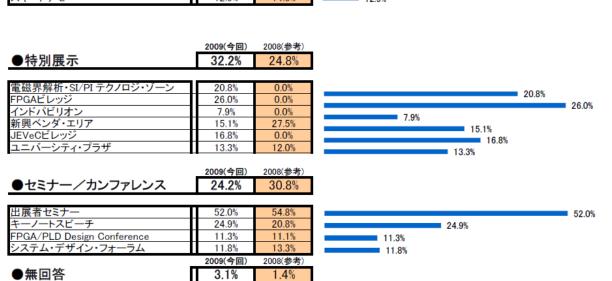

#### 3.1.11 特設ステージ

場 所:展示フロア内特設ステージ 参加無料

展示会場内の特設ステージにて、昨年に続いて、ベンダーエグゼクティブを迎えての「エグゼクティブが語る!」3セッションと「今さら聞けないことがわかる!未来がわかる!」2セッションを開催し、二日間で計1049名の聴講者を集めた。「エグゼクティブが語る!」ではLSI設計とPCB設計にまたがる技術課題をとりあげたセッション1、FPGAコンファレンスとの連携によるFPGA関連セッション、そして、半導体ベンダー2社のエグゼクティブとメディアのエグゼクティブを迎えて電子産業の将来とEDA技術をとりあげたセッションを開催した。「今さら聞けない・・」では「高位合成」と「検証メソドロジ」につき、対話式講義と講演により、それぞれ注目の先端技術につき、基礎から設計適用事例までが紹介された。

今年度は EDSF 実行委員会の他の WG との連携により、特設ステージのセッションテーマと関連した展示エリアの取り組み(セッション1のテーマと関連したテクノロジーテーマゾーンの設置、セッション2に関連して FPGA パビリオン)も行われ、EDSFair 全体の一体感を示すとともに、来場誘致に貢献できた。また、特設ステージ企画 WG メンバとして、EDA 技術専門委員会と EDSF 実行委員会の EDA ベンダ委員の参加を頂き、それぞれセッションオーガナイザとして、活動頂いた。

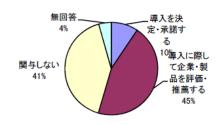

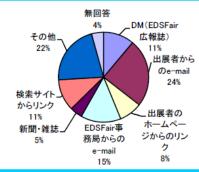

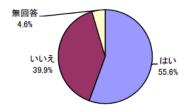

EDSFair2009 来場者アンケートによると、来場者の約3分の1は特設ステージを来場目的にあげており、目的達成度も回答数中44%と否達成12%を大きく上回った。自由記入でも、「特設ステージは企画がよく、いろいろな意見を聞くことができた」など積極的評価の記載が5件と、他のセミナなどとの時間割の整合と、客席の窮屈度の2件の改善要望の記載を上回った。

資料スライドの操作、スクリーンを指示するポインタ、各セッションの時間管理などの運営面の反省点は、次年度委員に引き継ぎ、改善をお願いする。

以下、各セッション毎に、企画概要(開催案内)と、実施結果として、聴講数と簡単なコメントを記載 する。

#### 1月22日(木)

- ■『エグゼクティブが語る!』

- □13:00~14:30 セッション1 日英同時通訳付き

#### 「ノイズに悩まされない設計の実現に向けて ~ LSI 設計・PCB 設計・EDA ツールで、今すべきこと ~」

『LSI を PCB に実装したら想定外の電気的ノイズトラブルが発生した』こんな声をよく聞くようになってきたのは、なぜか? その原因は? どうしたら未然に防げるのか? このステージでは、LSI 設計と PCB 設計にまたがる課題を認識し、解決への道筋を探ります。

Dr. Dian Yang [Apache Design Solutions, Inc., SVP, Product Management]

Mr. A. J Incorvia [Cadence Design Systems, Inc., VP, Research and Development]

仮屋 和浩 氏 [(株) 図研 取締役 技術本部長]

中村 篤氏 「(株) ルネサステクノロジ]

福場 義憲 氏 [東芝セミコンダクター社 システム LSI 事業部 カスタム SoC 応用設計技術部]

金子 俊之 氏 [(株) トッパン NEC サーキットソリューションズ 技術開発本部 設計部]

【司 会】 小島 郁太郎 氏 「㈱日経 BP 社]

【オーガナイザ】 南 文裕氏 [東芝マイクロエレクトロニクス㈱]

聴講者数 : 225名

オーガナイザ、司会者の周到な準備により、特設ステージの開幕にふさわしい、活発なセッションであった。会場からも多数の質問がでた。チップ、パッケージ、PCBの各設計間の協力連携が今後、ますます重要となる。会場からの質問にもあった、設計データの、共通化・標準化あるいは相互乗り入れへの取り組みの進展を期待したい。

□15:45~17:15 セッション 2 日英同時通訳付き

## 「FPGA/PLD の未来と課題を探る~ユーザの視点から FPGA/PLD の未来予測~」

近年、FPGA/PLD は製品づくりに不可欠なデバイスとして日本市場でも認知されつつあります。その FPGA/PLD に今後どのような成長を求め期待するのか、ユーザの視点から技術面、経済面として将来の製品に求められるソリューションを提起します。そして、それに対して、デバイスベンダー、EDA ベンダーとともに、FPGA/PLD のあるべき姿を探りながら課題を議論し、日本市場における FPGA/PLD の未来を予測します。

Mr. Danny Biran [Altera Corporation, SVP, Product & Corporate Marketing]

小島 洋一 氏 [ザイリンクス(株), フィールドアプリケーションエンジニアリング本部 本部長]

Mr. Gary Meyers [Synopsys, Inc., VP & GM, Synplicity Business Group]

Mr. Simon Bloch [Mentor Graphics Corp., VP & GM, Design and Synthesis Division]

山本 靖氏 [山本靖 & アソシエーツ]

松本 仁氏 [三菱電機(株)コミュニケーション製作所 光技術 G]

【司 会】 弘中 哲夫 教授 [広島市立大学 大学院 情報科学研究科]

【オーガナイザ】 松本 仁氏 [三菱電機(株)コミュニケーション製作所]

聴講者数 : 140名

5 つの特設ステージセッション中では唯一聴講数が 100 人台だったのは残念だったが、ここ数年 EDSF への展示がない 2 大 FPGA ベンダのエグゼクティブと、関連 EDA ベンダーエグゼクティブの参加のもと、

国内 FPGA ユーザ代表とのパネル討論は FPGA/PLD の未来と課題を探るよい機会となった。

#### 1月23日(金)

■『エグゼクティブが語る!』

□10:30~11:30 セッション3

## 「電子産業の成長シナリオと EDA 業界の役割」

日本の電子産業の将来像を、「携帯電話・情報家電・パソコンなどの既存製品の将来性」「環境やエネルギー問題へ向けた新製品・ビジネスモデルの創出」「MEMS など次世代技術の将来性」といった視点から語りあって頂きます。日々、難しい技術課題にとりくまれるエンジニア、管理職の方にも参考になる話が山盛りです。

望月 洋介 氏 「日経 BP 社 電子・企画局 局長補佐]

野口 達夫 氏 「東芝セミコンダクター社 技師長]

福間 雅夫氏 「NECエレクトロニクス(株)執行役員]

【司 会】 高野 一郎 氏 「㈱テクノアソシエーツ 代表取締役社長]

【オーガナイザ】 荒木 大 氏 [㈱インターデザイン・テクノロジー]

聴講者数 : 218名

設計や EDA の個々の技術ではなく、半導体ビジネスの視点から技術を語るセッションを、半導体ベンダエグゼクティブ (2名) の参加を得て開催したのは、今回、初めての取り組みである。世界不況の中、半導体業界も非常に厳しい状況にあるが、このような場での業界および、関連業界関係者への発信はぜひ今後も続けてほしいものである。

- ■『今さら聞けないことがわかる!未来がわかる!』

- □ 14:00~15:00 セッション4

#### 「今さら聞けない高位合成 ~一から学ぶ高位合成~」

最近高位合成を用いた設計事例の紹介が聞かれるようになったけど、本当はどうなの?どこまでできるの?

ここでは、高位合成を改めて理解するために、高位合成の仕組み、特長、適用範囲を設計事例も含め対話 形式でレクチャー。生徒と先生の学習シリーズ第3弾で高位合成をわかりやすくお伝え致します。

山田 晃久 氏 [シャープ㈱電子デバイス事業本部]

【聞き手】 銭 岩 氏 [シャープ㈱電子デバイス事業本部]

【司 会】 西本 猛史 氏 「シャープ㈱電子デバイス事業本部】

【オーガナイザ】 西本 猛史 氏 [シャープ㈱電子デバイス事業本部]

聴講者数 : 263名

5 セッション中、聴講数が最大で、高位合成に対する関心の高さが伺えた。高位合成の基本的な技術と、設計からみた動作レベル設計と RTL 設計の違いなどの説明から、実際の LSI 設計への適用事例まで、高位合成のエキスパートである講師の説明と、生徒役の若手エンジニアからの質問でわかりやすく紹介された。

#### □16:15~17:15 セッション 5

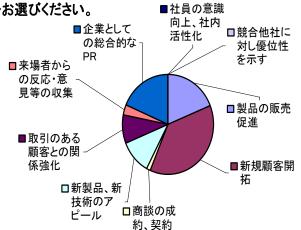

# 「検証メソドロジ入門から超並列計算機向けインターコネクトへの適用事例まで ~仏作って魂を入れる検証~」