# **JEITA**

# EDAアニュアルレポート 2014

Annual Report on Electronic Design Automation

システム・オン・チップ時代の向こうに –Beyond the "System on a Chip" era

2015年6月発行

作 成

半導体技術委員会/EDA技術専門委員会 Semiconductor Technology Committee/EDA Technical Committee

発 行

一般社団法人 電子情報技術産業協会 Japan Electronics and Information Technology Industries Association

#### 【巻頭言】

#### 「高付加価値LSIの設計基盤であるEDA技術発展に向けて」

EDA技術専門委員会 委員長 炭田 昌哉

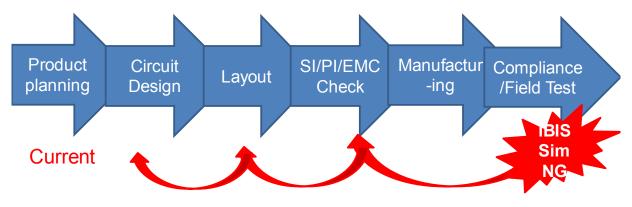

半導体は、家電製品や情報端末だけでなく、自動車、医療機器などにも搭載され、社会基盤にはなくてはならないものである。近年は、クラウドのような高度情報化社会、エコ社会を実現するために、高信頼性、低消費電力といった高付加価値をもつ半導体製品の提供が強く求められている。特に、増大するバラツキを考慮したタイミング設計技術、低消費電力技術、大規模 LSI のみならずボード、パッケージを含めた協調設計検証技術など、少ない工数で高品質な製品を設計する技術において、一層の発展が期待されている。これらの技術発展には、国内の半導体産業、大学、官庁間の密接な連携が重要であり、海外の関連業界・機関とも国際的な視野で協調、連携を図っていく必要がある。

EDA 技術専門委員会は、電子情報技術産業協会(JEITA)における業界活動組織の一つとして、電子機器の機能・性能を決定するシステム LSI の設計技術に関わる活動を行っている。設計技術およびそれに関わる標準化の動向を調査・検討し、それらの発展・推進を図り、更には国内外の関係業界の発展に寄与することを目的とし、以下の三つのテーマを設定し活動している。

- (1) EDA 技術の動向・関連情報の調査検討、課題解決への提案

- (2) EDA に関する標準化活動への貢献

- (3) EDA 技術および標準化の普及推進のためのイベント実施・支援

- (1) EDA 技術の動向・関連情報の調査検討、課題解決への提案

2014年度は、ナノ世代物理設計ワーキンググループ(NPD WG)とLSI-パッケージ-ボード相互設計ワーキンググループ(LPB WG)の二つで活動した。

NPD WG では、物理設計における課題の抽出、対策の検討、モデルやフォーマットを含む設計手法の標準化を目的とし、微細プロセスにおける設計課題を予測し、対策の検討、提案を行っている。

LPB WG では、2011 年に提案した LPB フォーマットが EDA ベンダーによる採用が進み、2015 年 12 月国際標準化完了を目標に取り組んでいる。

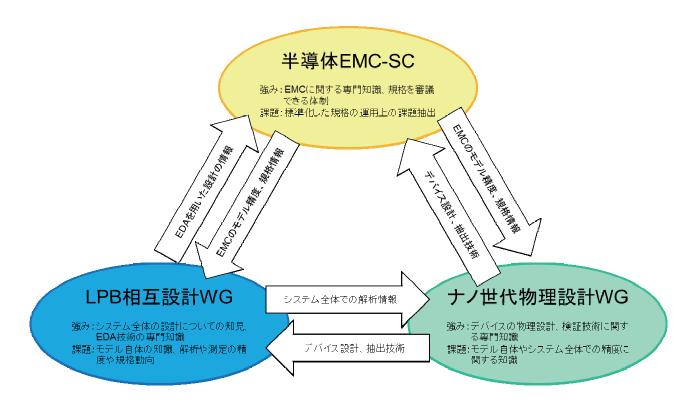

更に9月からは本委員会傘下のLPB WG、NPD WGと半導体製品技術標準化専門委員会傘下の集積回路製品技術小委員会/半導体EMC-SCとのコラボレーション活動としてLENプロジェクト(LPB-WG EMC-SC NPD-WG の頭文字)が始動した。本年度は、半導体EMC-SC で行った実測・シミュレーションのモチーフを使って、LPBフォーマットの効果を検証した。本活動の成果は、関係機関・団体との会議や学会・研究会、セミナー等で発表し、またアニュアルレポートとして積極的に公開している。

#### (2) EDA に関する標準化活動への貢献

標準化担当委員を置き、各ワーキンググループの成果を標準化に結び付けるべく、関連する標準化団体・組織と連携して活動を推進している。

IEEE/DASC, SA には、コーポレート・メンバーとして参加している。毎年、米国での DAC (6月)や DVCON (2~3月) に合わせて開催される DASC 会議には現地で出席し、日本での SystemC Japan (7月) には、米国から来日する関係者と交流を深めると共に、合同で DASC 会議にオンラインで出席している。今年度は、IEEE に提案した LPB フォーマットの規格開発プロジェクト P2401 でドラフトを作成し最終版の一歩手前まで完了した。 2015年 12月に IEEE Standard 承認の予定である。

SystemC / SystemVerilog / Power Format など言語関連のWG は、今年度も活動休止となったが、投票案件発生時には国内意見を取り纏めIEEEへのフィードバックを行う予定である。

また、IEC SC47A 国内委員会(半導体・集積回路分野)や TC91/WG13 国内小委員会(EDA 分野)との情報交換・交流を通じて、国際的な標準化活動へも貢献している。

#### (3) EDA 技術および標準化の普及推進のためのイベント実施・支援

普及活動については、本年は Design Solution Forum(10月)、ASP-DAC2015(1月)に出展し、主に LPB フォーマットの標準化取り組みを紹介した。

LPB WG ではベンダーならびにユーザーを対象にした LPB フォーラムを開催し、LPB フォーマットを導入した事例を紹介するセミナーを実施した。

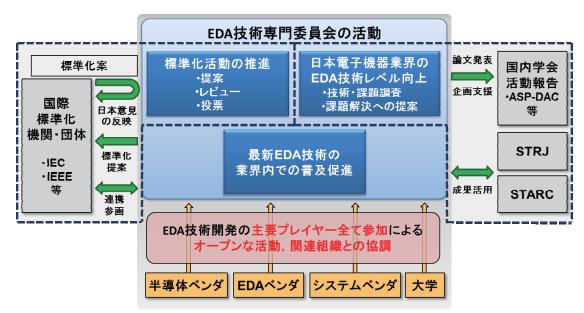

以下の図で、本委員会の活動と関係団体との関わりを示す。

IEC : 国際電気標準会議 ASP-DAC: Asia South Pacific-Design Automation Conference IEEE: 米国電気電子技術者協会 STRJ: 半導体技術ロードマップ委員会 STARC: 半導体理工学研究センター

EDA 技術専門委員会は、上図の関連組織・標準化団体との連携のもと、三つのテーマである EDA 技術調査と課題解決への技術検討、標準化活動、技術と標準化の普及促進という活動を通じ、高度情報化社会、エコ社会の実現を支える高付加価値 LSI の設計を支える EDA 技術の発展、さらには日本の電子情報機器業界の発展に寄与すべく、本年度 11 社約 50 名の業界各社有志の参画により活動してきた。2015 年度も積極的な活動を継続する予定である。

本報告「EDA アニュアルレポート 2014」は、EDA 技術専門委員会の 2014 年度年次報告として、上記三つのテーマについて活動成果をまとめたものである。また、本委員会のホームページにも各種報告を掲載しているので、ご覧いただきたい。

(http://www.jeita-edatc.com/index-jp.html)

#### 2014 年度 JEITA/EDA 技術専門委員会 委員一覧

委員長 炭田昌哉 パナソニックセミコンダクターソリューションズ(株)

半導体 BU 技術開発 C 基盤技術開発 G 参事

副委員長 高倉正博 (~2014/9)

ルネサスシステムデザイン (株)

第四開発事業部 バックエンド設計第三部

シニアエキスパート

副委員長 高橋一浩 (2014/10~)

ルネサスシステムデザイン (株)

第一要素技術事業部 デザインオートメーション部

主管技師

副委員長 改田博政 (株) 東芝 セミコンダクター&ストレージ社

ミックスドシグナル I C事業部 設計技術開発部

設計メソドロジー開発担当 参事

監事 河村 薫 (株) 富士通研究所

ものづくり技術研究所 特任研究員

幹事 大芝克幸 ソニーLSI デザイン (株)

第6 LSI 設計部門 アナログデザインソリューション部

シニアデザインエンジニア

委員 林 靖二 キヤノン (株) 生産技術研究所

実装技術研究部 実装技術第一研究室 主任研究員

委員 松澤浩彦 図研(株) EDA事業部 EL 開発部 シニア・パートナー

委員 益子行雄 (~2014/9)

日本ケイデンス・デザイン・システムズ社

テクニカルフィールドオペレーション本部

シニアテクニカルセールスマネージャー

委員 人見忠明 (2014/10~)

日本ケイデンス・デザイン・システムズ社 テクニカルオペレーション本部 カスタム IC & PCB グループ

委員 飯島一彦 日本シノブシス(合)

技術本部 本部長 バイスプレジデント

委員 三橋明城男 メンター・グラフィックス・ジャパン (株)

マーケティング部 ディレクター

委員 畔野正彦 (株) リコー LSIC 第2開発室 シニアスペシャリスト

特別委員 田中玄一 ルネサスエレクトロニクス (株)

企画本部 経営企画統括部 産業政策渉外部 部長

特別委員 赤嶺武一郎 (~2015/2)

富士通セミコンダクター(株)

(株) ソシオネクスト

共通テクノロジ開発統括部 第二設計技術部

特別委員 安茂博章 (2015/3~)

ソニー(株) RDS プラットフォーム

デバイス&マテリアル研究開発本部

セミコンダクタデバイス開発部門 デバイス設計部

特別委員 福場義憲 (株) 東芝 セミコンダクター&ストレージ社

ミックスドシグナル I C事業部 設計技術開発部

システム協調設計主幹

客員 今井正治 国立大学法人 大阪大学

大学院 情報科学研究科 情報システム工学専攻 教授

客員 若林一敏 日本電気(株) ESS 事業センター シニアエキスパート

グリーンプラットフォーム研究所 主幹研究員

#### 略語一覧

#### [1]団体・組織の名称

Accellera Accellera Systems Initiative

旧Accellera(VIとOVIを統合した、設計記述言語の標準化に関連する活動機関)とOSCI(Open SystemC Initiative: SystemC の標準化団体)が統合

ANSI American National Standards Institute

米国の標準化国家機関

ASP-DAC Asia and South Pacific Design Automation Conference

アジア·南太平洋地域でのEDA関連の国際学会(1995年に始まる)

CENELEC European Committee for Electrotechnical Standardization

EC(欧州委員会)の電気電子分野に関する標準化機関

DAC Design Automation Conference

米国で行われるEDA関連の国際学会

DASC Design Automation Standardization Committee

IEEEの下部組織で設計自動化に関する標準化委員会

DVCON Design & Verification Conference & Exhibition

米国で行われる検証専門の国際会議

ECSI European Electronic Chips & Systems design Initiative

欧州の設計自動化に関する標準化機関

EDIF Div. Electronic Design Interchange Format Division

EIAの下部組織で電子系の惜報データ交換規格の検討機関

EIA Electronic Industries Alliance

米国の電機電子通信業界団体

ICCAD International Conference on Computer Aided Design

CADに関する国際学会

IEC International Electrotechnical Commission

国際電気標準会議(電気電子分野に関する国際標準化機関)

IEEE Institute of Electrical and Electronics Engineers, Inc.

米国の電気電子分野の国際的な学会組織

IPC Association Connecting Electronics Industries

旧称:Institute for Interconnecting and Packaging Electronic Circuits

米国のプリント基板設計・製造に関する業界組織

ISO International Organization for Standardization

国際標準化機構

(電気及び電子、通信技術分野を除く全産業分野[鉱工業、農業、医薬品

等]に関する国際標準化機関)

IVC International Verilog Conference

OVIが主催するVerilog HDL国際学会であり、2000年にVIUF(VHDL International Users Forum)と統合してHDLCon(International HDL Conference)となり、2003年よりDVCon(Design & Verification Conference &

Exhibition)として開催

JEITA Japan Electronics and Information Technology Industries Association

一般社団法人 電子情報技術産業協会(電機電子業界団体)

JISC Japanese Industrial Standards Committee

日本工業標準調査会(国家審議会、IEC/ISOに対する代表機関)

JPCA Japan Electronics Packaging Circuits Association

社団法人 日本電子回路工業会

OSCI Open SystemC Initiative

SystemC の標準化団体で、2011年にAccellera Systems Initiativeへ統合

OVI Open Verilog International

Verilog - HDLに関連する技術の標準化と普及推進組織で、2000年に

VI(VHDL International)との統合でaccelleraに名称変更

SEMATECH Semiconductor Manufacturing Technology Initiative (Consortium)

半導体技術を向上するために始まった米国の官民プロジェクト

Si2 Silicon Integration Initiative

設計環境の整備促進を支援する米国の非営利法人(IECFI)

VASG VHDL Analysis and Standards Group

DASC傘下のVHDL標準化に関するワーキンググループ

VITAL VHDL Initiative Toward ASIC Libraries

VHDLライブラリ標準化団体

VSIA Virtual Socket Interface Alliance

LSIの機能ブロックのI/F標準化を目指している業界団体、2008年解散

#### [2]標準化・規格に関する技術用語

ALF Advanced Library Format

OVIで検討されたIPをも含むASICライブラリのフォーマット

ALR ASIC Library Representation

ASICライブラリ表現

CALS Computer Aided Logistics Support / Commerce at Light Speed

製品の技術情報の流通に関するすべての標準化活動の総称

CHDS Chip Hierarchical Design System

SEMATECHが要求仕様を作成した0.25-0.18um世代設計システム

CHDStd Chip Hierarchical Design System technical data

CHDSで使用するデータモデルの標準化

DCL Delay Calculation Language

遅延計算のための記述言語

DPCS Delay and Power Calculation System

IEEE1481として標準化推進されている遅延と消費電力の計算機構仕様

ECALS Electronic Commerce at Light Speed

電子機器、半導体、電子部品等の複合電子部品技術情報の流通ならびに

ECALS 辞書等の維持管理等、すべての標準化活動の総称

EDI Electronic Data Interchange

電子データ交換

EDIF Electronic Design Interchange Format

EIAの下部組織で検討されている電子系の情報データ交換規格

ESPUT European Strategic Program for Research and

Development in Information Technology

欧州情報技術研究開発戦略計画

HDL Hardware Description Language

ハードウェア記述言語

IP Intellectual Property

流通/再利用可能なLSI設計資産(本来は知的財産権の意)

JIS Japanese Industrial Standards

日本工業規格

SDF Standard Delay Format

遅延時間を表記するフォーマット

SLDL System Level Design Language

システム仕様記述言語

STEP Standard for the Exchange of Product Model Data

CADの製品データ交換のための国際規格

VHDL VHSIC (Very High Speed Integrated Circuit)

Hardware Description Language

IEEE1076仕様に基づくハードウェア記述言語

VHDL-AMS VHDL-Analog and Mixed-Signal (Extensions)

DASCの中で進められているVHDLのアナログ及びミックストシグナルシス

テムへの拡張

1. EDA技術専門委員会の活動

#### 1.1 2014 年度 JEITA/EDA 技術専門委員会 概要

委員会の名称 EDA技術専門委員会 (Electronic Design Automation Technical Committee)

委員会の目的 EDAに関連する技術およびその標準化の動向を調査し、その発展、推進を図り、

さらには国内外の関係業界の発展に寄与する

委員会の構成 会員会社/委員 11社/11名

特別委員3名客員2名

委員会の予算 会費 240,000 円 \* 11 社 = 2,640,000 円 (会費 11 社)

委員会の開催 年4回程度 (実績: 別紙-2 参照) 幹事会の開催 必要に応じ開催(実績: 別紙-2 参照)

担当事務局 JEITA/電子デバイス部 幾見 宣之(~2014.12)

宮川 裕之(2015.01~)

細川 照彦

#### ■EDA 技術専門委員会役員と担当(敬称略)

· 幹事会社 5 社(5 名)

委員長 : パナソニック 炭田 昌哉 ASP-DAC OC 副委員長: ルネサスエレクトロニクス 高倉 正博(~2014.09) HP/ML、内規改訂

高橋 一浩(2014.10~)

副委員長:東芝 改田 博政 広報パーンフレット

監事

: 富士通tミコンダクター

河村

薫

会計報告、アニュアルレポート

幹事

: ソニー

大芝

克幸

新企画検討会主査

·特別委員(3名)

標準化担当 ルネサスエレクトロニクス 田中 玄一

ナノ世代物理設計 WG 主査 富士通セミコンダクター 赤嶺武一郎(~2015.02)

ソニー 安茂博章(2015.03~)

LPB 相互設計 WG 主査 東芝 福場 義憲

客員(2名)

上流設計識者、ASP-DAC リエゾン 大阪大学 今井 正治 ASP-DAC リエゾン 日本電気 若林 一敏

#### ■2014 年度活動方針

#### 1. 委員会活動の継続的発展

スリムな組織でスムーズな運営と継続可能な体制の確立 「委員の、委員による、委員+業界のため」の活動 活動のロードマップを作成し将来展望を持って進む 健全で公平感のある財務体質の確立(会費,次期繰越金)

委員会の効率的な運営

ルールを守る 議論に重点 予算の最適運用

#### 2. 標準化の推進と展開

LPB フォーマット IEEE 規格化と国際標準展開 IEEE-SA に Advanced メンバー登録 (継続) IEEE/DASC メンバー (継続) 国際会議 (IEEE/DASC) 出席 標準化団体との協議・関係構築/維持

■活動計画の概要<別紙-1 参照>

#### <別紙 - 1>

#### 活動計画の概要

- 1. EDA 技術の動向 & 関連情報の調査検討、課題解決への提案

- (1) WG による技術動向とニーズ調査

- ・最先端テクノロジ : ナノ世代物理設計 WG、LPB-WG

- ・設計言語 : 今年度は言語関連の WG はすべて休会

- (2) 関連機関、団体、キーパーソン等との合同会議、意見交換、交流

- ·STARC, STRJ, JIC, JPCA, JIEP 等

- (3) 国内外の学会、研究会、イベントへの参加と連携

- 2. EDA 技術および標準化の普及推進のためのイベント実施、支援

- (1) EDA 技術普及の新企画推進

- (2) 外部イベントの活用 ET, Design Solution Forum 等

- (3) 各種ワークショップ、講演会の開催

- ・システム・デザイン・フォーラム

- ・LPB フォーラム

- 3. EDA に関する標準化活動への貢献と関連機関、団体への対応

- (1) EDA 設計言語およびモデル標準化のための技術的検討と提案

- ・LPB-WG を継続し、LPB 相互設計環境標準化に向けた活動を実施

- ・SystemC、SystemVerilog、VHDL、A-HDL、PowerFormat などは、必要に応じて対応(WG の再開等)

- (2) 国際的な関連機関、団体への参画・連携と標準化活動への協力

- ・標準化担当委員を中心に委員会で対応

- ・IEEE/DASC、IEEE-SA、Accellera Systems Initiative、 Si2 等との連携 DASC 会議(11 月@ET、3 月@DVCon) P2401WG(LPB) 参加のため IEEE-SA は Advanced 継続

- 4. 委員会活動の広報

- (1) 広報パンフレットの配布要否

- (2) アニュアルレポートの発行(下記 HP でも公開)

- (3) WWW ホームページの公開 http://www.jeita-edatc.com/

- (4) 活動成果の発表

- ・システムデザインフォーラム:標準化活動

- ・学術論文:ナノ世代物理設計 WG

- ・セミナー: LPB 相互設計 WG

## 2014年度 JEITA/EDA 技術専門委員会 開催実績

| 年/月     | 技術専門委員会                                                                                                                  | 懇親会                      | 幹事会   | 関連イベント                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------|

| 2014/4  | 4/25(金) (東京地区) ・14 年度役員審議、承認 ・13 年度専門委員会/WG の年間活動報告 ・14 年度事業活動計画 ・委員名簿更新内容確認 ・13 年度予算執行状況報告 ・13 年度版アニュアルレポート報告 ・14 年度予算案 | 〇<br>(2013<br>年度慰<br>労会) | 4/25  |                                                                                                                 |

| 2014/5  |                                                                                                                          |                          |       |                                                                                                                 |

| 2014/6  |                                                                                                                          |                          |       | •DAC2014 (6/1-6/5) @SF, CA<br>•DASC meeting (6/2) @DAC<br>•IBIS Summit (6/5) @DAC<br>•SystemC Japan (6/20) @新横浜 |

| 2014/7  | 7/25(金) (東京地区)<br>・標準化活動/WG 進捗報告<br>・13 年度版アニュアルレポート配布                                                                   |                          | 7/25  |                                                                                                                 |

| 2014/8  |                                                                                                                          |                          |       |                                                                                                                 |

| 2014/9  |                                                                                                                          |                          | 9/4   |                                                                                                                 |

| 2014/10 | 10/17(金)(大阪地区)<br>·標準化活動/WG 進捗報告                                                                                         | 〇<br>客員<br>交流会           | 10/17 | •Design Solution Forum 2014<br>(10/3) @新横浜                                                                      |

| 2014/11 |                                                                                                                          |                          |       | ・IEC General Meeting (東京大会) ・DASC meeting (11/11) @東京 ・ET2014 (11/19−21) @横浜 ・Asian IBIS Summit (11/20)  @横浜    |

| 2014/12 |                                                                                                                          |                          |       |                                                                                                                 |

| 2015/1  | 1/16(金) (東京地区)<br>・標準化活動/WG 進捗報告<br>・14 年度アニュアルレポート作成分担                                                                  |                          | 1/16  | •ASP-DAC2015 (1/19-22) @幕張<br>•DesignCon2015 (1/28-29)<br>@Santa Clara, CA                                      |

| 2015/2  |                                                                                                                          |                          |       |                                                                                                                 |

| 2015/3  |                                                                                                                          |                          |       | •DVCon2015 (3/2-5) @San Jose, CA •DASC meeting (3/4) @DVCon2015 •DATE2015(3/9-13) @Grenoble, France             |

### 1.2 2014 年度 JEITA/EDA 技術専門委員会 WG 開催実績

| 月        | ナノ世代物理設計 WG 関連                                             |  |  |  |  |

|----------|------------------------------------------------------------|--|--|--|--|

| 2014年 4月 |                                                            |  |  |  |  |

| 5 月      | 5/16(金) 10:00-17:00 第1回ナノ世代物理設計 WG 富士通エレクトロニクス本社 12F 応接室   |  |  |  |  |

| 6 月      | 6/13(金) 10:00-17:00 第2回ナノ世代物理設計 WG JEITA 関西支部 第2会議室        |  |  |  |  |

| 7月       | 7/11(金) 10:00-17:00 第3回ナノ世代物理設計 WG JEITA 404会議室            |  |  |  |  |

| 8月       |                                                            |  |  |  |  |

| 9月       | 9/5(金) 10:00-17:00 第4回ナノ世代物理設計WG JEITA関西支部第2会議室            |  |  |  |  |

| 10 月     | 10/10(金) 10:00-17:00 第5回ナノ世代物理設計 WG JEITA 404会議室           |  |  |  |  |

| 11 月     | 11/7(金)-8(土) ナノ世代物理設計 WG/集中審議 パナソニックリゾート大阪                 |  |  |  |  |

| 12 月     | 12/12(金)  10:00-17:00   第6回ナノ世代物理設計 WG   JEITA 関西支部  第1会議室 |  |  |  |  |

| 2015年1月  | 1/9(金) 10:00-17:00 第7回ナノ世代物理設計 WG JEITA 417会議室             |  |  |  |  |

| 2 月      | 2/13(金) 10:00-17:00 第8回ナノ世代物理設計 WG JEITA 関西支部 第1会議室        |  |  |  |  |

| 3 月      | 3/13(金) 10:00-17:00 第9回ナノ世代物理設計 WG ルネサス日本ビル 601-7会議室       |  |  |  |  |

| 月        | LPB 相互設計 WG 関連                                        |  |  |

|----------|-------------------------------------------------------|--|--|

| 2014年 4月 | 4/17(木) 13:00-17:00 第 1 回 LPB 相互設計 WG 連合会館 502 号室     |  |  |

| 5 月      | 5/30(金) 13:00-17:00 第 2 回 LPB 相互設計 WG 連合会館 404 号室     |  |  |

| 6 月      |                                                       |  |  |

| 7月       | 7/11(金) 13:00-17:00 第3回 LPB 相互設計 WG JEITA 413会議室      |  |  |

| 8月       |                                                       |  |  |

| 9 月      | 9/5(金)-6(土) LPB 相互設計 WG/集中審議 四季倶楽部ヴィラ箱根 80            |  |  |

| 10 月     | 10/31(金) 13:00-17:00 第 4 回 LPB 相互設計 WG JEITA 410 会議室  |  |  |

| 11 月     |                                                       |  |  |

| 12 月     |                                                       |  |  |

| 2015年1月  | 1/8(木) 13:00-17:00 第5回 LPB 相互設計 WG JEITA 414 会議室      |  |  |

| 2 月      |                                                       |  |  |

| 3 月      | 3/12(木) 13:00-17:00 第 6 回 LPB 相互設計 WG JEITA 414 会議室   |  |  |

| ) 3 H    | 3/19(木) 14∶00-17∶00 第 6 回 LPB フォーラム JEITA 412-414 会議室 |  |  |

#### 1.3 JEITA/EDA 技術専門委員会ホームページ

#### 1.3.1 開設の目的

電子情報技術産業協会(JEITA)の EDA 技術専門委員会の活動状況を公開し、EDA 技術に関する標準化や技術調査に関するご理解とご協力を頂くことを目的とする。

#### 1.3.2ホームページの構成

2006 年度にホームページを一新し、よりわかりやすく、欲しい情報に容易にアクセスできるような構成にした。ホームページは日本語版の他に英語版も用意し、英語版を最初に表示することで海外からの利用者の利便性に配慮している。日本語版、英語版の表示は各ページで簡単に切り替えられるように構成されている。本委員会の成果は、ドキュメントとして閲覧できると共に、ダウンロードすることもできる。

ホームページは以下の URL からアクセスすることができ、データ更新やメンテナンスは 担当委員が行っている。

http://www.jeita-edatc.com/

日本語版・英語版は、それぞれ次のエントリーで構成されている。

| 日本語版:     | 英語版:                          |  |  |

|-----------|-------------------------------|--|--|

| 委員会の紹介    | Introduction of the committee |  |  |

| 委員会活動     | Committee activity            |  |  |

| 公開資料ライブラリ | Open data library             |  |  |

| イベント・関連機関 | Event / Related organizations |  |  |

| お問い合わせ    | Inquiry                       |  |  |

| サイトマップ    | Site map                      |  |  |

#### (1) 委員会の紹介 / Introduction of the committee

委員長挨拶、活動と成果、メンバーをサブエントリとする。本委員会の概要、前年度の 活動内容・成果、本年度の活動計画、委員会メンバーを紹介している。

#### (2) 委員会活動 / Committee activity

下記の委員会の活動を紹介している。休止中、または活動を終了したものも含めている。

- ・ナノ世代物理設計 WG

- ・LSI・パッケージ・ボード相互設計 WG

- SystemVerilog WG

- SystemC WG

- PowerFormat WG

- · EDSFair 実行委員会

なお、LSI・パッケージ・ボード相互設計 WG は、2011 年度より独自のホームページを開

設し、WGのページからリンクを張っている。

#### (3) 公開資料ライブラリ / Open data library

「公開資料ライブラリ」のページでは、EDA 技術専門委員会内の各委員会・WG の活動報告や各委員からの発表資料等を適宜掲載している。主な掲載資料を以下に示す。なお、英語の資料は存在しないため、英語メニューからも日本語資料を参照している。

- ・EDA 技術専門委員会(過去のアニュアルレポート)

- ・EDA 標準化小委員会(SystemC 推奨設計メソドロジ、Power Format 比較表など)

- ・ナノ世代物理設計 WG (過去の資料)

- ・EDSFair 実行委員会(システムデザインフォーラムの紹介)

- ・システムレベル設計研究会(旧サイトへのリンク)

- ・その他 (過去の委員会活動報告)

#### (4) イベント・関連機関 / Event / Related organizations

「関連の会議」では、次の関係の深い EDA 関連技術委員会を紹介している。

- ・IEEE/DASC (電気電子学会/設計自動化標準化委員会)

- · IEC/TC91/WG13 (国際電気標準会議/電子実装技術委員会)

また、「関連機関」では、本委員会に関連のある 17 機関を紹介し、委員会名称はそれぞれのホームページへリンクされている。

#### (5) お問い合わせ / Inquiry

質問項目を入力するためのフォームが表示され、ホームページ管理者へのメールを送信することができる。

#### (6) サイトマップ / Site map

ホームページを構成している全体一覧を表示し、参照したいページに直接アクセスできるようにしている。

2. 各技術委員会の活動報告

#### 2.1 EDA 標準化活動

#### 2.1.1 標準化活動概要

#### (1)発足の背景とミッション

JEITA/EDA 技術専門委員会の標準化活動は、1990年の EIAJ/EDIF 研究委員会設立に始まり、当初は EDA に関するグローバルな重要課題に対して日本の業界を代表する唯一の機関として、特に設計記述言語の仕様標準化とその啓蒙等に多大な貢献を果たしてきた。近年、設計記述言語は高度化し、普及が進んだ。しかし、設計生産性の更なる向上および、それを支える EDA ツールの効率的な開発・利用を進めるためには、設計技術言語の国際標準化は依然として重要なテーマである。そこで、標準化関連の活動をより明確に位置づけるため 2000年11月に EDA 標準化小委員会が設立し活動を開始した。その後 2011年度に入り標準化活動の見直しを行い、標準化小委員を廃止し、EDA 技術専門委員会の下に標準化担当委員を置く体制に変更し現在に至っている(図-1参照)。

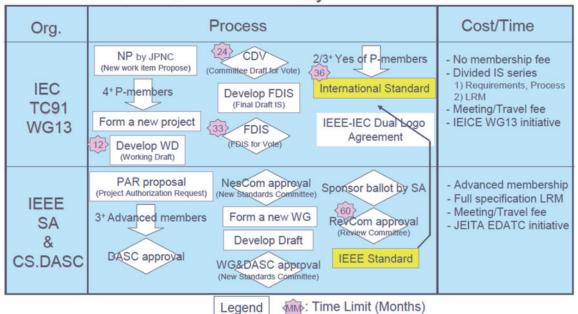

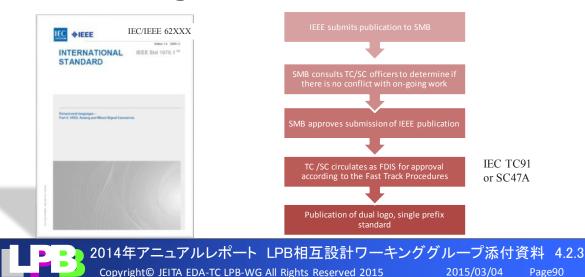

世界的には EDA 関連の標準は IEC(International Electrotechnical Commission)と IEEE(The Institute of Electrical and Electronics Engineers)で議論し、制定されてきた。IEC ではデザインオートメーションを議論する TC (Technical Committee) 91/WG (Working Group) 13, 14, 15、IEEE ではコンピュータソサイエティの DASC(Design Automation Standards Committee)、および SA(Standards Association)である。2002 年、IEC と IEEE が Dual Logo 協定を締結したことにより、IEEE 標準は IEC での技術審議なく最終ドラフト投票のみで IEC 国際標準に昇格できるようになった。

国内では IEC の対応機関は、日本工業標準調査会(JISC: Japanese Industrial Standards Committee)である。また、TC 毎に国内委員会があり、電子情報通信学会や JEITA に組織化されている。TC91(電子実装技術)国内委員会は JEITA にあり、TC91 のハードウェア設計記述言語関連のワーキンググループ(WG13)の国内委員会は電子情報通信学会にある。

JEITA/EDA 技術専門委員会は、2002 年度に IEC/TC93 国内委員会と協調体制を確立し IEC/TC93/WG2 (当時。現 IEC/TC91/WG13) の各種標準化提案を直接審議できる体制を構築した。2003 年度には、SystemC および SystemVerilog の標準化を業界として検討・推進する目的で、それぞれワーキンググループを発足させた。2007 年度には、CPF(Common Power Format)と UPF(Unified Power Format)の二つの Power Format の標準化案の議論と統一を目的に、検討ワーキンググループを発足させた。SystemC は、ますます重要性が認識されているシステムレベルの設計言語のひとつであり、SystemVerilog は IEEE1364(Verilog HDL)の後継・検証技術の拡張である。CPF/UPF の Power Format は、主にシステム LSI の低消費電力化設計の効率化を目的とした設計言語である。これらワーキンググループは、日本の標準化組織として、海外の関連団体と連携し、言語仕様の専門的な技術検討と改善提案を通じて、標準化へ貢献すること目指して活動を行っている。Power Format 検討ワーキンググループは目的を達成したため、2010 年 3 月に解散した。

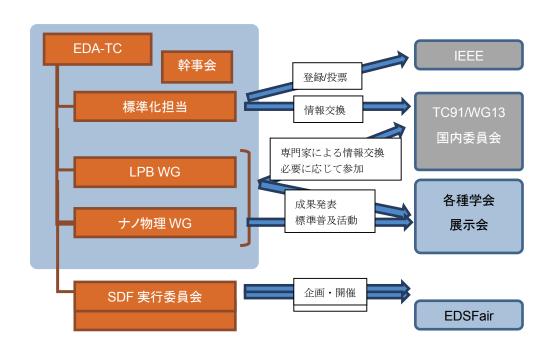

図-1 EDA 技術専門委員会の体制

#### (2) 2014年度活動 国内活動

標準化活動の大きな成果として、LPB WG の LPB フォーマットをEDA関連で日本初の国際標準(IEEE規格)とするべくIEEE にて P2401 として WG を設立。Chair, Vice Chair および Secretary とも日本で担当。日本だけでなく米国、欧州との議論を行うため充実した事前議論を国内で実施。また、WG内での議論に留まらず、複数回のフォーラム開催、国内でのベンダセミナでの情報発信、日本開催の国際学会での情報発信を行った。

#### (3) 2014年度活動 国際活動

本年度は LPB フォーマットを念願の日本初のEDA 標準とすべくIEEE 標準化 P2401 WG 活動を開始。2015年度での標準化を目標に本格稼働。米国および欧州のメンバを勧誘し、WG 内での議論の充実を図り、米国ミルピタス市にて対面WG会議も開催、白熱した議論を戦わせた。また、DASC会議への直接参加、日本開催展示会参加のIEEE DASC メンバ来日に合わせ、IEEE DASC メンバーと JEITA EDA-TC との情報交換会を実施。

LPB フォーマット標準化活動詳細は2.3節 LPB相互設計WG内で紹介する。

#### ① IEEE DASC 情報交換

2014年度はIEEE DASC会議/メンバーとの情報交換を4回参加。JEITA EDA技術専門委員会の 状況報告も実施。2回は米国開催で田中特別委員を派遣。2回は日本に開催を誘致した。対面会 議を複数回実施することによりキーマンとの交流を深められ、IEEE P2401 実現に向け、強固 な協力関係を構築できた。

DAC 会議 6月2日 米国サンフランシスコ市

SystemC Japan

6月20日

新横浜

IEC 東京大会

11月11日

有楽町

DVCon 会議 3月5日 米国サンホセ市

#### ② IEC/TC91/WG13 国際連携

田中特別委員(WG13 メンバ) が下記 IEC/TC91/WG13 会議に出席し、国際標準化活動を推進するとともに、EDA 技術専門委員会(日本側)の意見反映を実施した。

IEC/TC91/WG13 会議 11 月 11 日 有楽町

#### ③ IEC/SC47A/WG2 国際連携

PB 福場主査(WG メンバ)、LPB 担当者および田中標準化担当委員(オブザーバ)が東京有楽町で行われた IEC 会議に参加。IEEE P2401 との協調を図った。

#### 2.1.2 IEEE/DASC (電気電子学会/設計自動化標準委員会) · IEEE-SA (標準協会)

#### (1) 活動の概要

IEEE は米国に本部を置く電気、電子、情報、などの国際的な学会である。また、この分野の標準化活動を長年にわたり、しかも広範囲に実施している。SA は IEEE 標準規格を管理する組織であり、新規規格と規格メンテナンスの提案承認、規格投票作業と規格化承認を管理する。DASC は Computer Society の下部組織として、SA の支援を受けながらエレクトロニクス産業における設計自動化関連の標準化活動を行っている。

活動の中心は、標準設計記述言語(HDL: Hardware Description Language)の VHDL と Verilog HDL に関連する設計と検証であり、タイミング情報、論理合成、算術関数とテストの標準化に注力している。これら設計言語に関連して、システムレベルまで適用範囲を拡大して、Analog Mixed Signal、ソフトウェアとハードウェア協調設計等の拡張の標準化を検討している。2005 年には SystemVerilog と SystemC という高位設計技術言語、設計と検証を統合した記述言語の標準化作業が完了し、2009 年および2012 年には SytemVerilog、2011 年には SystemC がそれぞれ第一回目の改定作業を完了している。

#### (2) JEITA/EDA 技術専門委員会との関連

これまでは EDA 技術専門委員会は IEEE/DASC のメンバーとして関連する WG に参加し、標準化案に日本の意見を反映してきた。2004年12月には IEEE-SA のメンバーにもなり、IEEE の標準化活動に、ドラフトレビュー・標準化案の改善の提案・投票を通じて積極的に参加し

ている。

今年度は、IEC 東京大会の会期中 2014年11月13日に IEEE/DASC との情報交換会を DASC 会議と共に、日本で開催した。米国からは Stan Krolikoski 氏(DASC 委員長)、Dennis Brophy 氏 (DASC 委員),電話会議で DASC 各メンバ,日本からは、炭田委員長、田中標準化担当委員,LPB WG 福場主査,他 LPB WG メンバー2名が出席した。会議において、EDA 技術専門委員会からは、活動状況の紹介として LPB フォーマットの標準化への検討状況を説明し情報交換を行った。

#### 2.1.3 IEC/TC91/WG13 (国際電気標準会議/デザインオートメーション)

IEC の SMB(Standardization Management Board・標準管理評議会)は、TC93 に対してPメンバー数を5以上にすることを求め、TC93 もPメンバー数の増加に向けて何年も努力を続けたが成功せず、2012年2月 SMB において TC93 の解散と TC91 への合流が決定された。その後、TC91 での調整を終え WG13-15 の 3WG で活動を再開した。また DA (Design Automation)を扱う 3WGのみで従来同様 国内サブ委員会として電子情報通信学会下で活動継続することとなった。韓国や中国では旧 TC93 と TC91 との合流に手間取っており、旧 TC93メンバーがうまく活動できていないという現実がある一方、日本では TC91 への合流がスムーズに進み従来通り問題なく活動できている。

#### (1)活動の概要

IEC は 1906 年に設立された国際標準化機関であり、すでに 100 歳を越える。設計自動化を取り扱う IEC/TC93 は 1992 年に設立された。TC93 の全体会議は毎年開催され、スイス、英、仏、米、デンマーク、日、英、米、独、伊と開催された。その後 2012 年に TC91 傘下での活動を開始し現在に至る。

#### (2) TC91/DA の組織とワーキンググループ (WG)

TC91/DA は3つの WG から構成されている。今までの各 WG の主な活動を示す。

- ・WG13:部品・回路・システム記述言語、モデルのハーモナイゼーション:

- (a) 設計検証記述言語 SystemVerilog とシステム記述言語 SystemC の言語仕様拡張と利用普及のためのモデル化を検討。(b) 国際規格のメンテナンス (VHDL、VHDL-AMS、PSL、SDF、DCL/SPEF、IBIS 等)。(c) STEP Electrical (ISO 規格) と EDA 標準の整合性の検討。(d) EDIF と AP-210 との整合性の検討。(e) 言語間の Interoperability の検討

- ・WG14: 再利用可能部品ライブラリ, 規格適合性テストの具体的事案の議論。

- 日・米・欧の各プロジェクト間の仕様整合と連携の検討、日本からは JEITA/ECALS プロジェクトの成果を提案している。IBIS も話題に取り上げられている。最近は電子カタロ

グの流通に関する規格案が議論の中心となっている。

・WG15:システムテスト記述言語、ATML(Automatic Test Markup Language)の検討。

#### 2.2 ナノ世代物理設計ワーキンググループ(Nano Scale Physical Design Working Group)

#### 2.2.1 目的

半導体デバイス・配線テクノロジの進化に伴い、新たな設計上の課題があらわれてきている。また、これらの課題に対処するため各社が開発した設計手法や設計情報が、標準化されず、設計環境の開発・サポートコストが削減できない事例や、EDAツール間あるいは半導体ベンダと顧客との間の情報授受がうまく行えない事例が増えてきている。

一方、国内半導体ベンダではFabless化が進み、提供されるプロセス情報や設計環境のみでは、 設計品質を保つことが困難になった。そのため、これまで以上に製造と設計を補完する種々の事 象をいかにスムーズにやりとりする仕組みを作るかが重要となる。

上記課題を背景として、本ワーキンググループでは、次のような調査、課題検討、および標準化を実施することにより、より効率的な設計環境の実現に貢献することを目的として活動する。

- ナノ世代テクノロジノードにおける、LSI の物理設計・検証に関する参加各社の共通課題の抽出、および解決手法の提案

- 半導体ベンダとその顧客との間でやり取りするライブラリや設計情報等を規定する、設計 ルール・ガイドラインの作成

- LSI の物理設計、検証手法の精度、互換性や効率を向上できるライブラリ・設計情報フォーマットの標準化

- 各種ライブラリを用いて行う検証が十分な精度で行えるかを判定するための標準ベンチマーク・データの作成

#### 2.2.2 活動内容

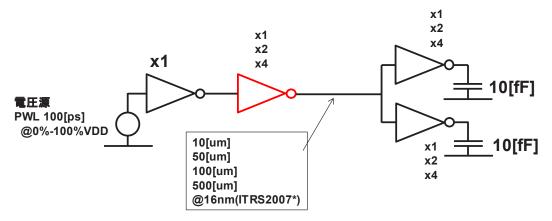

2014 年度は参加各社が問題意識を有している設計課題について優先順位付けを行い、以下の3 テーマに注力した。

- EMI ノイズ解析

- 低電圧におけるばらつき評価

- 次世代 Tr.構造における物理設計課題の検討

現在直面している設計課題として「EMI ノイズ」を、将来を見据えたテーマとして「低電圧におけるばらつき」と「次世代 Tr.構造の課題」をピックアップした。

LSI-Package-Board にまたがる EMI の課題に関しては、LPB 相互設計 WG および半導体製品技術標準化専門委員会・集積回路製品技術小委員会・半導体 EMC-SC と連携して進めた。

これら活動で得られた成果は、本アニュアルレポートや論文発表、学会発表などを通じて、広く 公表を行っていく。 今年度の活動から得られた各テーマの課題と今後の展開を以下に記す。

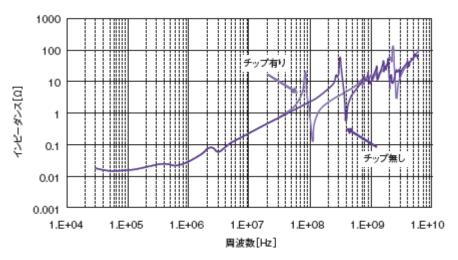

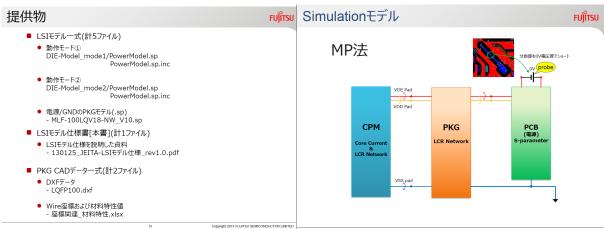

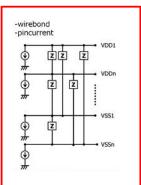

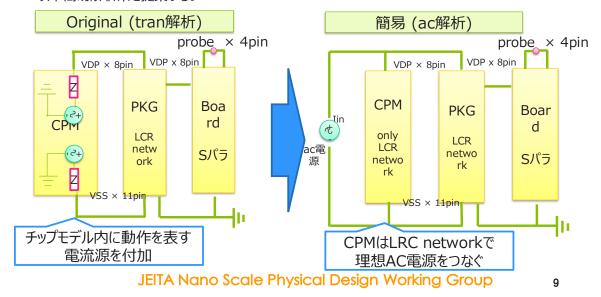

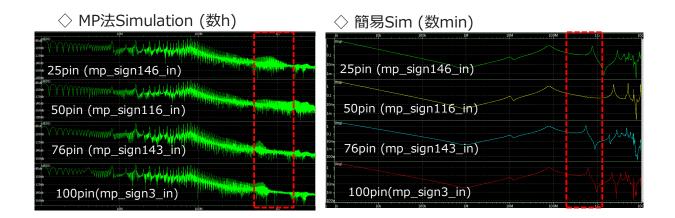

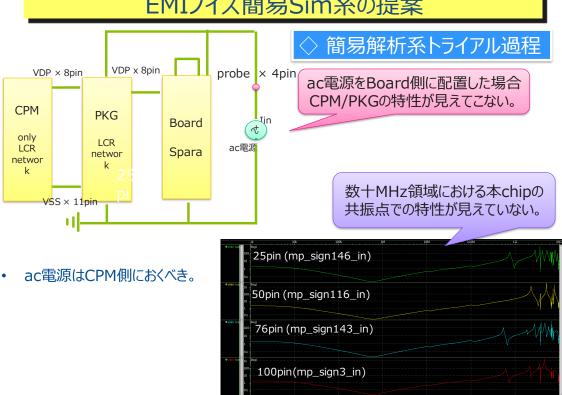

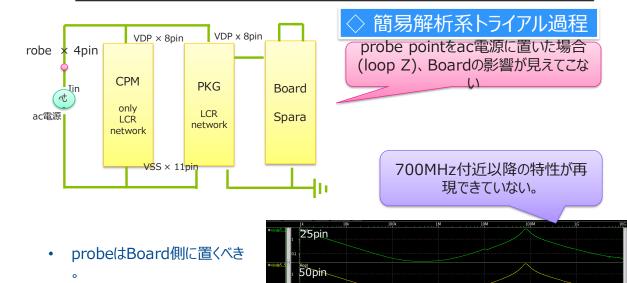

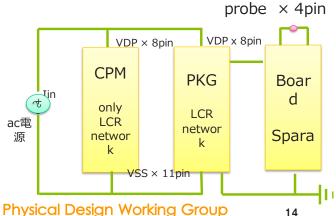

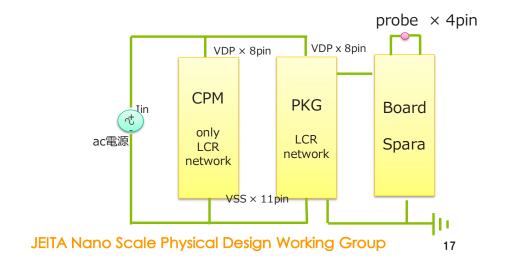

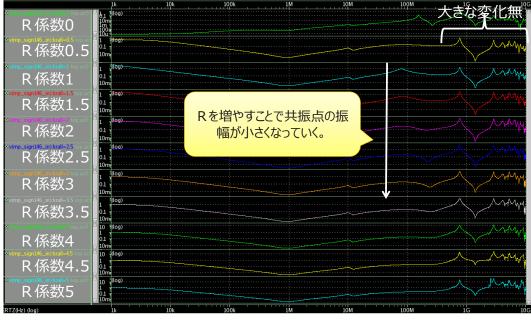

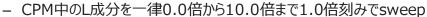

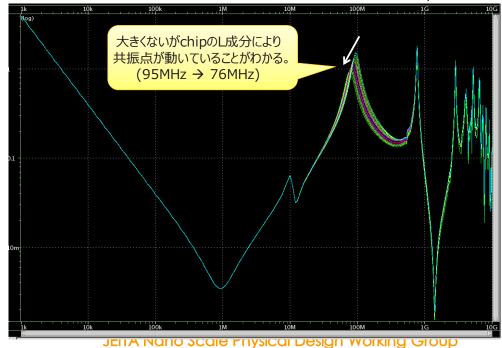

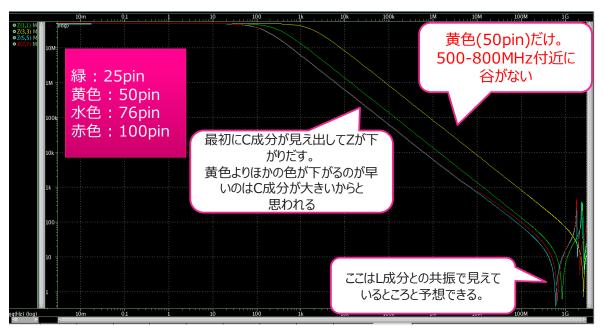

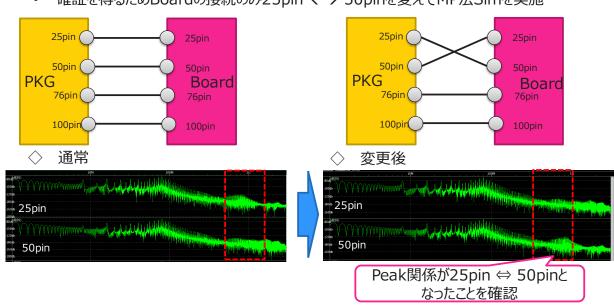

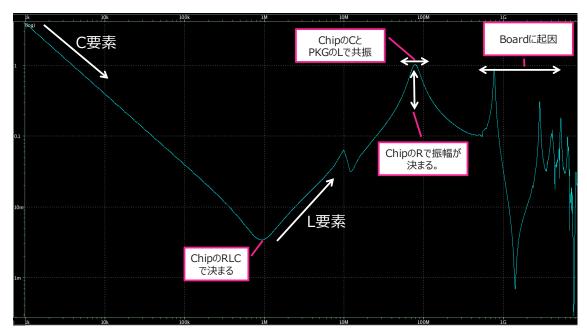

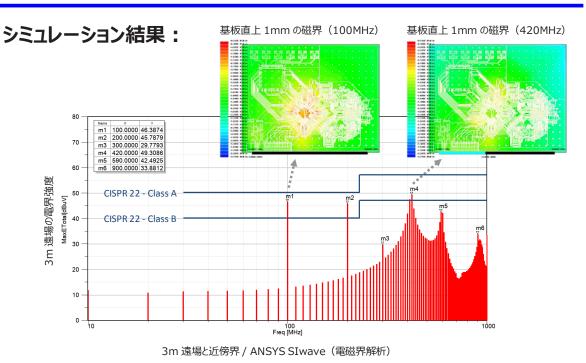

#### (1) EMI ノイズ解析

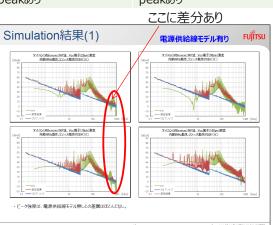

LSI 設計において、高速 IF に代表されるように高速化が年々進んでおり、ノイズ問題が深刻化している。今年度は EMI ノイズに Focus して検討を行った。EMI 設計において、LSI/Package/Board (LPB) 協調は非常に重要であり、LPB 相互設計 WG、半導体 EMC-SC、ナノ世代物理設計 WG が協力した「LEN PJ」に参画することで、調査を加速させた。

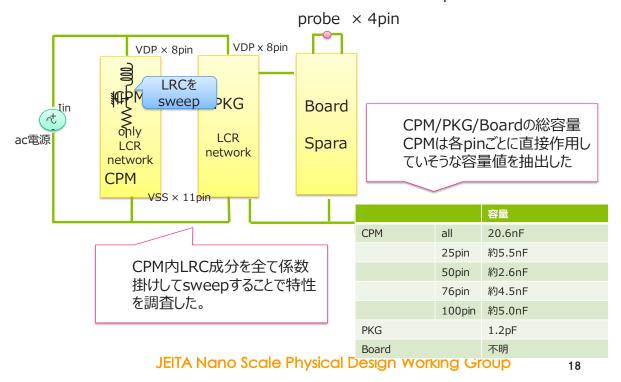

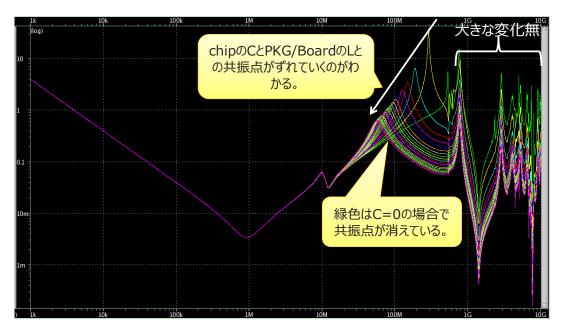

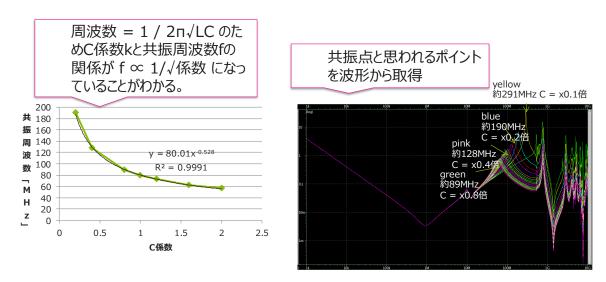

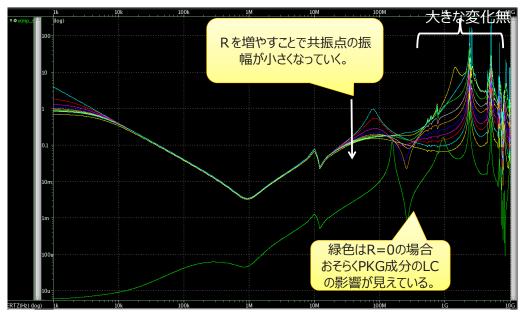

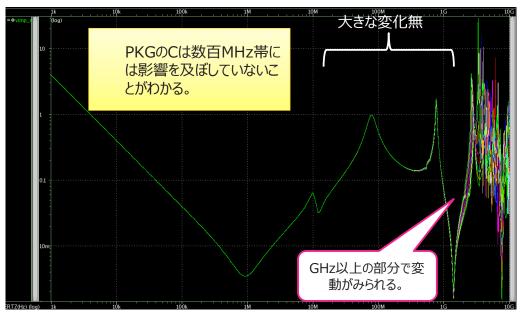

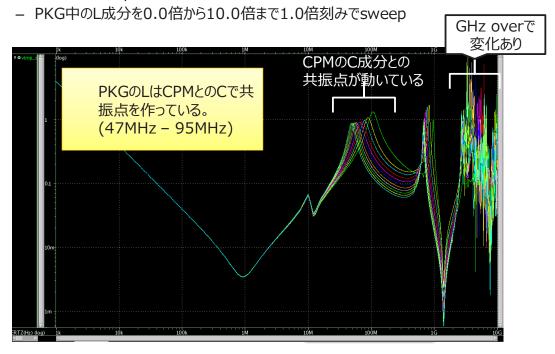

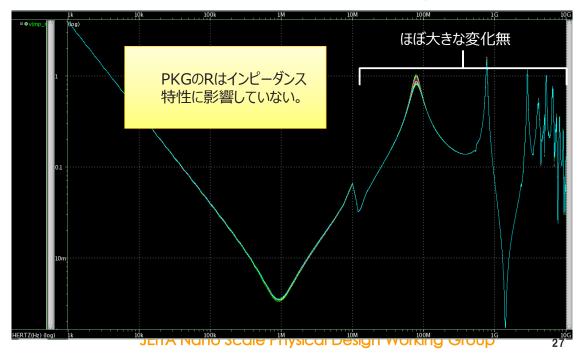

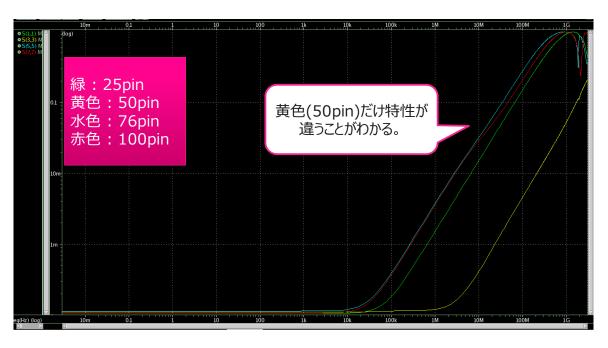

半導体 EMC-SC がおこなったマイコンをモチーフとした MP 法 EMI 実測-Sim との相関調査の結果の中から、ある周波数帯域において Simulation と実測で大きな相違がある点に着目し、解析を進めた。その結果、(1) EMI ノイズ簡易 Simulation 回路系の提案、(2) EMI 実測-SIM ずれの要因解析、を得た。

来年度は(1)については適用実績を増やし、適用範囲、精度について検討を行い、(2)については LSI-Package-Board Model の精度向上の検討、課題の抽出を進めていく。

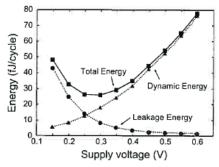

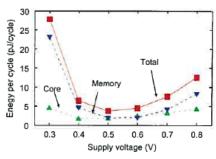

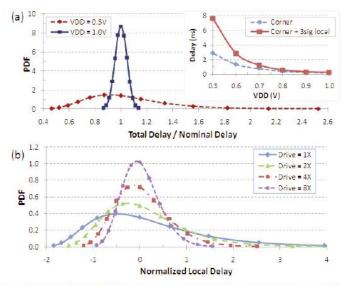

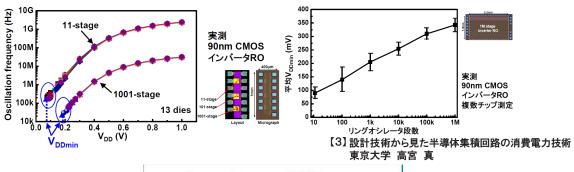

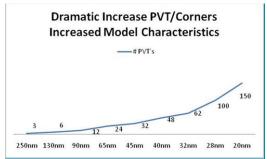

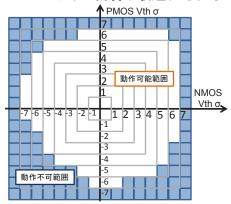

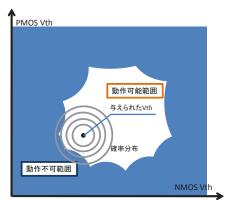

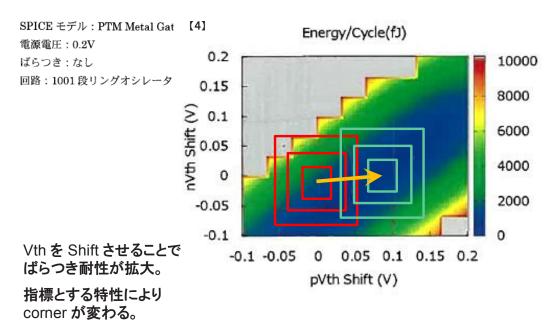

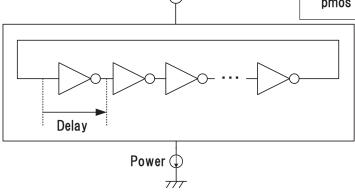

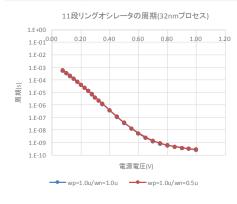

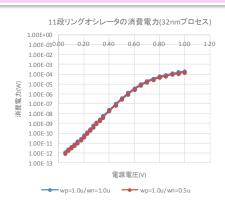

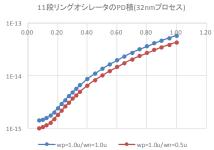

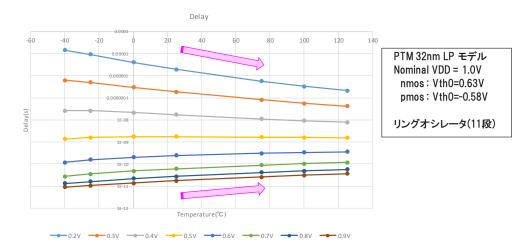

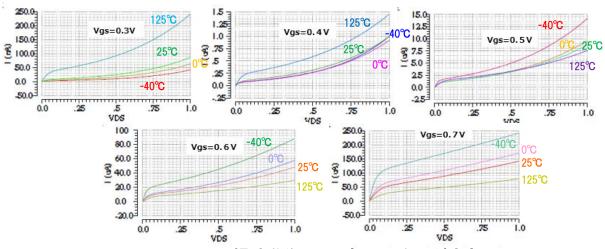

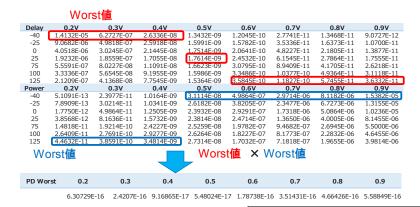

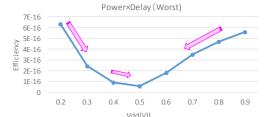

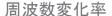

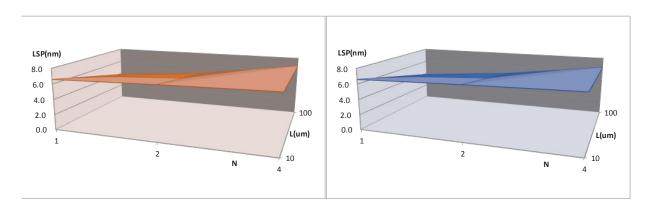

#### (2) 低電圧におけるばらつき評価

昨年度に低電圧動作時に Transistor ばらつきが、Ring Osc.の動作や消費電力等の特性に及ぼす影響を検討し、Transistor の特性 Center 値を見直すことで、ばらつき耐性が向上できる可能性を見出した。今年度は新たに温度特性についての考察を加え、同一温度条件下で比較した場合には電圧を下げるほどエネルギー効率が良いが、温度ばらつきを加えた Worst 値で考えると結果が異なり電源電圧に最適値が存在する可能性を示した。

来年度は温度を含めたコーナー条件間でのばらつきを考慮した機構の更なる調査および、センサーネットワークなどの IoT (Internet of Things) への提言をまとめていく。

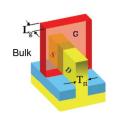

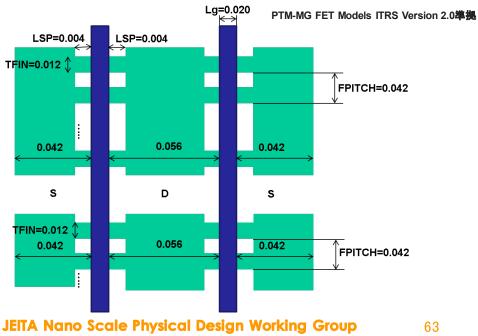

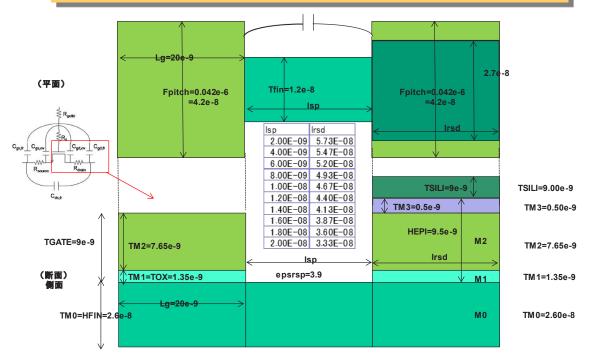

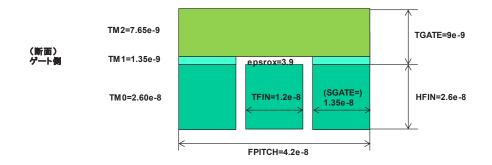

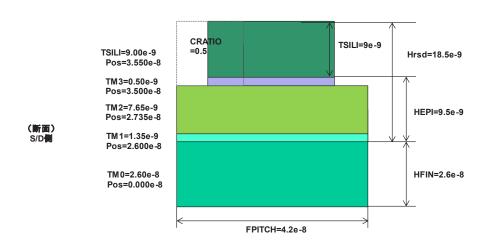

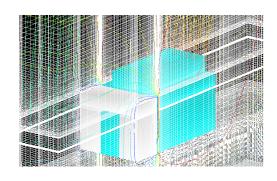

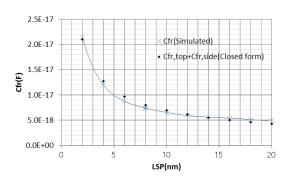

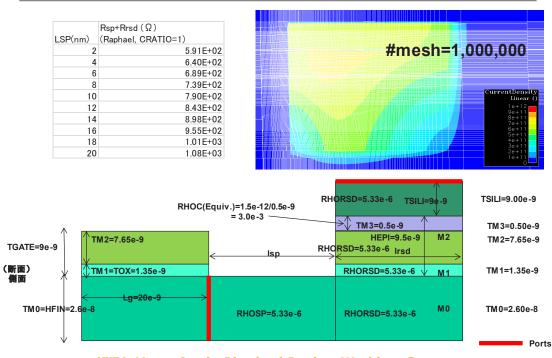

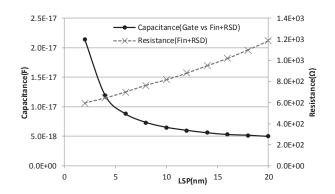

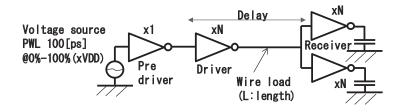

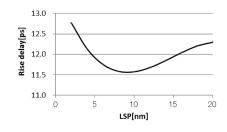

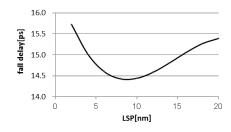

#### (3) 次世代 Tr. 構造における物理設計課題の検討

次世代プロセスルールである、16nm 以降のテクノロジでは、これまでに扱われてきたプレーナー型のトランジスタに代わり、立体構造を持つ FinFET に移行している。FinFET は立体構造であるため、その寄生 RC 成分も、既存のプレーナー型と異なると考えられる。今年度は、FinFET の寄生 RC のモデル化を行い、モデル化した寄生 RC を用いて、回路ベースでの伝搬遅延時間の最適化を行った。結果、同一面積にて最大 10% 程度の遅延時間改善が可能であることを示した。

来年度は、Power の観点も追加して、検討を進めていく。

これらの活動で得られた成果は、次のような形態により無償で一般に公開する。

- アニュアルレポート

- JEITA のホームページ

- 関連学会の研究会・学会における発表や論文誌への投稿

成果の詳細は本アニュアルレポートの付録に掲載した。

#### 2.2.3 参加メンバー

主 査 赤嶺武一郎 \*1 富士通セミコンダクター㈱

副 主 査 安 茂 博 章 \*2 ソニー(株)

委員金本俊幾ルネサスエレクトロニクス㈱同栗山茂\*3ルネサスエレクトロニクス㈱

同態野義則㈱リコー

同 河野正治 ㈱リコー

同 城間 誠 \*4 パナソニックシステムテクノ

同清水 光 平 \*5パナソニックシステムテクノ同長 谷 川 尚ソニーLSI デザイン(株)

オブザーバー 黒川敦 弘前大学

EDA-TC 標準化担当 田中 玄一 ルネサスエレクトロニクス㈱

\*1: ~2015年2月 3月は特別委員

\*2:2015年3月~ 主査

\*3: ~2015年1月 \*4: ~2014年5月 \*5:2014年6月~

#### 2.3 LPB (LSI・パッケージ・ボード) 相互設計ワーキンググループ

#### 2.3.1 LPB 相互設計ワーキンググループ(本委員会)活動報告

#### 2.3.1.1 背景と設立までの経緯

#### 2.3.1.1.1 日本工業製品の状況

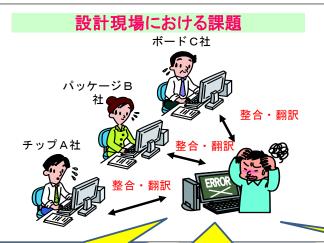

電子機器(セット)の開発は高性能化、低価格化、商品サイクルの短期化が顕著となり、これに対応するためにセットの機能面、設計/製造面でのグローバル化が進んでいる。この中で市場競争力を生む商品企画と開発力が課題である。かつて、日本工業製品は機能・性能・品質において差別化を図ってきたがこの要素を保持したまま、国際市場において開発競争に勝ち残る為の手段が模索されている。これまで日本の企業において、LPB各分野においては個別に切磋琢磨しており設計のノウハウは構築されている。しかしながらそれらを共有しない閉塞性、企業間の考え方の違い、設計保証について全体での俯瞰をすることなく供給者に対して過度の設計保証を求める傾向にあり、設計者〔会社〕は設計情報の公開には非常に消極的であると言わざるを得ない。これにより LPB 相互の設計現場の連携が十分に取れていたとは言い難い。結果として全体としての最適化が進まず、単価、開発コストや開発期間において国際市場での競争力は向上せず、むしろ低下の傾向にあるとすら言える。

#### 2.3.1.1.2 開発環境における問題

設計を効率的に行うには EDA の整備や改良、情報の収集が迅速に行われなければならない。これらの開発環境の整備は各企業個々に行われてきており、ノウハウとして一般には公開されていない。しかしながらこの閉塞性が設計に必要な情報の流通を阻害しており、また EDA の整備コストの増大や、VOC (Voice Of Customer) の分散によりツールの改良が行われない等の弊害を生んでいる。これらは競争するべき分野と協調するべき分野が明確にされていないために、本来複数の企業が協力して効率化をするべき分野の要素まで各企業の機密内容に含まれていると拡大解釈されていたことに問題の本質があると考えられる。

#### 2.3.1.1.3 技術的背景

システムの高速化と電源・インターフェースの低電圧化でタイミングやノイズに対するマージンが少なくなってきている。またコスト競争の激化によりコストと性能のバランス設計は益々重要となっている。これまで設計はLSI・パッケージ・ボード(以下LPB)それぞれ別々に設計ガイドに従って行われてきた。しかしながら設計マージンの減少に伴いあらかじめLPB各所個別の設計ガイドを定めることが難しくなり、LPB全体で協調して設計ターゲットを決める必要が出てきた。すなわちシステムの設計途上でシミュレーションによって設計指針を決める手法への変革が必要であり、その為には迅速でかつ正確なシミュレーションを行える環境が必要となった。

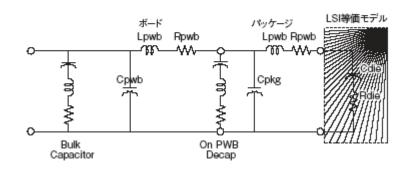

#### 2.3.1.1.4 特性面における LPB 相互設計の必要性一例

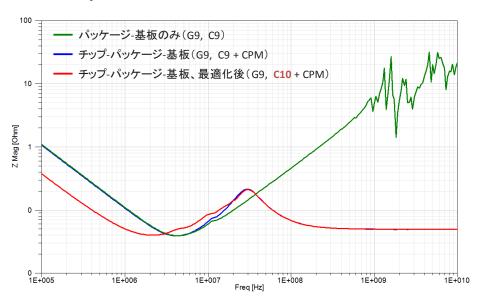

LPBが相互に協調して設計すべき部分の一例として電源網の設計がある。LPB上の電源網:Power Delivery Network(以下 PDN)(図 2.3.1-1)はノイズを小さくする為にインピーダンスを下げるように設計をする。LPB各部に存在するインダクタンス成分とキャパシタンス成分により共振が起こる。共振が発生する周波数ではインピーダンスが極端に大きくなる。すなわち LPB各部の PDN モデルを正確にシミュレーションに反映しないと全体の PDN の設計が正しく出来ない(図 2.3.1-2)。このシミュレーションを実行するためには LSIの PDN 等価モデル、パッケージやボードの形状情報、構成材料の電気特性、構成部品の等価モデルなど様々な情報を揃えなければならない。この際に LPBの各部分の設計情報の書式や仕様の違い、必要パラメータが共有されていない事などが効率的な設計が出来ない要因となっている。

図 2.3.1-1 LPB の電源網(PDN)の等価回路

図 2.3.1-2 LPB の電源網 (PDN) の等価回路

#### 2.3.1.1.5 JEITA における LPB 相互設計 WG の発足

開発の難易度アップ、コスト・開発期間の国際競争の激化は設計のアプローチへも変革を求められる。個々の最適化ではセット全体の最適化を実現するのは難しくなり全体を見越した設計が LPB 個々にも求められる。そこで LPB の設計をある 1 つのパーティーに集約する手段も考えられるが、これは非現実的である。LPB それぞれの物理的事象はスケールが違いすぎ、個々の

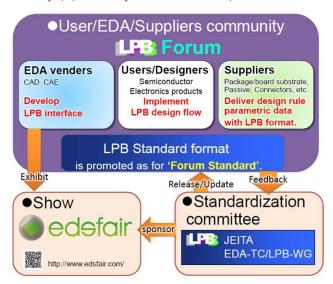

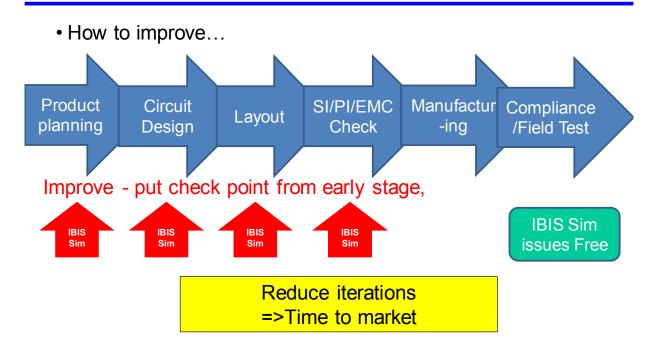

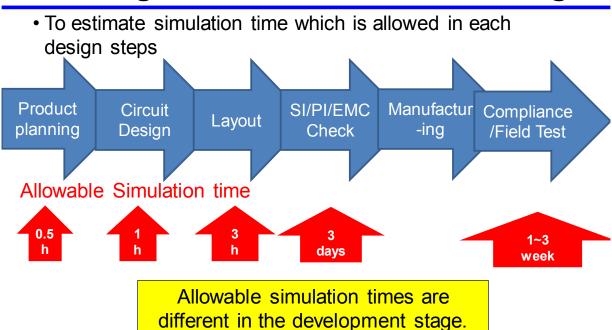

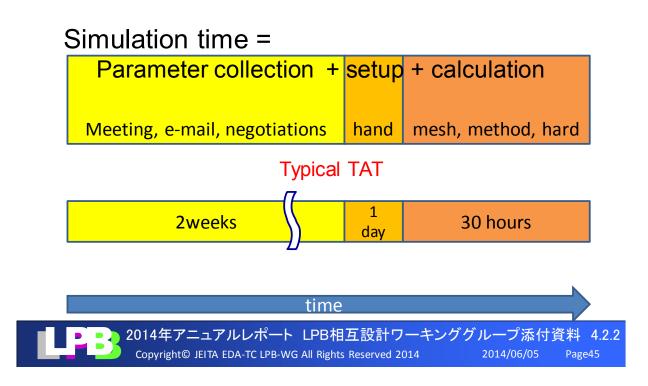

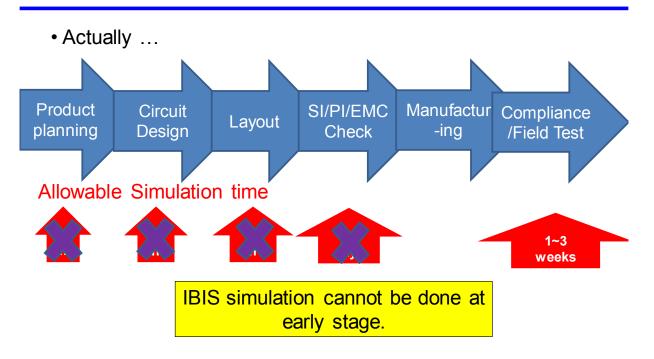

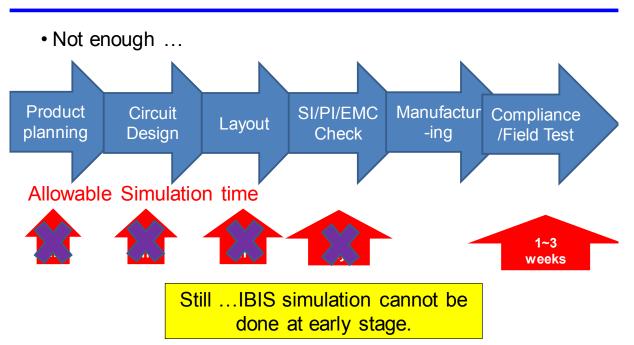

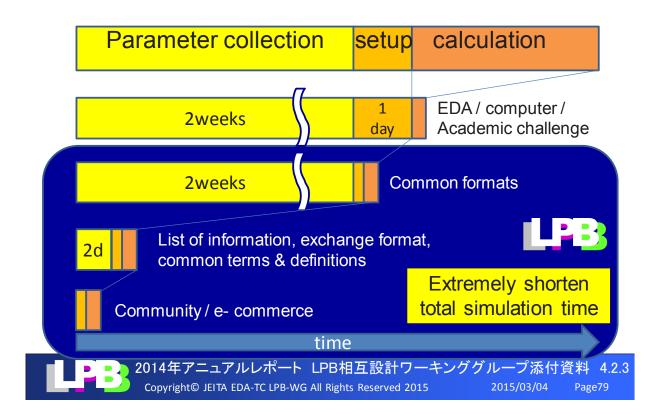

専門の技術者が腕を振るわなければならない。ここで LPB がうまく連携できる仕組みが必要と なってきた。この、声を受けて JEITA の半導体部会、EDA 技術専門委員会の元に各企業の代表 が集まり半年の準備ワークグループ活動を経て 2010 年 4 月に LPB 相互設計ワークグループ(以 下 LPB-WG) が正式発足した。このワークグループでは設計最適化の課題を整理し、設計効率を 向上させる標準化を行うことを目的としている。特に LPB は設計工期やシミュレーション時間 を短縮することに注力している。シミュレーション時間を一例として LPB-WG の活動範囲を説 明する。シミュレーション時間とは一般に実行時間をイメージすることが一般的である。しか しながら工期から考えるとシミュレーション時間とは準備段階の情報収集やセットアップ、そ して計算実行時間の合計と考えるべきである。これまでシミュレーション時間を短縮するには 計算時間を短縮することに注力されてきたが、これは EDA ツールの改良やコンピュータの処理 能力の改良で行われてきた。しかしながら実際にはシミュレーション時間の内訳は準備段階の ほうが計算時間よりも長くかかっているのが実情である。この準備段階に費やす時間を短縮す るのが LPB-WG の標準化の活動範囲となる。 情報を交換する書式を同一にし、必要な情報をリ ストにすることで情報収集時間とセットアップにかかる時間は飛躍的に短縮する。さらに情報 を交換するしくみがあれば更なる短縮が可能となる。例えば、コミュニティーの形成や e-コマ ースの活用、クラウドなどデータベースの整備等が考えられる。 LPB フォーラム(後述) はこ の目的で設立されている。標準のみならず情報流通手法まで開発することが LPB-WG の役割範 囲としている。(図 2.3.1-3)

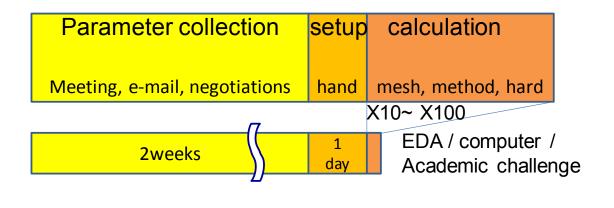

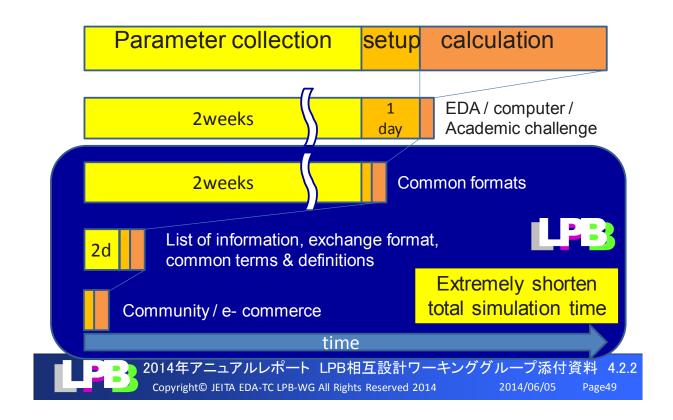

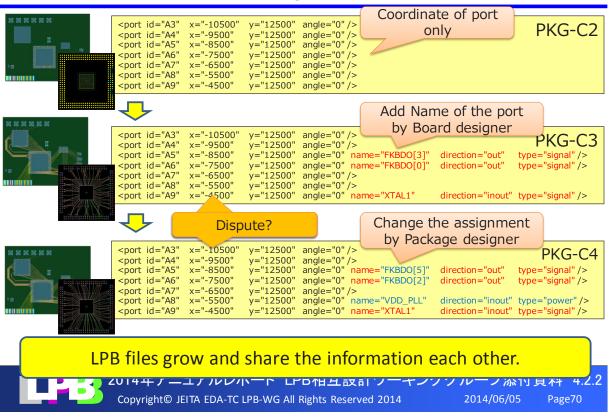

# Parameter collection setup calculation 2weeks EDA/ computer / Academic challenges 2weeks Common formats List of information, exchange format, common terms & definitions Extremely shorten total simulation time time

## simulation time reduction

図 2.3.1-3 シミュレーション時間の削減の概念

#### 2.3.1.2 LPB 相互設計解説

#### 2.3.1.2.1 LPB 相互設計 WG の目的とゴール

- 1、LPB が協力しあって設計を行う為の課題を抽出しその分析を行いソリューションの提案を 行う。

- 2、具体的には LPB 全体での接続記述、形状情報、解析設定条件に着目し、それらの定義や書式等の標準を開発する。

- 3、標準化提案内容は公開し普及を図る

- 4、これにより日本のエレクトロニクス製品の国際的競争力を高めることを目標とする。

#### 2.3.1.2.2 LPB 相互設計の概念解説 ~個別設計と相互設計~

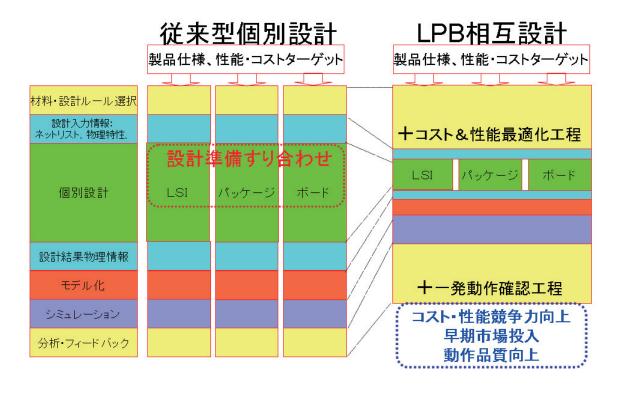

#### 2.3.1.2.2.1 従来型個別設計の概念

LPB相互設計がこれまでの設計思想と異なる点を説明しておく。

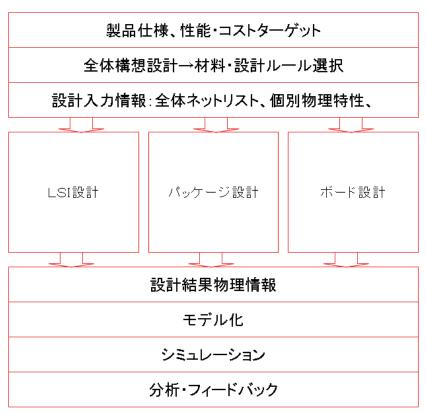

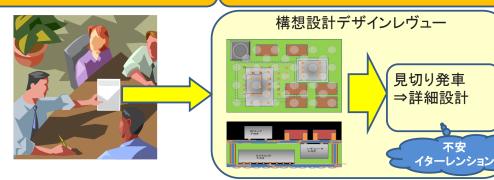

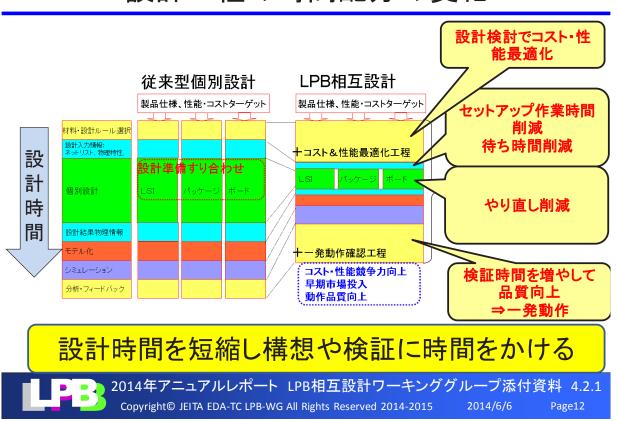

従来の設計手法は紙に書いたレベルの大まかなセットの製品仕様が決定されるとLPB別々に設計がスタートし、その個々分野内で最適化が行われてきた。これを個別設計という呼び方にここでは定義する。個別設計においてもLPBが完全に別々に設計が行われていたわけではなく当然すり合わせは行われてきたが場当たり的な確認が多く、また共通の認識も乏しいためにお互いの情報の公開・流通がし難い場合も多く、時間がかかるものであった。それでも日本企業においてはLPB各部門の設計力は高く、品質・特性といった面での差別化は図られていたといえる。しかしながら上記背景に述べたような市場要求の変化に対してこの方法では以下の問題に直面することになっている。(図 2.3.1-4)

- 1,全体最適化が困難

- 2, 設計解析の準備に時間がかかる

- 3, やり直しが発生し開発期間増大

- 4. リソースの重複

#### 従来型個別設計 従来 製品仕様、性能・コストターゲット 紙に書いた 材料・設計ルール選択 材料・設計ルール選択 材料・設計ルール選択 仕様書 設計入力情報: 設計入力情報: 設計入力情報: ネットリスト、物理特性<mark>、</mark>ネットリスト、物理特性、<u>ネットリスト、物理特性</u>、 パッケージ設計 ボード設計 LSI設計 設計結果物理情報 設計結果物理情報 設計結果物理情報 モデル化 モデル化 モデル化 シミュレーション シミュレーション シミュレーション 分析・フィードバック 分析・フィードバック 分析・フィードバック

図 2.3.1-4 従来型個別設計

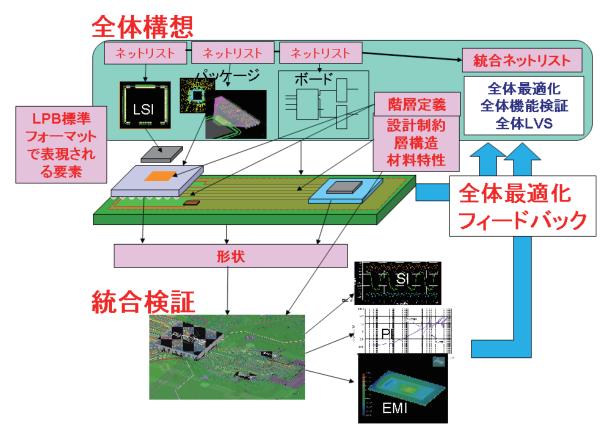

#### 2.3.1.2.2.2 LPB 相互設計の概念

個別設計の課題を克服する方法として LPB 各部門が協力しあって設計を進めるスタイルを相互

設計と定義する。相互設計においては全体構想設計を十分に行い各部の設計基準を設定し、その後は個々に設計を行う。設計終了後は全体を統合したシミュレーションを行い、設計のへのフィードバックを適所に行う。これにより下記の効果を期待する。(図 2.3.1-5)

- 1、全体最適化を可能にする。

- 2、設計・解析期間を短縮。

- 3、やり直しを最小に留める。

- 4、リソースの分担。

# LPB相互設計

図 2.3.1-5 LPB 相互設計

#### 2.3.1.2.2.3 EDA の面からみた LPB 相互設計

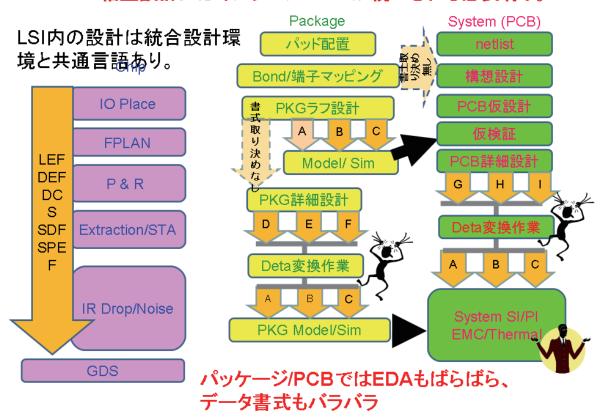

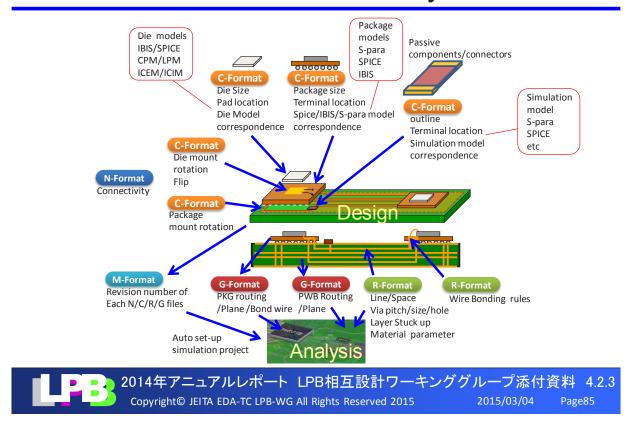

LPB 相互設計の内 EDA を使って設計検証する部分を考える

EDA が使われる工程の前段階では必ず入力データの準備がある。LPB 相互設計ワークグループの分析によると、この準備の段階において情報の流通が十分ではく、書式の違いがあり、EDAのセットアップに多大な時間を要しており相互設計の実現を阻む要因のひとつになっている。LSIの設計は比較的1つのEDAベンダツールでフロアプラン、詳細設計、検証、ECO(Engineering Change Oder)でまかなわれ、工程間のやりとりも統一書式(DEF など)がある。一方、パッケージやボードの設計では設計ツールと検証ツールは別々で、しかもツール間でデータの互換性はない。ベンダごとにもデータ書式はバラバラで、複数のEDAツールを駆使して最適な設計環境の構築には多大な投資と開発リソースが発生する。また、この流通性の悪さによりEDAツールをひとつのシステムから別のシステムに置き換えることの動機が削がれる。その結果一人のユーザーは同じシステムを使い続け、そしてEDAツールに対する改良要求は単一のものとなり

がちで、EDA ベンダは ROI を考慮すると改良を積極的に行わないという状況も発生する。結果的にその設計者の成果物は競争力を失い、事業整理と共に EDA ツールは購入されなくなってしまうという負のサイクルが生じる。

#### 2.3.1.2.2.4 競争領域と共通化領域

相互設計における競争領域と共通化するべき部分とを分類してみる。構想設計や設計、検証の作業は各社のノウハウなど機密内容が含まれる。それに比して EDA の入力部分は各社で共通化できる内容であり相互設計の実現を促進する効果が期待できることからこの部分について JEITA では共通仕様化を検討・推進することとなった。(図 2.3.1-6)

# 相互設計におけるEDA部分と共通化部分

図 2.3.1-6 相互設計におけるEDA活用部分と共通化部分

#### 2.3.1.3 LPB 相互設計共通仕様

#### 2.3.1.3.1 課題の整理

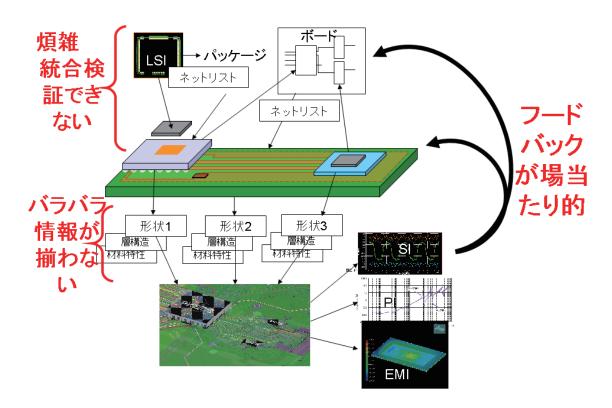

LPB 相互設計を行おうとすると多くの問題点に直面する。

1、LPBでネットリストが不統一

それぞれのネットリストのやり取りの際に変換をする必要があり、煩雑な上にミスが起きやすい。LPB が別々に設計変更を加える際に接続にフィードバックがかかり難くしばしば接続エラーが発生する。全体のネットを管理しないために全体での接続検証や機能検証など EDA を使ったアプローチが整備されない。すなわち、基準となるネットリスト(ゴールデン)が存在せず、個々の設計結果から個々のネットリストを更新することが多く、全体で接続に不具合があっても検出する手立てがない。

#### 2、LPBで設計結果の形状データが不統一

LPB で設計結果の出力データフォーマットは統一されておらず、これにより解析ツールへの読み込みが一元的に出来ないために全体解析を難しくしていた。別々なフォーマットは EDA ツールに読み込む際に、EDA ツール側に複数のフォーマットに対応する機能を整備することが必要でその準備に時間とコストが発生する。それぞれの書式に対するバージョンアップも常に対応し続ける必要があり管理コストも発生し続ける。また違う書式のデータは違った付加情報を必要とし、その情報収集にも多大な時間と労力を要しているのが現状である。(図 2.3.1-7)

## LPB相互設計にはインターフェースが統一される必要有り。

図 2.3.1-7 パッケージ・ボードはインターフェースが統一されていない

#### 3、LPBの合成が煩雑

LPB は別々に設計されるためにそれぞれの繋ぎあわせでミスが生じやすい。たとえば LSI チップのパッケージへの搭載おいてフリップ [裏表] やローテンション [回転角度] では頻繁に連絡ミスや誤解、思い込みで事故が起こる。パッケージとボード間でも同様のミスが発生することもある。解析ツール上で LPB を合成する際には画面を見ながら手作業で位置合わせや向き合せを行なって接続するのが常識的に行われている。これではミスは撲滅できない。

#### 4、設計途上の設計制約の・設計結果へのフィードバックの難しさ

LPB の間で設計制約に対する考え方がバラバラで、与える情報量・質・書式に差があることがある。これらは設計途上での誤解や追加の煩雑なコミュニケーションを生み、結果として確認待ち時間や反復的な設計やり直しによる時間のロスを生じることがある。一方、設計後も書式式の多様性やそれに伴うインターフェースの複雑化により検証結果を設計にフィードバック

するのも煩雑となり、フィードバックを避けて問題を残したままに妥協したり、比較的に簡単なところにのみフィードバックすることに留まって全体の最適化が進まない状況にも陥りやすい。(図 2.3.1-8)

図 2.3.1-8 インターフェースが統一されていないまま相互設計を行った場合の問題点

#### 2.3.1.3.2 標準フォーマットの作成

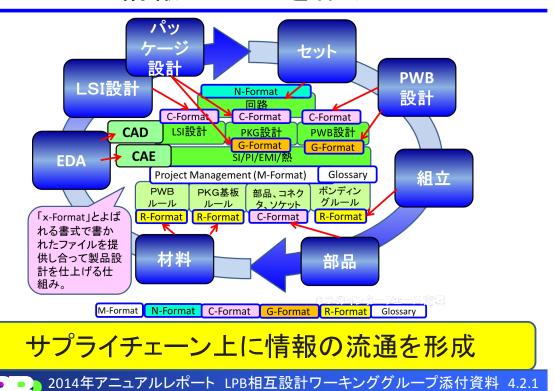

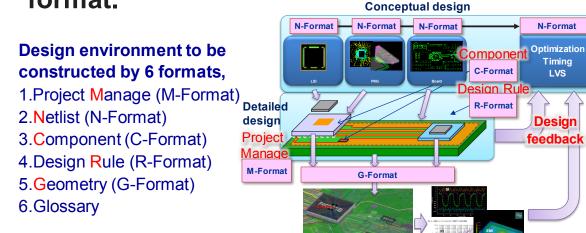

LPB 相互設計標準フォーマットを策定した。2010年の活動結果では下記5点を策定しV1.0としてリリースをしている。

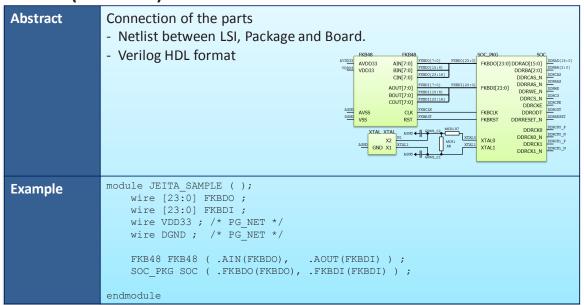

#### LPB-V1.0

- 1、ネットリスト: VerilogHDL の拡張(SPICE 制約互換)

- 2、階層定義情報:独自定義 XML 出力

- 3、設計制約情報:独自定義 XML 出力

- 4、設計結果形状情報 既存フォーマット

- 5、用語集

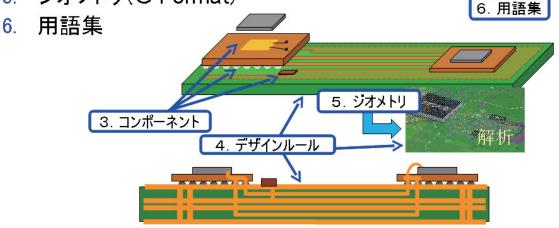

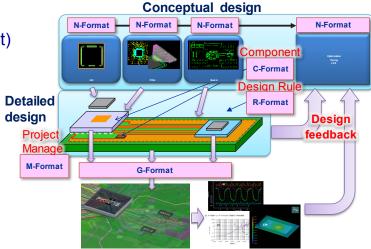

これに基づき 2011 年の活動で設計試行を行った結果、仕様の変更が必要となり LPB-V2.0 に改定を行っている。 (図 2.3.1-9)

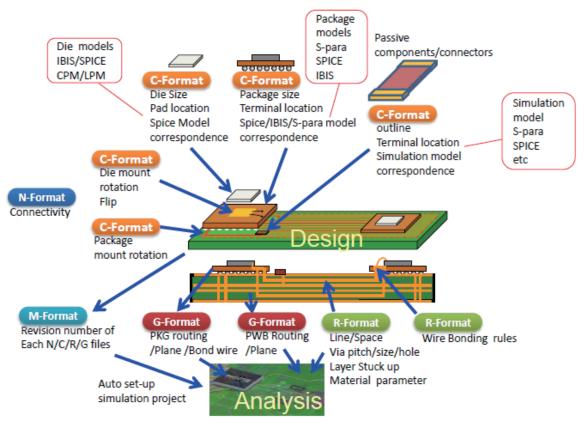

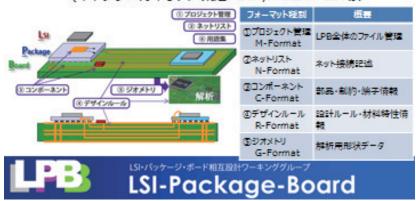

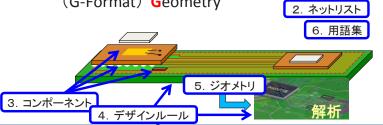

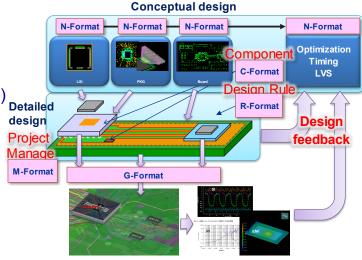

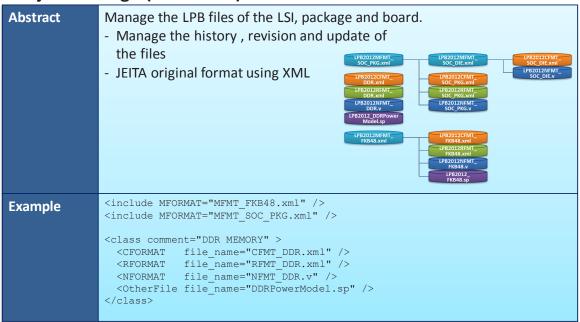

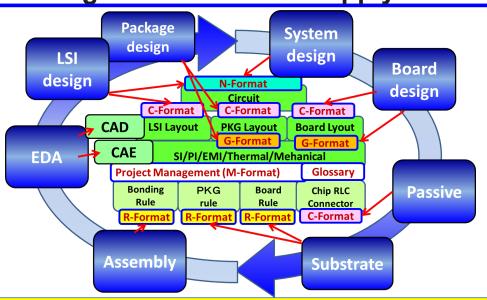

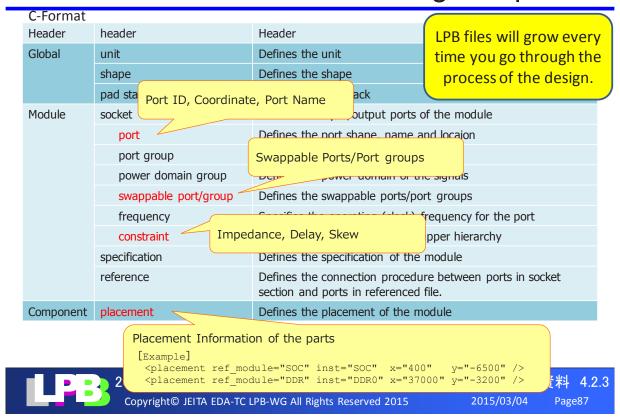

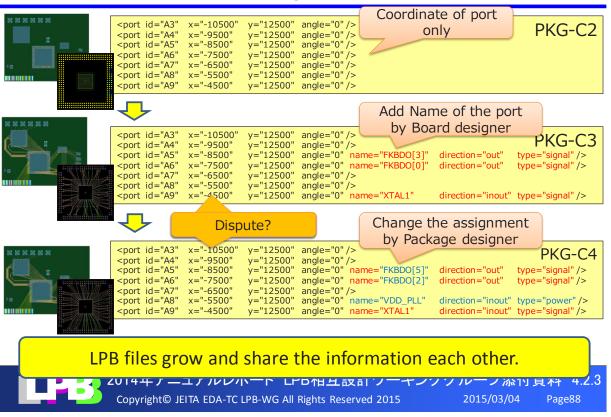

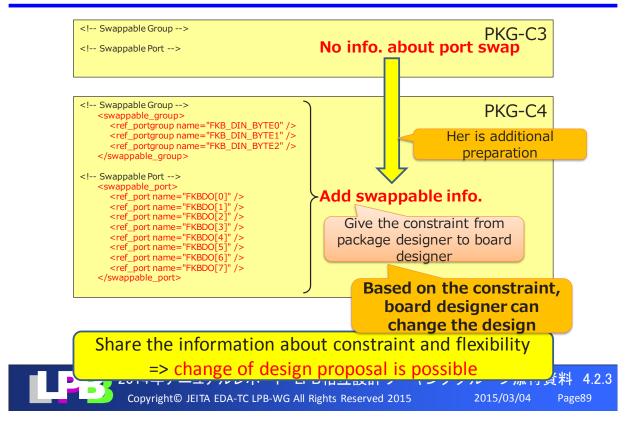

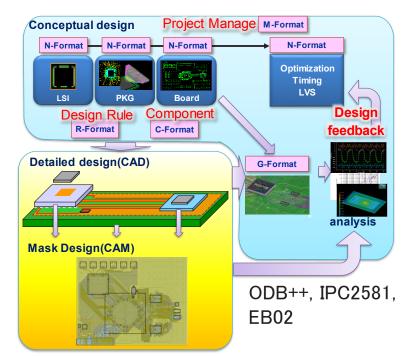

#### LPB-V2.0

- 1、プロジェクト管理 (M-Format)

- 2、ネットリスト (N-Format)

- 3、コンポーネント (C-Format)

- 4、デザインルール (R-Format)

- 5、ジオメトリ (G-Format)

- 6、用語集

LPB-1.0 から LPB-2.0 への大きな変更点は開発プロジェクトにおいてそれぞれのインターフェース標準フォーマットの履歴を管理する「プロジェクト管理」フォーマットの追加と、「階層定義」「設計制約」に記載される内容を大幅に改定し、「コンポーネント」「デザインルール」に仕分けなおしたことである。

2012年にはEDA ベンダへの採用とツールへの導入が進む過程で、フォーマットの齟齬の修正や 改良が必要となり LPB-V2.1 が作成され 2013年 3月にリリースした。LPB-V2.1 の構成は LPB-V2.0 と同じであり、各フォーマットが改定されている。

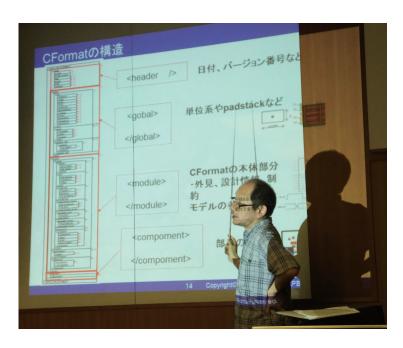

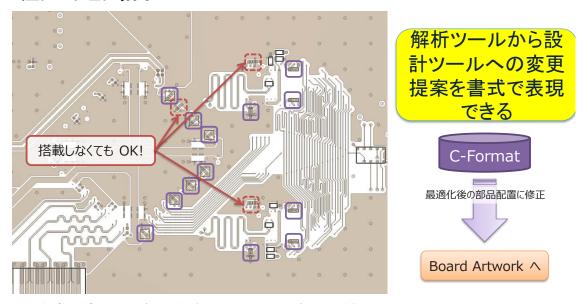

2014 年度になり、LPB フォーマットを国際標準とする活動を開始し、IEEE 標準化委員会において標準化作業を進めた(P2401 LPB-WG)。この結果、各種業界からの要望や、開発中の別な規格(IEC SC47A EMC シミュレーションモデル)との整合性などを考慮して、様々な仕様追加を行い 2015 年 3 月に LPB-V2.2 をリリースした。

## JEITA LPB標準フォーマットとして5つのファイルと用語集

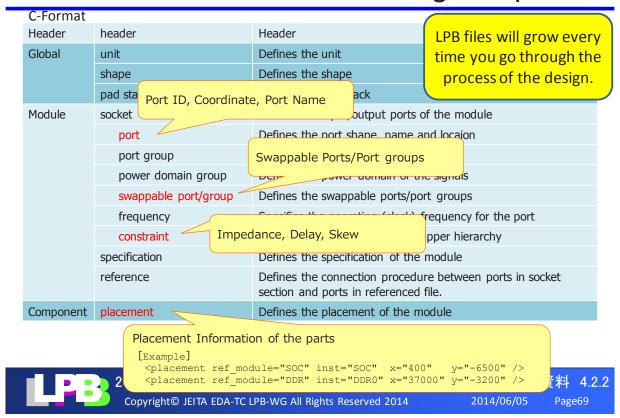

- 1. プロジェクト管理(M-Format)

- 2. ネットリスト(N-Format)

- 3. コンポーネント(C-Format)

- 4. デザインルール(R-Format)

- 5. ジオメトリ(G-Format)

1. プロジェクト管理

2. ネットリスト

6 田誕集

図 2.3.1-9 LPB 標準フォーマット

プロジェクト管理フォーマット: 製品の開発プロジェクトの中ではLPB それぞれに標準フォーマットに沿ってインターフェースファイルが準備されるが、それぞれの設計工程の最適化や改変によりインターフェースファイルも逐次アップデートされる。LPB 相互に連絡なしにファイルをアップデートすると設計結果に不整合がおこりミスややり直しの原因となる。システム全体でインターフェースファイルのバージョンを管理する目的でそれぞれのバージョン名を記述する。

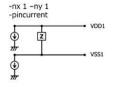

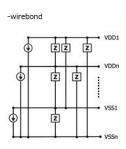

ネットリスト: LPB 全体での接続管理を目的とし、将来 LPB 全体の接続検証や機能検証ができる EDA 環境の開発が促進されることを狙って Verilog-HDL を基本ネットリストとした。形状

情報と完全に分離した接続情報に徹して階層構造にも柔軟に対処が可能である。IEEE に定められる Verilog-HDL には電源グランドのネットの定義がないことや、パッケージ・ボードの検証に使われている SPICE との互換性を持たなければならない。これらにより、LPB フォーマットでは Verilog-HDL の書式に電源グランド端子を追加し、SPICE におけるピン並びに制約と同じ制約を課す拡張仕様が加えられている。

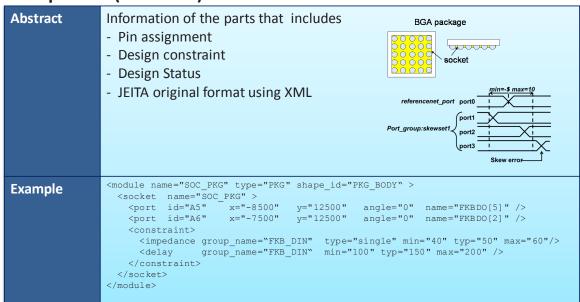

コンポーネント: コンポーネントファイルは LPB 各部の設計結果をつなぎ合わせる場合の 部品の物理的な形状、接続位置・方向、設計上の制約を定義する。流通している同様なフォーマットで必要となる情報がすべて包含されている書式がないため、本 WG で独自に書式を制定した。EDA ツールへの読み込みを簡単にするために XML の書式を採用している。

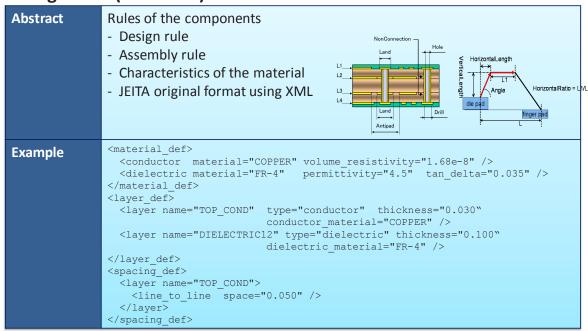

デザインルール : LPB 各部の設計ルールを記述する。ライン、VIAやスペース、層構成をあらわす。解析のセットアップの為の材料物理特性や詳細断面構造もあわせて定義する。流通している同様なフォーマットで必要となる情報がすべて包含されている書式がないため、本WG で独自に書式を制定した。EDA ツールへの読み込みを簡単にするために XML の書式を採用している。

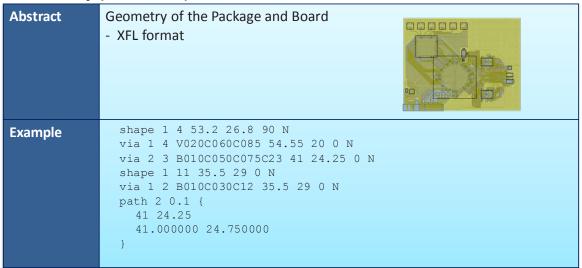

ジオメトリ : ジオメトリは設計結果を解析環境に渡す際の書式を定義する。各層ごとの 2 次元図形と、VIA, Bump, Bond Wireの 3 次元的情報、 2 次元情報を積み上げて立体構造にするための層構造(縦方向の寸法)などと記述する。テキストでの表現が必須であり、シンプルでかつある程度の精度をもった書式が必要である。これは独自の書式の開発は困難であることから EDA ベンダが提供した書式(XFL)を採用している。尚、このファイルはシミュレーションを行うために十分な形状情報のみに特化しており、製造の為の詳細な情報を加味することを目的としていない。したがってこのファイルだけでは製造コピーをすることは困難であることから需給間で設計情報を流通させる際の障壁を下げることも目的の一つである。

用語集 : LPB 各部の設計文化の違いにより同じ物理形状、材料などに対して別の表現をすることがある。たとえば Via は Via と呼ばれるだけではなく PTH など製造方法を表した表記がされることがある。この LPB 共通仕様の中では基本的にひとつの設計要素は1つの表記をするよう言葉の定義をしている。

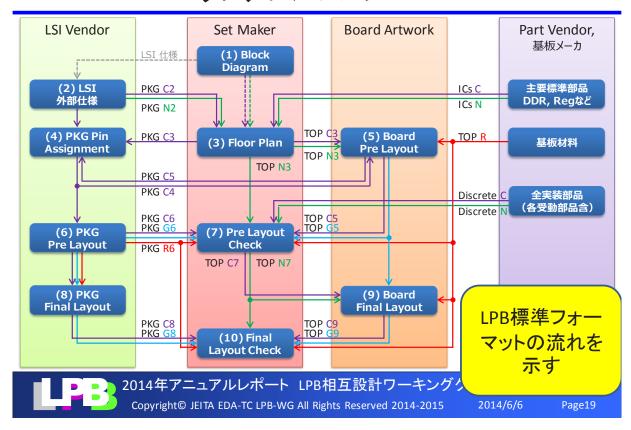

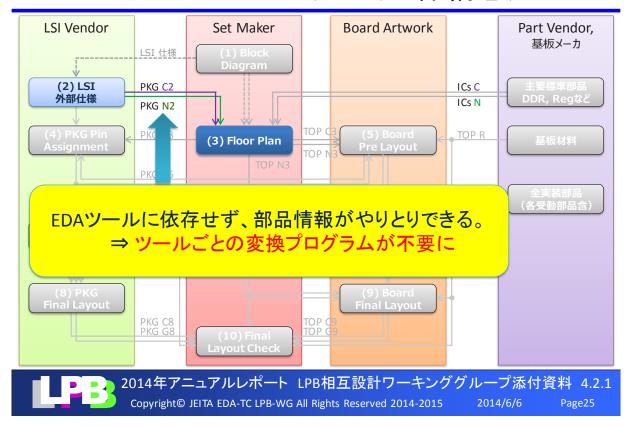

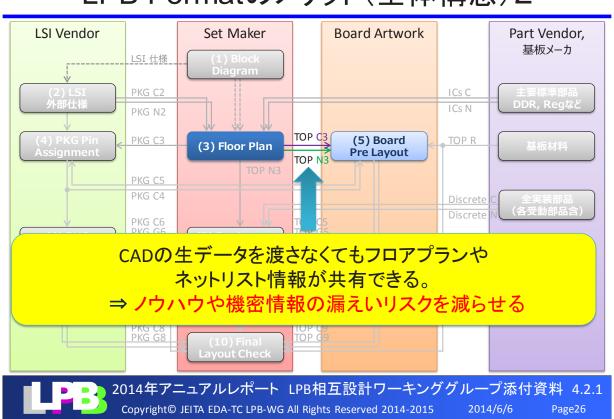

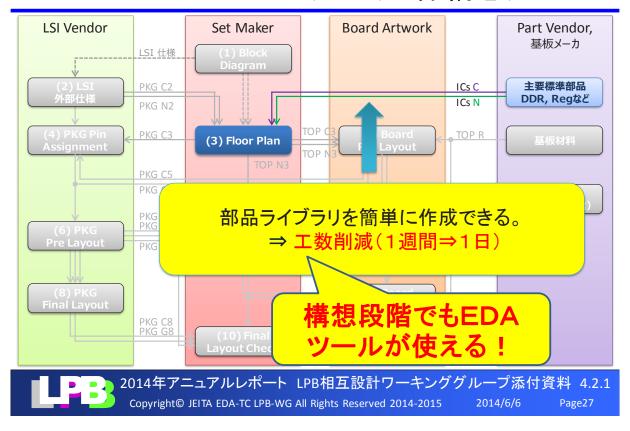

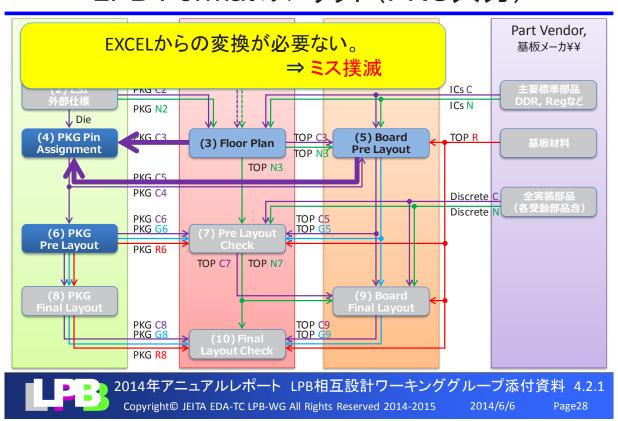

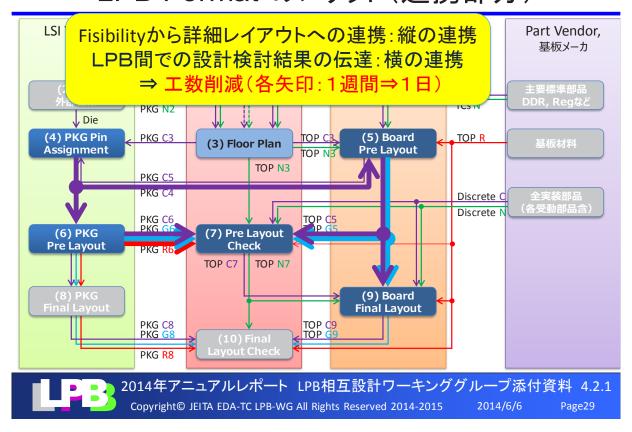

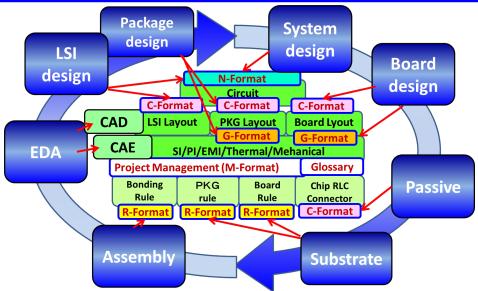

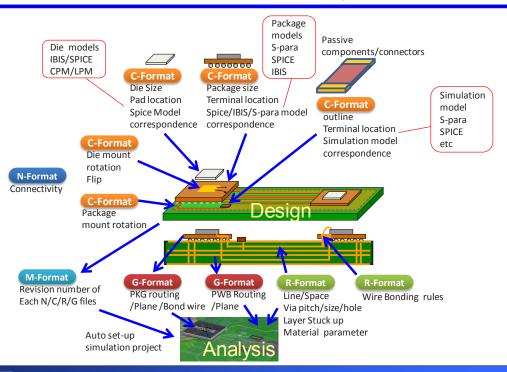

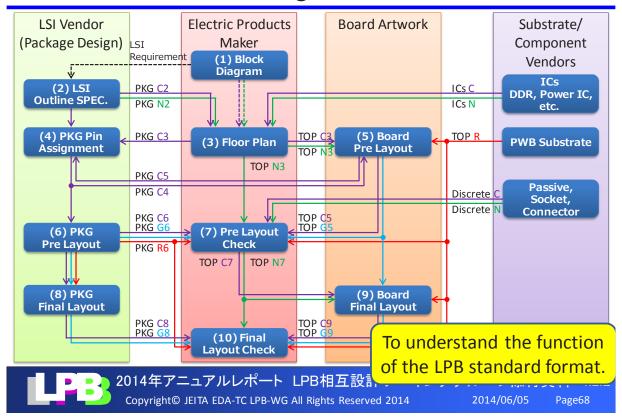

図 2.3.1-10 は具体的に設計のどの部分でどのフォーマットが使用されるかの概略を示している。

図 2.3.1-10 各 LPB 標準フォーマットの使われる部分の概略図

#### 2.3.1.3.3 LPB 相互設計標準フォーマットにより期待する効果

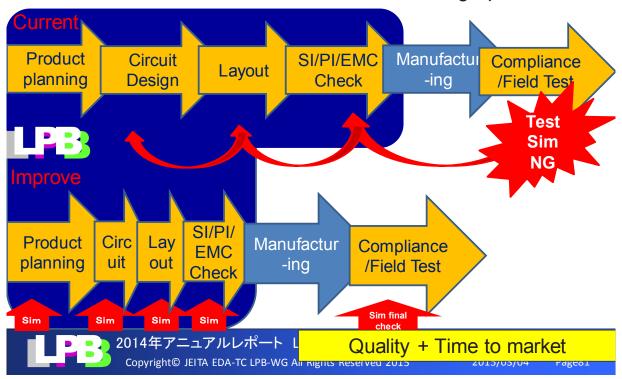

これまで詳細設計段階で「すり合わせ」が行われてきた。前述のように、これでは設計の最適化はLPB個々のレベルに留まる。また、「すり合わせ」が行われる時期は開発の工程の終盤になりがちであり、大きな手戻りには手遅れの場合が多い。標準フォーマットができると全体での情報伝達が容易になり、より早い段階で全体設計構想を練ることができることが期待される。全体構想設計が行われて、LPB各部の設計仕様が詳細設計前に明確化されることにより各部の個別の設計はやり直しの少ない短期間の設計完了が期待される。また解析も全体を見越した検討が可能となり、スムースにできれば解析にかける時間も取れるようになり、より深く吟味した設計フィードバック案が作成できる。また、構想設計と統合解析の関係が出来上がっていると、設計のフィードバックはLPBどの部分に適用するべきかを考察した上で行えるようになり全体最適化が促進されることが期待される。EDSFair2011Nov.でパネル討議を行った結果、半導体側からの期待値として設計前半の全体設計構想の部分を主導し、設計最適化を促進したいというコメントがあった。一方セット側のコメントとしては後半の統合検証がやりやすく、効率的に解析かつ、解析の項目を増やして製品の品質保証責任を果たせることを期待している。この設計スタイルが定着するとLPBの水平分業だけではなく、半導体とセットの開発分担という縦の分業も促進される。(図 2.3.1-11)

図 2.3.1-11 インターフェースフォーマットを整理した LPB 相互設計

この構想の元、LPB 相互設計共通仕様の効果を可視化する。縦方向を時間軸とみなして各工程の相対的な工程期間を示す。(図 2.3.1-12)

図 2.3.1-12 LPB 相互設計の効果 設計スタイルの変革

従来の個別設計に比較して相互設計のスタイルにおいては構想段階と分析・フィードバックの 段階に時間をかける代わりに実際の設計期間を短縮する。これらによりコスト・性能のバランス最適化と設計品質の向上を狙う。今まで時間のかかっていた設計・解析の準備にかかる時間も短縮する。これらにより全体の開発期間を短縮可能とし、完成品での不具合を減少させ結果として市場投入を早める。

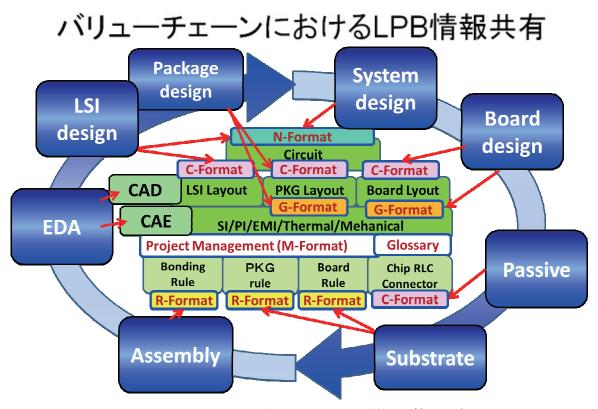

商品の市場での成功にはその時の市場にニーズにマッチした仕様の製品をいち早く市場投入することが重要であり構想設計をより早い段階で精度よく実施する必要がある。そのためには、開発に係る情報がそろっており、かつ直ぐに設計プロセスに使用可能な状況でなければならない。設計に係る情報とは LPB 各部分の設計結果だけでなく、設計に入る前に必要なデザインルールや材料の電気・物理特性、受動部品やコネクタなどの形状や電気モデル、組み立て (パッケージまたはボード) の際のルール (配置制約、ボンディングルール等)等、サプライチェーンから情報を集めなければならない。現状、それら情報の収集は人対人のコミュニケーションに大きく依存し、異種サプライヤー間で言葉の定義の違いによる相互理解にかかる余分な時間と、提供されたデータもそのまま設計ツールに読み込みができない書式であり、書式の合わせこみを行う時間が大きく発生している。これらが構想設計の実施を妨げ、時間不足となりいきなり詳細設計に入らなければならない状況を引き起こす。構想設計が不十分のまま詳細設計を行うとやり直しが多く発生する原因となる。情報のやり取りに LPB 標準フォーマットを活用することによって効率よく情報の収集や設計結果の提供ができるようになる。必要な情報は LPB標準フォーマットで明らかになっており、LPB 標準フォーマットで記載された情報ファイルを要求、または提出すればよい。(図 2.3.1-13)。

図 2.3.1-13 LPB 標準フォーマットを使った情報共有

また、あらかじめ材料、部品についての LPB 標準フォーマットによる情報ファイルを複数集め

ておき、構想設計の過程でどの材料・部品を使うか容易に試し選択することが可能となってくる。このようにサプライチェーンが協力し合って情報を集め、競争力のある製品を市場に出して成功すればサプライチェーン全体がエコシステムとして成功していく。このように一つ一つの情報が設計の価値を高めていくバリューチェーンが成立する。

#### 2.3.1.3.4 開発効率における JEITA LPB 標準フォーマットの効果実例

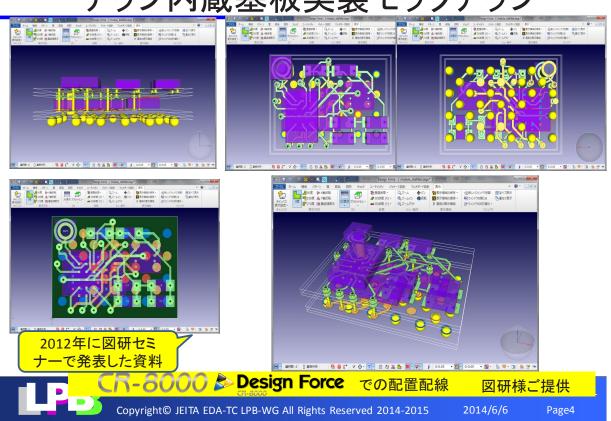

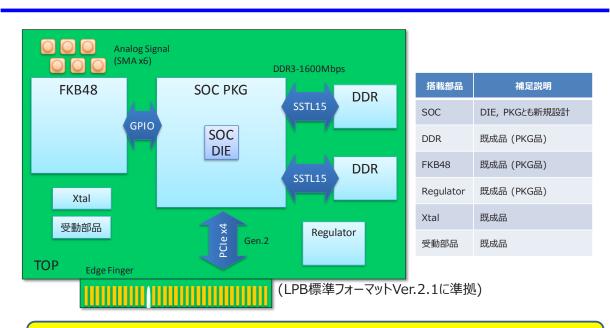

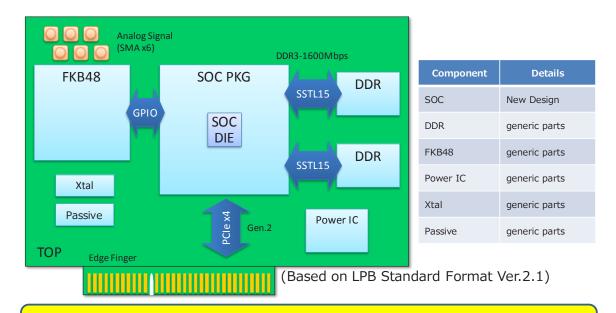

LPB 標準フォーマットによる設計効率の改善は(図 2.3.1-3)に概念を説明している。ここでは実際の事例によりどの程度の改善が見込まれるかを実験した。小規模な模擬セットを想定して LPB 標準フォーマットを使って実設計を行った(図 2.3.1-14)。この結果この程度の設計事例であっても従来の詳細設計や検証にかかっていた時間を 61%削減し、情報を待っている時間を 2 週間以上削減することが出来た。

## LPBメンバーによる設計事例

従来方式とLPBフォーマット方式、それぞれで実際に設計することで比較

作業時間 61%削減

待ち時間

2週間以上

削減

<u>■従来方式担当</u> キャノン

## **MLPB方式担当**

·Chip A

LSI : ソニー パッケージ : 富士通

ᄞ그

·Chip B

LSI : 東芝 パッケージ : 図研

<u>・ボード</u> : トッパンNEC

ハナソニック

・検証: デンソー

DDR<del>をモチー</del>フとして設計

Connector

Connector

Chip A

Cortroll

Vyet Lane (Bott)

Core - 1.2V

Experiment (Bott)

Core - 1.2V

Core - 1.

Chip A

Chip B

LPBフォーマットで仕様書やり取り

# -

## LPB標準フォーマットを適用することのメリットを確認。

図 2.3.1-14 LPB 標準フォーマットを使った設計事例とその効果

#### 2.3.1.4 LPB 相互設計ワークグループ活動

#### 2.3.1.4.1 構成メンバー (表 - 1)

2010年 16社/20名+特別委員3名 客員1大学/1名

2011年 17社/23名+特別委員2名 客員1大学/1名

2012 年 17社/21名+特別委員4名 客員1大学/1名

2013年 12社/20名

2014年 12社/22名

主查:福場義憲 株式会社東芝

副主査:大槻隆志 株式会社リコー (国際標準化サブワーキンググループ主査)

副主査: 永野民雄 ルネサスエレクトロニクス株式会社(標準化戦略サブワーキンググループ主査)

副主査:岡野資睦 株式会社東芝 (相互設計導入サブワーキンググループ主査)

表 2.3.1-1 LPB 相互設計ワーキンググループメンバー (2014 年度)

| 衣 2. 3. 1-1      |    | DI D THIS INTE          | プロキンググループメンバー (20) |                                |

|------------------|----|-------------------------|--------------------|--------------------------------|

| 氏名               | 正副 | 役職                      | 所属                 | 子会社                            |

| 福場義憲             | 正  | 主査                      | 株式会社東芝             |                                |

| 林 靖二             | 正  |                         | キヤノン株式会社           |                                |

| 村井裕典             | 副  |                         | イングが大芸正            |                                |

| 松澤浩彦             | 正  |                         | 株式会社図研             |                                |

| 古賀一成             | 副  |                         | W-VA LIZINI        |                                |

| 濱田誉人             | 正  |                         | ソニー株式会社            | ソニーLSI デザイン(株)                 |

| 川畑航              | 副  |                         | ) - WYA II         | ) - LOI / /   V (VN)           |

| 岡野資睦             | 副  | 副主查<br>相互設計導入<br>SWG 主查 | 株式会社東芝             |                                |

| 冨島敦史             | 副  |                         |                    |                                |

| 青木孝哲             | 副  |                         |                    |                                |

| 益子行雄<br>中途人見氏に交代 | 正  |                         | 日本ケイデンス・デザインシステムズ社 |                                |

| 人見忠明             | 正  |                         |                    |                                |

| 徳永真也             | 正  |                         | パナソニック株式会社         | パナソニックセミコンダクタ<br>ーソリューションズ (株) |

| 中川祐之<br>2月末まで在籍  | 正  |                         | 富士通株式会社            | 富士通 VLSI(株)                    |

| 松村宗明<br>2月末まで在籍  | 副  |                         |                    | 富士通セミコンダクタ(株)                  |

| 折原広幸             | 副  |                         | 富士通株式会社            | 富士通アドバンストテクノロジ(株)              |

| 大塚育生             | 副  |                         |                    | 田工地/   (                       |

| 澤田修              | 正  |                         | メンター・グラフィックス・ジャパン株 |                                |

| 門田和博<br>3月より加入   | 副  |                         | 式会社                |                                |

| 大槻隆志             | 臣  | 副主査<br>国際標準化 SWG<br>主査  | 株式会社リコー            |                                |

| 村田和希             | 副  |                         |                    |                                |

| 永野民雄             | 正  | 副主査<br>標準化戦略 SWG<br>主査  | ルネサスエレクトロニクス株式会社   |                                |

#### 2.3.1.4.2 活動内容

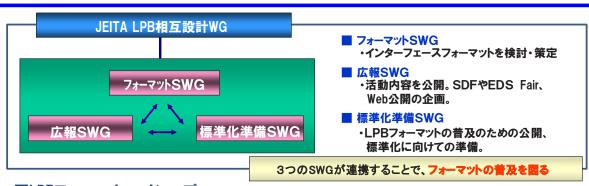

ワークグループ内で 3 つのサブワーキンググループ (SWG) を構成して活動をしている。2014 年度は下記 3 グループ。

- ①国際標準化 SWG

- ・LPB フォーマットの国際標準化として IEEE-SA P2401 委員会の運営を行う。

- ・IEEE P2401 国際標準のドキュメントを作成する。

- ②標準化戦略 SWG

- ・LPB フォーマットの改良・拡張案を考察する。

- LPB-V2.2 (IEEE P2401 対応)

- ・他規格との連携 リエゾン活動

- ・ LEN [LPB-EMC-Nano 世代] ジョイントワークグループ

- ③相互設計導入 SWG

- ・参加企業における導入支援

- 事例構築・発表。

- ・ LPB フォーラム

以上、3 つの SWG が協力しあって LPB 標準フォーマットの普及と国際標準化を促進する活動を 行っている。

活動は8回の本委員会を実施した(内2回は9月に集中討議として連日で行った)。本委員会や集中討議の合間にはSWGが複数回の委員会を行い、それぞれの役割における検討結果や成果を議案として本会議と集中討議に提出し討議と審議をおこなった。

また本活動を上位委員会の EDA 技術専門委員会への報告を行った。

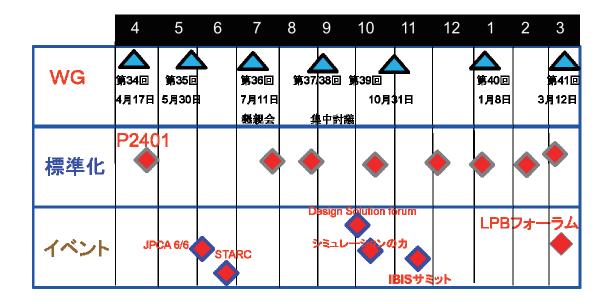

#### 本委員会日程

4月17日 (発足からの通算第34回)

5月30日(同第35回)

7月11日(同第36回)

9月5日 (同第37回)

9月6日 (同第38回)

10月31日 (同第39回)

1月8日 (同第40回)

3月12日 (同第41回)

(図 2.3.1-15)

図 2.3.1-15 LPB 相互設計ワーキンググループ活動記録 (2013 年度)

- ●国際標準化として IEEE P2401 を運営し、規格書第3稿まで作成した。

- ・先期 IEEE Standard Association (IEEE SA) 内にワーキンググループ P2401 を設置。議長に JEITA LPB 相互設計ワーキンググループ主査の福場が就任、国際幹事として JEITA EDA 技術専門委員会標準化担当の田中氏が就任した。また LPB 相互設計ワーキンググループ副主査国際標準化サブワーキンググループ主査の大槻氏がエキスパートとして参加することとなった。

7回の電話会議とフェース TO フェース会議を 3 月 4 日に米国 Mountainview, Freemont 市で行った。規格書は国際標準化 SWG で作成し、IEEE P2401 会議に提出し審議を行った。 3 回の改定を行って 3 月 4 日に第 3 稿を承認した。このドラフトに対してワーキンググループでの最終レヴューを行って 4 月 9 日に最終稿を完成(ワーキンググループ内の最終承認)させる予定である。尚、Face to Face meeting の際に、P2401 参加委員に対して LPB の紹介を行って理解を深めた。(添付ファイル 4.2.3 IEEE P2401 Face to Face meeting Mar.  $4^{th}$ , 2015 参照)

- ●IEEE P2401 に相応する LPB-V2.2 を策定してリリースした。

- ●IEC 東京大会にて SC47A/WG2 (11 月 13 日) の会議にオブザーバーとして LPB メンバーが参加した。目的は IEC SC47A/WG2 が策定中の EMC 用シミュレーションモデルが LPB フォーマットで取り扱いが可能かを検討することであった。結果、LPB フォーマット側で対処が必要とわかり、仕様の追加を行って LPB-V2. 2 および IEEE P2401 へ反映した。その後、IEC メンバーと電話会議を行い、IEEE P2401 のドラフト 3 (D3) に変更内容を含めることによって合意を得た。

- ●普及活動としてベンダーセミナーや実装学会での発表や展示会も積極的に行った。

- ・ JPCA ショー (発表) 内容は添付ファイル 4.2.1 部品内蔵基板とこれを支える設計技 術動向参照。

- ・ STARC セミナー (発表) 資料は IBIS サミットと同等の内容にて割愛

- Design Solution Forum (展示) EDA パンフレットを配布。

- ・ AET 主催シミュレーションの力 (発表&パネル討議) 資料は IBIS サミットと同等の内 容にて割愛

- ・ IBIS サミット USA (DAC) で1回、日本で1回 内容は添付資料 4.2.2 DAC IBIS Summit, San Francisco, CA を参照。日本の IBIS サミットも同等の内容にて割愛。

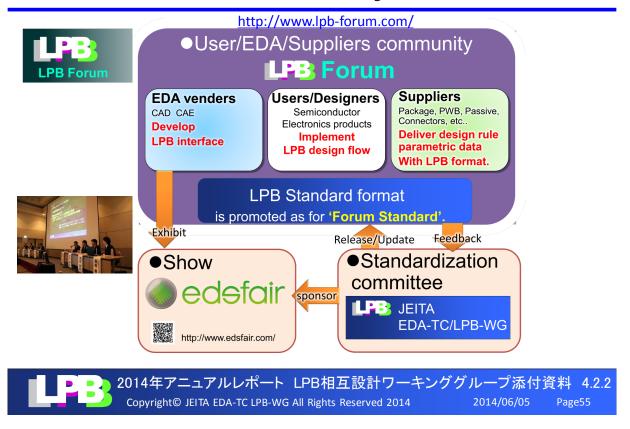

- ●LPB フォーラムは JEITA LPB-WG が主催し、ユーザー・EDA ベンダ参加の会合である。これま

でに4回開催している。本年度は2回開催した。

第 5 回 LPB フォーラム 9月 5 日 6 日の WG 会議と併設 EDA ツールのワークショップ 第 6 回 LPB フォーラム 3月 19 日 LPB フォーマットの紹介、国際標準化活動紹介、LPB 相互 設計フロー実例。LEN 発表、IBIS 委員会との連携、熱・EMC シミュレーション実例。

各活動の詳細はサブワーキンググループの項目を参照。

#### 2.3.1.4.3 今後の課題と活動方針

来年度はLPBフォーマットのIEEEでの国際標準化を完遂する。2015年末にIEEEでの最終承認を終えて正式発行を行う。その後、IECへ提案してIEC Dual Logoの取得を目指す活動に発展させる。

設計現場でのLPBフォーマットの活用はまだ始まったばかりである。国際標準化の主目的は標準によってEDAツールのインターフェースに採用され、ユーザー同士がツールをつかって情報の結合をしていくことである。市販 EDAツールないし、企業内(設計現場レベル)で運用されるローカルツールの入出力が統一されることによってファイル交換によって情報流通ができるようにすることがゴールとなる。LPBフォーラムにおいて一企業内での活用事例が示された。今後はそのようなローカルな現場レベルでの活用からサプライチェーン内にある企業間の情報流に発展させることが必要ある。このために、来年度はより多くの設計ユーザーに JEITA LPB 相互設計ワーキンググループやLPBフォーラムへの参加を呼びかけ、普及を促進する。2015 年度は以下の3つのアイテムを活動の骨子とする。

- 1. 国際標準化

- ▶ LPB 標準フォーマットを IEEE 標準として発行する。IEC への提案を開始 する。

- 2. 標準化戦略

- ➤ 実際の実施例が増え、これで明らかになってき仕様の不足部分のエンハンスを行う。LPB-V3.0 の検討を始める。: EMCや IBIS シミュレーションにおける活用の模索を LEN プロジェクトの継続で推進する。

- 3. LPB 相互設計導入推進

- ➤ 参加メンバー各社における LPB 標準フォーマットよる相互設計導入の支援を行う。(サンプルデータやリファレンスフローの充実。EDA ツールやサプライチェーンでの導入拡大推進等。)

以降サブワーキンググループごとの活動報告

### 2.3.2 国際標準化サブワーキンググループ

#### 2.3.2.1目的

#### 2.3.2.1.1 標準化の目的、背景

JEIATA LPB-WG においては、日本のエレクトロニクス製品の国際的競争力を高めることを大きな目標として掲げ、その実現において国際標準化は大きな意味を持つということをWGの一致見解とし、国際標準化 SWG が主体となって、LPB 標準フォーマットの国際標準化へ向けての活動を行っている。

#### 〈標準化の目的〉

- ■LPB 標準フォーマットの普及助長のための国際標準化

- ・LPB 標準フォーマットの更なる設計現場での活用を促進するための公的国際 標準化団体での公開。

- ・設計現場における LPB 標準フォーマットの活用による設計効率 UP。

- ■EDAベンダーからの強い要望

- ・EDAツールへのフォーマット採用に対する理由付け。

- ■JEITA LPB-WG としての成果物

## 2.3.2.1.2 国際標準化活動

昨年度、JEITA LPB 標準フォーマットとしての適合性、JEITA との連携性、公的影響度/普及性、その他を鑑み調査検討を行った結果、 JEITA LPB-WG としては、公的な国際標準化団体として IEEE を選択した。

今年度は IEEE での国際標準化を目標として、その実現に向けての具体的な活動計画、進め方を検討し、その内容に従って着実に標準化活動を実施。

#### 2.3.2.2 活動内容

#### 2.3.2.2.1 今年度活動項目

今年度の大きな活動項目として以下を実施。

- ■標準化へ向けてのステップの立案

- ・JEITA LPB-WG 国際標準化 SWG と IEEE P2401-WG のリンク

- Draft 作成ステップ

- ■JEITA LPB-WG 国際標準化 SWG における活動

- · Draft 内容検討

- Draft 作成

- ・Draft 内容審議/IEEE P2401-WG への提出

- ・Comment\_Sheet 内容の審議・/IEEE P2401-WG への提出

- IEEE P2401-WG における活動

- 月1回の国際会議

- ・Comment\_Sheet 内容の審議・承認

- ・Draft 内容審議・承認

#### 2.3.2.2.2 今年度活動内容

#### 2.3.2.2.2.1 標準化へ向けてのステップの立案

#### ■IEEEとIECの標準的ステップおよび期間

まず、IEEE と IECの一般的な標準化に向けてのステップを参考として記載する。

# Road to International Standard (IS) publication

To align and set strategies to achieve the target in a cost- and time-effective way

図 2.3.2-1 国際標準化への道のり

JEITA LPB-WG において優先活動として決定した国際標準化団体である IEEE については PAR(Project Authorization Request) Proposal から IEEE Standard まで 6 0 か月 (5年) である。

また、IEEE 標準化後には"IEEE-IEC Dual Logo Agreement"において IEC 標準化も目標としているが、通常 IEC の標準化については NP (New work item Propose) から International Standard までが 3 6 か月 (3年) となっている。

#### ■LPB 標準フォーマットの IEEE 国際標準化へ向けての具体的ステップ

IEEE における一般的な標準化までの期間は60か月となっているが、昨年度の活動であるDAC (Design Automation Conference)での JEITA LPB-WG活動の紹介、さらにその後の IEEE/DASC(Desigin Automation Standards Committee) キーマンとの直接対話におけるLPB標準フォーマットの重要性説明、理解により、IEEE における標準化大日程は以下を設定した。

|      | CY2013                                       | CY2014                          | CY2015                                                                                |

|------|----------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------|

|      |                                              | Jan.   Prepare to develop Draft | Review & Comment                                                                      |

| Jun. | Contact to IEEE                              |                                 | Mar. ◆ 3rd Draft Development  Apr. ◆ Final Draft Development/WG Vote  May ◆ DASC Vote |

| Aug. | PAR Creation (Project Authorization Request) | Sep. • 1st Draft Development    | ◆ Sponsor Ballot                                                                      |

|      | ◆ DASC approval                              | Review & Comment                | Recirculation Ballot                                                                  |

| Dec. | NesCom approval (New Standard Committee)     | Dec. • 2nd Draft Development    | Dec. • RevCom approval (Review committee)   IEEE   Standard !                         |

- ・標準化提案 (PAR)

- ・IEEE内におけるWG発足 (P2401-WG)

- •Draft作成準備 (IEEE Style)

- •Draft作成 (1st/2nd Draft)

- Review & Comment

- •Draft作成 (3rd/Final Draft)

- •Review & Comment

- ・IEEE上位組織での投票

- ·最終承認 (RevCom)

図 2.3.2-2 IEEE 国際標準化へのステップ

この大日程をベースとして、IEEE P2401 標準化活動および JEITA LPB-WG 国際標準化 SWG 活動の具体的な活動計画を立案。

IEEE P2401-WG 活動は月1回のペースで国際会議を実施することとなったが、基本的には、 JEITA LPB-WG 国際標準化S W G 活動はこの IEEE P2401-WG 活動計画にリンクさせ、Draft 内容 の検討、課題の抽出、対応についての議論を重ね、IEEE P2401-WG へのアウトプットとして各 ステップごとに Draft、Comment\_Sheet を作成、提出した。 具体的計画は以下のとおり。

|                          | Due   | Term<br>(weeks) | Circulation<br>end | Meeting  | Draft stage |

|--------------------------|-------|-----------------|--------------------|----------|-------------|

| P2401 kick off           | All   |                 |                    | 4/24     | >D1         |

| D1 Development           | JEITA | 13              | 7/24               | 7/24     | D1 vote     |

| D1 Review &comment sheet | All   | 4               | 8/21               | 8/28     | D1          |

| D1 Modification proposal | JEITA | 4               | 9/25               |          | D1          |

| Consensus for D2         | All   | 3.5             | 10/21              | 10/21    | D1>D2       |

| D2 intermediate report   | JEITA |                 | 11/6               |          | D2          |

| D2 Development           | JEITA | 6.5             | 12/4               | 12/4     | D2 vote     |

| D2 Review &comment sheet | All   | 4               | 1/8                | 1/8      | D2          |

| D2 Modification proposal | JEITA | 4               | 2/5                | 2/5      | D2          |

| Review proposal          | All   | 4               | 3/3                |          | D2          |

| Consensus for D3         | All   |                 |                    | 3/4(PST) | D2>D3       |

|                            | Due   | Term<br>(weeks) | Circulation<br>end | Meeting | Draft stage                  |

|----------------------------|-------|-----------------|--------------------|---------|------------------------------|

| D3 Development             | JEITA | 2               | 3/12               |         | D3                           |

| D3 Review - Comment sheet  | All   | 1               | 3/19               |         | D3                           |

| D3 Modification proposal   |       | 3               | 4/9                |         | D3                           |

| Review proposal            |       | 1               | 4/16               |         | D3                           |

| Consensus for final        |       | WG              | 4/23               | 4/23    | D3/Final                     |

| Final Document development |       |                 | 4/23               |         | Final Draft                  |

| Technical writer editorial |       |                 |                    |         | Revised<br>final<br>document |

| WG Vote                    |       |                 |                    |         |                              |

| DASC Vote                  |       |                 | 5/B                |         |                              |

| RevCon Vote                |       |                 | 12/B               |         |                              |

図 2.3.2-3 IEEE 国際標準化への具体的計画

#### ■Draft 作成ステップ

Draft 作成については D1~D3 の 3 ステップを設定した。

#### 〈D1 ステップ〉

IEEE 標準化へむけての Draft は JEITA LPB-WG で策定した LPB 標準フォーマット Ver2.1 をベースとし、まずは IEEE から発行されている標準作成のための Style Manual に従ったフォームとして 1st Draft(D1)を作成、および IEEE への提出。(2014/7/3)

D1 は主に IEEE 標準フォームとしての体裁を整えることを目的としたものではあるが、内容としては JEITA LPB-WG で議論し策定した LPB 標準フォーマット内容が忠実に反映されているものである。

D1 に対する審議は記述上の修正、追記がメインとなったが、LPB 標準フォーマット自体に対する使用上の改善等についても議論された。

それらの審議内容については Comment\_Sheet という形で記録を残し、その審議結果を D1 へ反映し、それを Draft (D2) として作成し、IEEE P2401-WG に提出。(2014/12/3)

#### 〈D2 ステップ〉

D1 ステップにおいて作成された 2nd Draft (D2) の内容に対する具体的審議を行い、それらの審議内容を 3rd Draft (D3 に反映することを目的とした。

審議内容としては、LPB 標準フォーマットの背景、目的、概要、メリット等設計現場における 設計者にとっての必要性、有用性等の説明内容、また実際に LPB 標準フォーマットを使ってい く上で参考となる使用事例説明内容を検討。

また、LPB標準フォーマット自体の更なる必要情報、改善点についても議論を重ね、さらには他標準におけるモデルとリンクするためのインターフェースフォーマット等、LPB分野における解析に必要な周囲環境とリンクするためのインターフェースフォーマットについても検討した。

これら審議された内容については D1 ステップと同様に Comment\_Sheet に記録として残し、それらの審議結果を D2 へ反映し、それを Draft (D3) として作成し、IEEE P2401-WG に提出。 (2015/3/5)

## 〈D3 ステップ〉

D2 ステップにおいて作成された 3rd Draft (D3)の内容に対する具体的審議を行い、それらの審議内容を Final Draft に反映することを目的とした。

Draft の審議としては最終ステップとなる。D3 ステップは現在進行中であるが、審議内容としてはD2 ステップで課題となっていた LPB フォーマットの設計現場での活用の参考となる事例内容についてとなる。

Final Draft 承認予定は 2015/4/23

#### 2.3.2.2.2. JEITA LPB-WG 国際標準化 SWG における活動

JEITA LPB-WG 国際標準化SWGにおいては、LPB 標準フォーマットの IEEE 国際標準化へ向けての Draft の作成を実施してきた。

Draft については JEITA LPB-WG で策定した LPB 標準フォーマット Ver2.1 をベースとし、 IEEE 標準である Style Manual に従ったフォームへのコンバートを行い、Draft 内容の検討、 課題の抽出、対応についての議論を重ねてきた。

今年度は JEITA LPB-WG 国際標準化SWGとしては計7回の会合を開催した。

### 2.3.2.2.2.1 国際標準化 SWG 活動履歴

上記ステップに対応し、JEITA LPB-WG 国際標準化 SWG において以下の日程で内容の検討をしてきた。

今年度は計7回の会合を実施。内容概略について以下に記す。

#### ■第一回 国際標準化 SWG 会合 (2014/5/8)

#### 〈内容〉

LPB フォーマットの IEEE 国際標準化へ向けての活動。

第一回は LPB フォーマットの IEEE 国際標準化へ向けてのベースとなる Draft 作成 に取りかかっていくにあたっての Style Manual 内容の確認、メンバー間の意識合わせ、および今後のA. I. について決定。

Draft 作成にあたり、各フォーマットに対する作成担当者を決定。各担当者により Style manual に従ったフォームで Draft 作成開始。作成完了は 6/13 を設定。

#### ■第二回 国際標準化 SWG 会合(2014/6/13)

〈内容〉

第一回 IEEE 国際標準化 WG 会合で擦り合わせた Draft 作成に向けての方針、 進め方に従って作成作業を実施しているが、7月3日の IEEE への Draft 提出にあた り、各フォーマットの Draft 作成進捗状況を確認するとともに、今後の進め方等に ついての調整実施。

#### ■第三回 国際標準化 SWG 会合 (2014/8/27)

〈内容〉

第二回 IEEE P2401 国際会議(2014/7/24)において、JEITA で策定した LPB フォーマットの Draft に対するコメントを"comment Sheet" に記載し、その内容 JEITA でまとめて IEEE 国際会議で議論していくことに決定。コメントのまとめは JEITA LPB-WG 国際標準化 SWG であり、今回は"comment Sheet" にアップされた内容の確認とまとめを実施。

#### ■第四回 国際標準化 SWG 会合(2014/9/24-25 集中討議)

〈内容〉

IEEE P2401 Draft D1 完了に向けて、D1 における修正内容範囲の確認、および具体的修正箇所についての議論を実施。

#### ■第五回 国際標準化 SWG 会合(2014/12/3)

〈内容〉

D2 ステージへの移行に伴い、D1 Draft に対して出されたコメント内容についての D2 Draft への反映内容についての議論を行い、D2 Draft を完成させることを目的とした。

#### ■第六回 国際標準化 SWG 会合(2015/1/7)

〈内容〉

Draft D2 を昨年末作成完了し、その内容に対するコメントを IEEE P2401 メンバーおよび JEITA LPB-WG メンバーから収集。

また、コメントに対する内容審議をまず国際標準化 SWG で実施し、最終承認は JEITA 本会合で行う。

今回はDraft D2の内容に対する1stコメントの審議を実施。

#### ■第七回 国際標準化 SWG 会合(2015/2/4)

〈内容〉

D2ステージにおいてはLPBフォーマットの実使用レベルでの具体的内容審議を 行い、修正、追記等の内容をコメントシートにまずは提案内容として記載。

D2 Draft 内容に対する修正、追加等の提案内容について JEITA 内で審議し、コメントシートとしてその内容をまとめた。

#### 2.3.2.2.3 IEEE P2401-WG における活動

昨年度 (2013/12/11)、IEEE における NesCom において LPB 標準フォーマットの標準化活動が承認され、その後に IEEE 内で正式に P2401-WG(LPB フォーマット)が発足した。

P2401-WG 発足に伴い、第一回目の IEEE P2401-WG 国際会議を 2014/4/25 に実施し、LPB フォーマットの IEEE 標準化活動が正式に Kick Off した。

当初、IEEE P2401 国際会議の開催ペースとしては JEITA からは3か月に一回という提案であったが、そのペースではインターバルが長いとのメンバーからの指摘があり、それを受けて1か月に1回のペースで会議を行っていくことになり、Draft 内容審議サイクルも1か月単位となった。

## 2.3.2.2.3.1 Draft 内容審議について

JEITA LPB-WG において策定した LPB 標準フォーマット Ver. 2.1 をベースにして、IEEE Style Manual (IEEE で定められた標準 Style) に従ったフォームに則り、1st Draft を JEITA LPB-WG において作成。

1st Draft は 2014/7/3 に IEEE に提出し、IEEE P2401-WG メンバーに公開。

第二回 IEEE P2401 国際会議(2014/7/24 開催) において、今後の Draft 内容審議の方法について議論が行われ、Draft の審議は3ステップ(D1/D2/D3)で実施していくことで合意され、それぞれのステップにおけるサイクルは以下の内容で実施していくことに決定。また、Draft に対するコメントは Comment\_Sheet に記載し提案することも決定。

Draft 内容審議スケジュールについては 2.3.4.2.2.1 における "LPB 標準フォーマットの IEEE 国際標準化へ向けての具体的ステップ "項を参照のこと。

### 〈各ステップにおけるサイクル内容〉

- ① Draft(D1/D2/D3) Development

JEITA LPB-WG による Draft 案作成、および IEEE への提出(P2401-WG メンバーへの

Draft 公開)

- ② Draft (D1/D2/D3) Review & Comment Sheet

①で提出された Draft に対する内容審議、および Comment\_Sheet へのコメント内容 記載、IEEE への提出 (P2401-WG メンバーへの Draft 公開)

- ③ Draft(D1/D2/D3) Modification Proposal②で提出された Comment\_Sheet の内容についての審議を行い、次ステップにおけるDraft への採用可否を決定

- ④ Consensus for Draft③で決定された内容の Draft への反映、および Draft の承認。ここで承認されると 次ステップへの移行となる。

Comment\_Sheet とは、以下の項目で構成されており、各ステップにおける審議内容の履歴となる。

| " Name <sup>1.</sup> | Line<br>number. | Clause/<br>Subclause. | Paragraph/<br>Figure/ | Comments. | Proposed change. | Observations . |

|----------------------|-----------------|-----------------------|-----------------------|-----------|------------------|----------------|

| a                    | (e.g. 17).      |                       | Table/                |           |                  |                |

Name/Line Number/Clause/Paragraph/Comment/Proposed Change/Observation

図 2.3.2-4 Comment\_Sheet 項目

#### 2.3.2.2.3.2 IEEE P2401-WG(LPB フォーマット) 国際会議活動履歴

上記 Draft 審議内容に従って、IEEE P2401-WG 国際会議を以下の日程および内容で実施。会議は米国と日本を繋いでの Conference Call で実施。

今年度は計8回の国際会議を実施。内容概略について以下に記す。

#### ■第一回 IEEE P2401-WG 国際会議(2014/4/25)

〈内容〉

IEEE での LPB フォーマットの標準化活動が承認されての最初の会合であり、標準化活動が正式に Kick Off した。

- ・メンバーの紹介および役割確認

- ・IEEE WG Policies and Procedures (P&P)の説明および承認

- Draft 作成について

- ・今後の計画について

#### ■第二回 IEEE P2401-WG 国際会議(2014/7/24)

〈内容〉

- ・First Draft(D1)は本会議にてオーソライズされた。

- ・まずはこの D1 に対するレビューを実施していく。

- ・レビューについては下記添付資料における"Comment\_Sheet"を使って進めていく。

- ・JEITA 側から提案した IEEE P2401-WG の大日程は基本的には3か月毎に開催する案であったが、それでは間隔が長いということで、臨機応変に Small Meeting という形で議論する場を設ける。

#### ■第三回 IEEE P2401-WG 国際会議(2014/8/28)

〈内容〉

- ・Draft D1 に対する Comment\_Sheet の作成

- Draft D1 の内容に対するコメントを JEITA 作成のコメントシートに記入し、IEEE CentralDesktop にアップロードする。 納期は 9/18

#### ■第四回 IEEE P2401-WG 国際会議(2014/10/21)

〈内容〉

- D1 ステージから D2 ステージへの移行は承認された。

- ・D2 Draft に反映させる内容のアウトラインを作成し、IEEE P2401-WG メンバーにアナウンスする。( $\sim$ 11/6)

- ・次のミーティングまでに D2 Draft を完成する。 $(\sim 12/4)$

#### ■第五回 IEEE P2401-WG 国際会議(2014/12/4)

〈内容〉

- ・D2 Draft の内容について説明。D2 Draft は承認された。

- D2 Draft の内容に対するコメントを D2\_Comment\_Sheet に記載する。 (~2015/1/5)

- ・RAMANUIA さん (Valeo 社)が IEEE P2401-WG メンバーとして新規参加する。

#### ■第六回 IEEE P2401-WG 国際会議(2015/1/8)

〈内容〉

- ・Draft D2 に対する Comment\_Sheet の内容の確認および審議

- ・今回のコメントシート内容として、Mentor John Park 氏から2件、JEITA LPB-WGから6件がコメントとして提出され、その内容の説明および採用可否について審議が行われた。

- ・上記コメントについては継続審議項目も含めて承認された。

- ・F2F ミーティングは 3/4 Freemont Mentor Office にて開催決定。

- ・引き続き、D2 Draft の内容に対するコメントを D2\_Comment\_Sheet に記載する。(~ 2015/2/4)

#### ■第七回 IEEE P2401-WG 国際会議(2015/2/5)

〈内容〉

- ・D2 ステージとして LPB フォーマットの実用化レベルでの具体的内容の審議

- ・今回のコメントシート内容として、前回提案された Mentor John Park 氏からの Encryption に関する継続審議案件 1 件、JEITA LPB-WG からの前回からの継続審議 案件 1 件、新たな提案 12 件がコメントとして提出され、その内容の説明および採用可否について審議が行われた。

- ・F2F ミーティングは 2015/3/4 14:00-17:00 (PST) Freemont Mentor office で 開催されることが決定

#### ■第八回 IEEE P2401-WG 国際会議(2015/3/5)

〈内容〉

本会合は IEEE P2401-WG における米国メンバーとの Face to Face ミーティングとなり、Freemont Mentor Office で開催された。日本からは P2401-WG Chairman 福場氏、Secretary 田中氏が参加。

- ・LPB フォーマットについての概要、メリット、事例等について説明

- · Comment Sheet 内容審議

- ・Draft D3内容については本会議で承認。

#### 2.3.2.3 国際標準化へ向けての今後の予定

IEEE P2401-WG 活動においては、現在 Draft D3 が承認され、Final Draft ステージに移行した。

Final Draft が承認されると、DASC (Design Automation Standard Committee) において Draft に対する Voting が行われ、その後 Sponsor Ballot へ移行し、最終ステップである RevCom Final へと進み、そこでの承認により IEEE 標準となる。

主なステップは以下のとおりである。

- Final Document Development/Final Draft Vote → 4/23

- ·DASC Vote → 5/B 予定

- MEC and Sponsor Ballot Invitation

- Sponsor Ballot

- Recirculation 1 Ballot

- Recirculation 2 Ballot

- Submit to RevCom & Final Recirculation(if necessary)

- ・RevCom Final → 12/7予定

## 2.3.2.4 国際標準化 SWG 参加メンバー

表 2.3.2-1 LPB 相互設計国際標準化サブワーキンググループメンバー (2014 年度)

| ·    |       | · ·              |

|------|-------|------------------|

| リーダー | 大槻 隆志 | 株式会社リコー          |

| メンバー | 福場 義憲 | 株式会社東芝           |

| 同    | 田中 玄一 | ルネサスエレクトロニクス株式会社 |

| 同    | 青木 孝哲 | 株式会社東芝           |

| 同    | 中川 裕之 | 富士通株式会社          |

| 同    | 大塚 育生 | 富士通株式会社          |

| 同    | 永野 民雄 | ルネサスエレクトロニクス株式会社 |

| 同    | 岡野 資睦 | 株式会社東芝           |

| 同    | 川端 航  | ソニー株式会社          |

| 同    | 富島 敦史 | 株式会社東芝           |

#### 2.3.3 LPB 相互設計WG 標準化戦略サブワーキンググループ

#### 2.3.3.1 目的

LPB 相互設計 WG で、LPB を統合的に扱う設計環境の実現に向け、その課題の分析をする中で、LSI、Package、Board の設計・解析で扱うツールが異なり、データフォーマットが異なること、さらに、Package、Board の設計・解析環境では、EDA ベンダ間でデータフォーマットが統一されていないため、必要情報が揃わない、設計・解析のセットアップに膨大な時間とリソースがかかる、結果が共用できない、といったことが明らかになった。

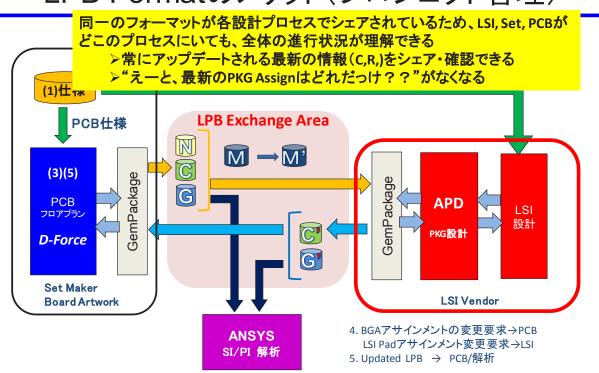

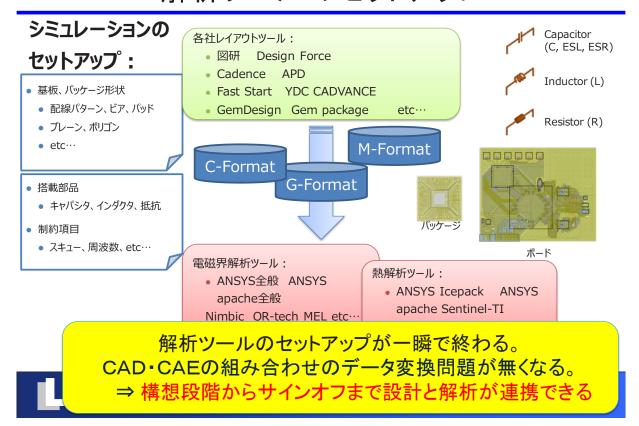

そこで、ツール間のデータフォーマットの統一を検討するサブワーキンググループを立ち上げ、①LPB 全体の管理、②接続記述、③部品・制約・端子情報、④設計ルール・材料特性情報、⑤解析用形状データのフォーマットを『JEITA LPB 標準フォーマット』として策定した。また、JEITA LPB 標準フォーマットの理解を深めるため、LPB 相互設計の一例として『Reference Flow』を定義、それぞれの作業の間でどのようなファイルの受け渡しが行われるか、および EDA 開発に使えるテスト用のデータとして『Golden Sample』を整備・拡充している。

サブワーキンググループは2010年度より継続して活動しており、

2010 年度 LPB 標準フォーマット Ver. 1.0

2011 年度 LPB 標準フォーマット Ver. 2.0

2012 年度 LPB 標準フォーマット Ver. 2.1

Golden Sample Ver. 1. 0

2013 年度 Reference Flow Ver. 1.0

Golden Sample の拡充 (Reference Flow の途中段階のファイル作成)

としてリリースしている。

LPB 標準フォーマットは、2012 年度にリリースした Ver. 2.1 を基に IEEE P2401 で標準化を進めている。2015 年に標準化する上で、記述の見直しや追加要望に応じてフォーマットを修正、標準化へ提案するバージョンとしてまとめる必要がある。一方、Ver. 2.1 としてまとめる時点で課題として見送った機能があることや、Ver. 2.1 を策定した 2012 年度以降に、LPB フォーラムの参加者など LPB 相互設計 WG 外の方々からもご意見をいただいており、より実設計に使えるような工夫・発展を継続的に行う必要もある。そのため今年度は、他規格との連携・リエゾン活動を通じ意見収集を行い、

- 1. LPB 標準フォーマット Ver. 2.1 の標準化対応 IEEE P2401 での標準化活動に対応し、記述の見直しや追加要望に対する具体案を作成、 標準化として提案するバージョンを策定し、Ver. 2.2 としてリリースする。

- 2. LPB 標準フォーマットの拡張案の検討 Ver. 2.1 を策定する際に見送った内容や、LPB フォーラム参加者など WG 外からいただい た意見要望を整理・検討し、Ver. 3.0 への対応案としてまとめる。

を目的に活動を行った。

#### 2.3.3.2 活動内容

#### (1) LPB 標準フォーマット Ver. 2.1 の標準化対応 (Ver. 2.2 のリリース)

表 2.3.3-1 は LPB 標準フォーマット一覧を示す。LPB 標準フォーマットは、(1) プロジェクト管理 (M-Format)、(2) ネットリスト (N-Format)、(3) コンポーネント (C-Format)、(4) デザインルール (R-Format)、(5) ジオメトリ (G-Format) の 5 種類のファイルで構成されている。

表 2.3.3-1 LPB 標準フォーマット

| フォーマット種別    |          | 概要           | フォーマット書式                       |

|-------------|----------|--------------|--------------------------------|

| (1)プロジェクト管理 | M-Format | LPB全体のファイル管理 | XML (独自)                       |

| (2)ネットリスト   | N-Format | ネット接続記述      | Verilog-HDL(既存)※電源・GNDはコメントで注記 |

| (3)コンポーネント  | C-Format | 部品·制約·端子情報   | XML (独自)                       |

| (4)デザインルール  | R-Format | 設計ルール・材料特性情報 | XML (独自)                       |

| (5)ジオメトリ    | G-Format | 解析用形状データ     | XFL Ver.1.0(既存)                |

表 2.3.3-2 は、各フォーマットの Ver. 2.1 からの変更点をまとめたもので、Ver. 2.2 では(1) プロジェクト管理(M-Format)、(3) コンポーネント(C-Format)、(4) デザインルール(R-Format) を見直している。(2) ネットリスト(N-Format)、(5) ジオメトリ(G-Format) については(提案不採用も含め)変更はなかった。

表 2.3.3-2 各フォーマットの Ver. 2.1 からの変更点

| No. | Format   | 内容                                                                       | Ver.2.2 対処                                                                                     |

|-----|----------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 1   | C-Format | 単位系の見直し、及び単位にインチを許可する                                                    | ⇒ 採用 長さの単位だけ許可、要素「distance」に値「inch」「mil」を<br>追加、ただし、SI接頭辞は不可とする                                |

| 2   | C-Format | 要素「padstack」の属性「type」の値「DIE_PAD」<br>「BOND_PAD」を本文にあわせ修正するか               | ⇒ <mark>採用</mark> 属性「 <i>type</i> 」を削除する                                                       |

| 3   | C-Format | モジュール内部に接続しないPortを許可する                                                   | ⇒ 採用 要素「Port」の属性「type」に値「through」を追加                                                           |

| 4   | C-Format | リファレンスのformatにVHDLを追加する                                                  | ⇒ 採用 要素「format」に値「VHDL」を追加                                                                     |

| 5   | C-Format | リファレンスのformatに、ICEM対応として、XML記述自<br>体をサポート、モデル種指定を追加する                    | ⇒ 採用 属性「format」に値「XML」を追加 モデルの種類を指定するオプション属性「type」とその値 「ICEM-CE」「ICEM-RE」「ICIM-CI」「ICIM-RI」を追加 |

| 6   | C-Format | 暗号化の機能を追加する                                                              | ⇒ 採用 W3C勧告のXML Encryptionを用いることを適用例として追加                                                       |

| 7   | C-Format | 要素「placement」がどの要素「module」に対するものなのか不明                                    | ⇒ 採用 最初の要素「module」が対象となる 本文に追記                                                                 |

| 8   | M-Format | 要素「class」の属性「log」が不要                                                     | ⇒ 採用 属性「log」を削除する                                                                              |

| 9   | R-Format | 単位系の見直し、及び単位にインチを許可する                                                    | ⇒ 採用 長さの単位だけ許可、要素「distance」に値「inch」「mil」を<br>追加、ただし、SI接頭辞は不可とする                                |

| 10  | R-Format | 要素「padstack」の属性「type」の値「DIE_PAD」<br>「BOND_PAD」を本文にあわせ修正するか               | ⇒ <mark>採用</mark> 属性「 <i>type</i> 」を削除する                                                       |

| 11  | R-Format | M-Formatで紐付けられたR-FormatのルールがC-<br>Formatのどの要素「 <i>module</i> 」に適用されるのか不明 | → 不採用 全部に適用される 本文の変更なし                                                                         |

| 12  | G-Format | PartのPinの形状指定の「padstackID」がオプション扱<br>いとなっているが、必須項目にすべき                   | ⇒ 不採用 解析ツール都合のため不採用                                                                            |

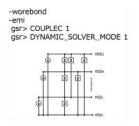

この内、No. 5 C-Format の ICEM 対応については、現在 IEC で EMC モデルの標準化として取組 みが行われている「ICEM-CE」「ICEM-RE」「ICIM-CI」「ICIM-RI」に対応するものであり、ICEM-CE 自体は XML で記述された IC やパッケージのモデルである。LPB 標準フォーマットの内、コンポーネント情報を扱う C-Format に、外部モデルを参照し物理情報(端子)に紐付ける機能(リファレンス記述)があるため、そのリファレンス記述の対応フォーマットに XML を加えることで ICEM-CE を参照できるように修正を実施した。対応案と記述例を表 2.3. X-3 に示す。

表 2.3.3-3 ICEM 対応

## C-FormatのリファレンスICEM対応

指定方法: format="XML" type="ICEM-CE"などを追加

port\_pathに「XML Path Language」準拠で指定する

長所:XML形式であれば何でもOK、モデル種が増えてもLPBは対応不要短所:指定が面倒、指定ミスのリスク大、LPBの記述変更(type追加)

<referencexmlns:xml="http://www.jeita.or.jp/LPB/xml" reffile="XXXX.xml" format="XML" type="ICEM-CE">

<connection socket\_name="socket1" port\_id="A1">

$\label{lem:constraint} $$ \operatorname{sml:ref\_port\ port\_path} = ''/\operatorname{Cemodel/Lead\_definitions/Lead[@Id='1']''} / > </\operatorname{connection} > $$$

<connection socket\_name="socket1" port\_id="A2">

<xml:ref\_port port\_path="/Cemodel/Lead\_definitions/Lead[@Id='2']"/>

</connection>

<connection socket\_name="socket1" port\_id="A3">

<xml:ref\_port port\_path="/Cemodel/Lead\_definitions/Lead[@Id='3']"/>

</connection>

</reference>

なお、本修正案は、今年度の取組みとして行った他規格との連携・リエゾン活動「LPB-EMC-Nano 共同 LEN プロジェクト」において、JEITA-半導体部会-半導体製品技術標準化委員会-集積回路製品技術小委員会-半導体 EMC サブコミッティに、ICEM の紹介・内容説明、対応案の精査など、ご協力いただいている。

### (2) LPB 標準フォーマットの拡張案の検討

表 2.3. X-4 は Ver. 2.1 策定時に見送った機能や、2012 年度以降 LPB フォーラムの参加者など LPB 相互設計 WG 外の方々からもご意見をいただいた意見要望を整理し、その対応案をまとめたものである。 Ver. 2.2 で対応・修正したものも含まれている。

表 2.3.3-4 Ver.3 へ向けた拡張案

| No. | Format   | 内容                                                                                                                                                             | Ver.3 対処                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | C-Format | frequencyの用途不明。<br>また、仕様の記述が、「概要」と「詳細」で合っていない<br>(C-Formatの「概要」タブでは、 <specification>内<br/>で定義されているが、「詳細」タブ内では、<socket>内<br/>で定義されている。</socket></specification> | クロックを想定していて、PKG側に端子の出力情報として与えているだけ?<br><specification>に入れた方が良い?<br/>入力としての制限であるならば設計制約に入れるべき?<br/>最終的な結論は先送り<br/>⇒ 解決済み</specification>    |

| 2   | C-Format | アナログ電源のリップル率など、電圧のmin/max以外の表現ができない                                                                                                                            | 必要性含めて検討する ⇒ 採用 リップル率:出力の規格として(Portの属性)か、入力の許容値として(power_domainの属性)か検討要 恐らく出力、継続検討                                                         |

| 3   | C-Format | swappable の意味                                                                                                                                                  | port入れ替え(I/Oセル入れ替え)可能となる表記を検討する ⇒ 採用 swappableではなく、未決定を表す属性を追加 キーワードは継続 検討                                                                 |

| 4   | C-Format | KEEPOUT領域が指定できない                                                                                                                                               | 検討する (R-Formatも含めて)  ⇒ 採用 要素moduleの中で定義する Keepoutの対象は継続検討                                                                                  |

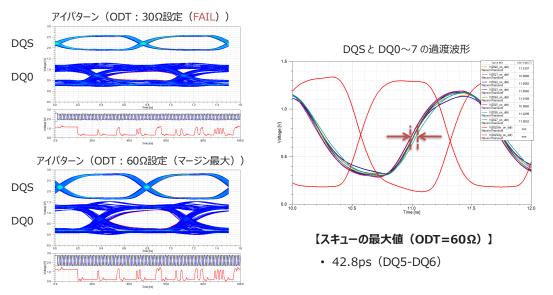

| 5   | C-Format | 差動信号のSkewを定義するとき、Groupでmax.を定義すると、Pos-Negどっちがどっちかわからない。PKG-PCBでの帳尻合わせをする場合 コントロールできない。                                                                         | port の部分にskewを記載し、制約の部分は変えない<br>というやり方はいかがか?<br>⇒ 採用 portgroupに差動属性を追加、Pos/Negの属性も追加、指定する                                                  |

| 6   | C-Format | C-FormatにはLayer定義が無いため、Layer指定が<br>できない<br>- padstack の ref_shape<br>- component の placement                                                                   | 部品内蔵等含めた対応を考える  ⇒ 採用 要素mountに値「MIDDLE」追加、基準面からのz方向の順番の属性を追加、ユーザが値「正の整数(TOPとBOTTOMは外に向かって数字が大きくなる、MIDDLEはTOP側からの順番とする)」を指定する                |

| 7   | C-Format | 次の設計フェーズに移れるかなど、判断結果の記述「Fixed」「Locked」などのプロパティを付けるか                                                                                                            | 全フォーマット対象、エレメントに指定、下位エレメントを含む<br>⇒ 採用 キーワードは継続検討                                                                                           |

| 8   | C-Format | Portのアトリビュートに内部に接続しないスルーを追加                                                                                                                                    | ⇒ 採用 Ver.2.2で対応                                                                                                                            |

| 9   | C-Format | 差動信号の専用定義                                                                                                                                                      | → 採用 No.5と同じ                                                                                                                               |

| 10  | C-Format | Power_domainで電源とGNDのペアとして指定できない                                                                                                                                | ⇒ 採用 power_domainを要素「power」「ground」に分け、それぞれに<br>属性portと属性min/typ/maxを指定する 複数指定可とする                                                         |

| 11  | R-Format | Bonding Padを長円で表現できない                                                                                                                                          | 検討する<br>⇒ <mark>不採用</mark>                                                                                                                 |

| 12  | R-Format | Die Pad層を三次元的に正い表現できない                                                                                                                                         | 必要性含めて検討する<br>⇒ <mark>不採用</mark>                                                                                                           |

| 13  | R-Format | モールドの高さ定義が不明確                                                                                                                                                  | 高さ基準を変更できるようにするか検討する  ⇒ 不採用                                                                                                                |

| 14  | R-Format | KEEPOUT領域が指定できない                                                                                                                                               | 検討する (C-Formatも含めて)<br>⇒ 採用                                                                                                                |

| 15  | R-Format | bondingwire_def と ball_def で英語表記方法が<br>異なる                                                                                                                     | 機を見て見直す<br>⇒ 採用 対応済み                                                                                                                       |

| 16  | R-Format | デザインルールのエリア指定など、ユーザ由来と製造由来との区別<br>複数(ファイル)のエリア指定の場合の優先度                                                                                                        | ⇒ 採用 優先順位を付ける属性を追加する 値は正の整数(大きい方が優先)<br>省略可能、省略時は「default」エリアは「0」、それ以外のエリアは「1」とする<br>同値の複数ルールは包含のみ許し、狭い領域を優先とする<br>属性のキーワードは継続検討           |

| 17  | N-Format | 各端子がどの電源系に属しているかの記述                                                                                                                                            | ⇒ 採用 オブションとして指定可能にする<br>電源系は /* PG_NET=「domain」*/ で指示「domain」はユーザ指定<br>信号系に /* pow=「domain」 gnd=「domain」*/ で電源系を指定<br>pow、gndなどのキーワードは継続検討 |

| 18  | M-Format | 設計バージョンの履歴管理をフォーマット記述がサポート<br>するか                                                                                                                              | ⇒ <mark>採用</mark> セットを複数許可する、履歴を示す番号を追加<br>キーワードは継続検討                                                                                      |

## 2.3.3.3 LPB-EMC-Nano 共同 LEN プロジェクト

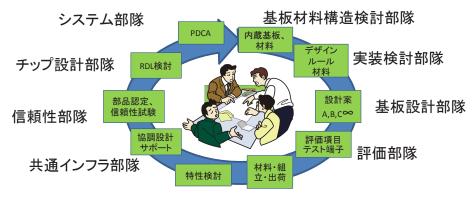

LPB 標準フォーマットをより実設計に使えるような工夫・発展を継続的に行うため、今年度は、他規格との連携・リエゾン活動、意見交換の場として「LPB-EMC-Nano 共同 LEN プロジェクト」を開催した。図 2.3.3.3-1 に本プロジェクトの参加 WG/SC の構成を示す。

本年度は表 2.3.3-5 のとおり第1回~第6回の計6回開催した。

# **JEITA**

# 半導体部会

## EDA技術専門委員会

半導体製品技術 標準化専門委員会

ナノ世代物理設計WG

LPB相互設計WG

集積回路製品技術 小委員会

半導体EMC-SC

図 2.3.3-1 LEN プロジェクト構成 WG/SC

表 2.3.3-5 本年度に開催した LEN プロジェクト

|     | 開催日時       | 会場       | 概要(LPB 関連)                        |

|-----|------------|----------|-----------------------------------|

| 第1回 | 2014/6/18  | 富士通      | 参加者:13名                           |

|     |            | 新横浜中央ビル  | 各 WG/SC の活動紹介。今後の進め方を議論した。        |

| 第2回 | 2014/7/30  | 富士通      | 参加者:15名                           |

|     |            | 新横浜中央ビル  | 活動の目標と成果を議論。ICEMについて紹介いた          |

|     |            |          | だいた。                              |

| 第3回 | 2014/9/10  | 富士通      | 参加者:12名                           |

|     |            | 新横浜中央ビル  | 半導体EMC-SCのモチーフをLPBフォーマットで解        |

|     |            |          | 析した場合について検討した。                    |

| 第4回 | 2014/10/30 | 富士通      | 参加者:15名                           |

|     |            | 野村不動産新横浜 | ICEM 対応の LPB フォーマット(C-Format)を提案。 |

|     |            | ビル       | 内容について議論した。                       |

| 第5回 | 2014/12/19 | 富士通      | 参加者:13名                           |

|     |            | 新横浜中央ビル  | ICEM 対応についての修正案を提案。内容を議論、         |

|     |            |          | 確認した。                             |

| 第6回 | 2015/2/10  | 日本ケイデンス  | 参加者:16名                           |

|     |            | 新横浜中央ビル  | 活動のまとめについて議論。                     |

この活動を通じ、下記2点について検討、成果としてまとめた。

• LPB 標準フォーマットの IEEE P2401 での標準化で ICEM 記述を対応 ICEM 記述に対応するため、ICEM 記述の標準化の状況や、その内容について議論、対応 案の作成、精査を行い、標準化提案バージョンへ反映することが出来た。

• LPB 標準フォーマットの適用検証

LPB 標準フォーマットを設計に適用した場合、効率化されるかの検証のため、半導体 EMC-SC が行っている MP 法のシミュレーションをモチーフに、LPB フォーマットを用いて解析を実施した。また、その結果については、3 月 19 日に開催した LPB フォーラムで報告を行った。

#### 2.3.3.4 参加メンバー

サブワーキンググループのメンバーは下記表 2.3.3-1 の通り。

2014 年度はこのメンバーで、サブワーキンググループを計 8 回開催した。(内、6 回は LEN プロジェクトと並行開催)

表 2.3.3-1 LPB 相互設計標準化戦略ワーキンググループメンバー (2014 年度)

| リーダー | 永野 民雄 | ルネサスエレクトロニクス株式会社       |

|------|-------|------------------------|

| メンバー | 松村 宗明 | 富士通セミコンダクター株式会社        |

| 同    | 青木 孝哲 | 株式会社東芝                 |

| 同    | 村田 和希 | 株式会社リコー                |

| 同    | 冨島 敦史 | 株式会社東芝                 |

| 同    | 林 靖二  | キヤノン株式会社               |

| 同    | 川畑 航  | ソニーLSI デザイン株式会社        |

| 同    | 大塚 育生 | 富士通アドバンストテクノロジ株式会社     |

| 同    | 益子 行雄 | 日本ケイデンス・デザイン・システムズ社 ※1 |

| 同    | 人見 忠明 | 日本ケイデンス・デザイン・システムズ社 ※1 |

| 同    | 松澤 浩彦 | 株式会社図研                 |

<sup>※1</sup> 期の途中で益子から人見に交代した。

#### 2.3.4 LPB相互設計導入WG

#### 2.3.4.1目的

JEITA LPB 標準フォーマットを実際の設計現場で使用することで、フォーマットの成熟を図り現場レベルでの課題を明確にする。また各社のフォーマット使用開始を公開することで、業界全体のフォーマット流通性を図る。

#### 2.3.4.2 活動内容

#### 2.3.4.2.1 活動概要

昨年度まではWG内でフォーマットを使った事例を作ることでLPB相互設計の検証および普及活動を展開してきた。本年度は各社がフォーマットを使った設計を開始し、その進捗度合いおよび以下の課題を共有する活動を行った。

- ・フォーマットに課題があればフォーマット修正案の作成

- ・EDA ツールに課題があれば EDA ベンダーと折衝

上記課題を含め、各社がフォーマット使用を開始したことを2015年3月19日開催の第6回LPBフォーラムで公開した。

#### 具体的な活動内容

- 1. 各社、設計現場でのフォーマット使用開始の推進

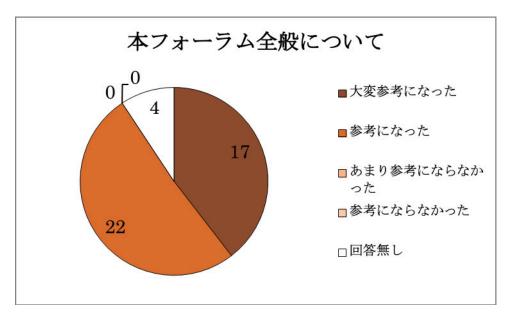

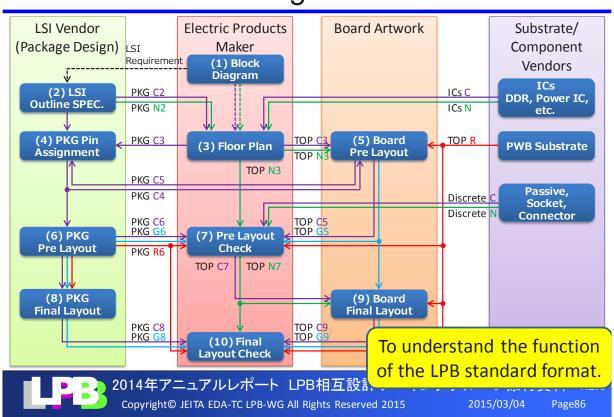

- 2. 第5回 LPB フォーラム準備、開催