# LSI-Package-Board

講演テーマ: LPB相互設計セミナー

『実践!これでいける! LSI・パッケージ・ボードの相互設計実例 ~LPB標準フォーマットの活用方法とその効果~』

日時:平成23年11月17日(木) 15:30-17:00

場所:パシフィコ横浜

展示ホール「EDSFair2011Nov.」アネックスホールF201

# 1部

LSI-パッケージ - ボードの相互設計の為の標準フォーマットとその活用方法実施例

# アジェンダ

- ■背景

- 適用事例の説明

- 従来方式

- LPB**方式**

- 総括

# アジェンダ

- ■背景

- 適用事例の説明

- 従来方式

- LPB方式

- 総括

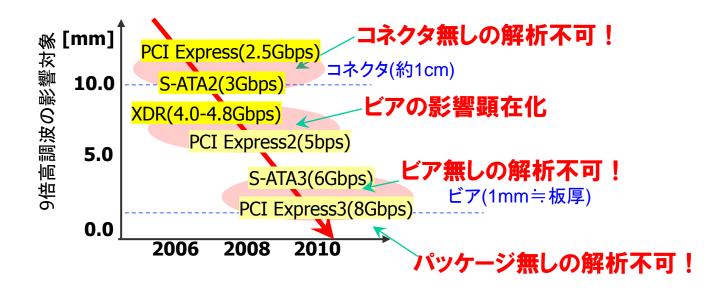

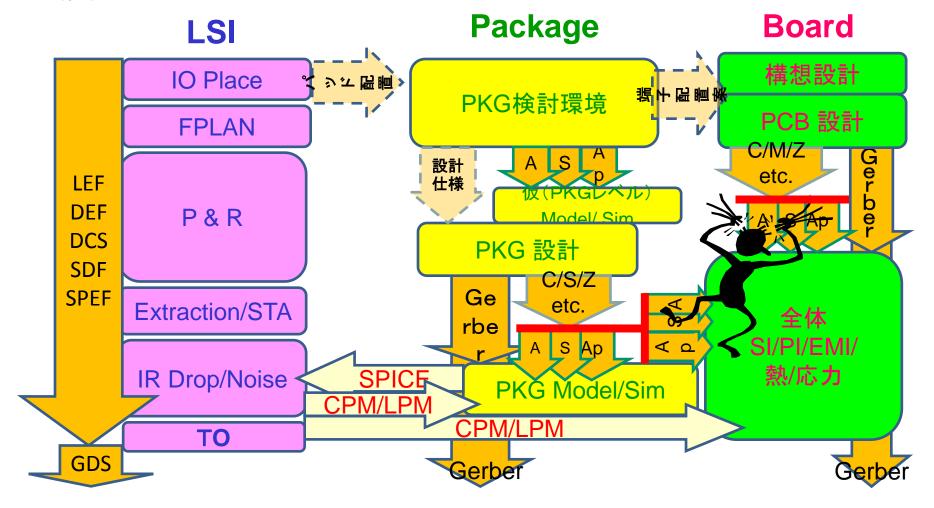

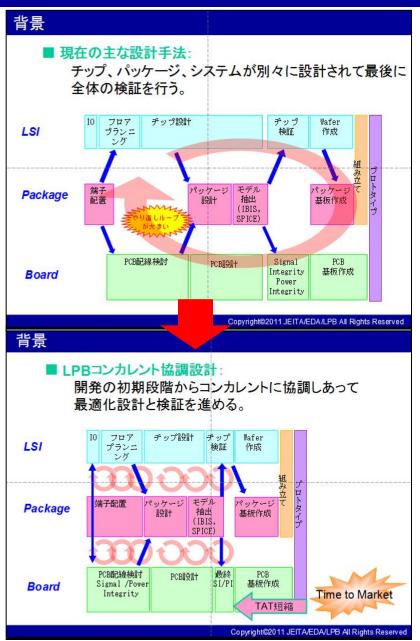

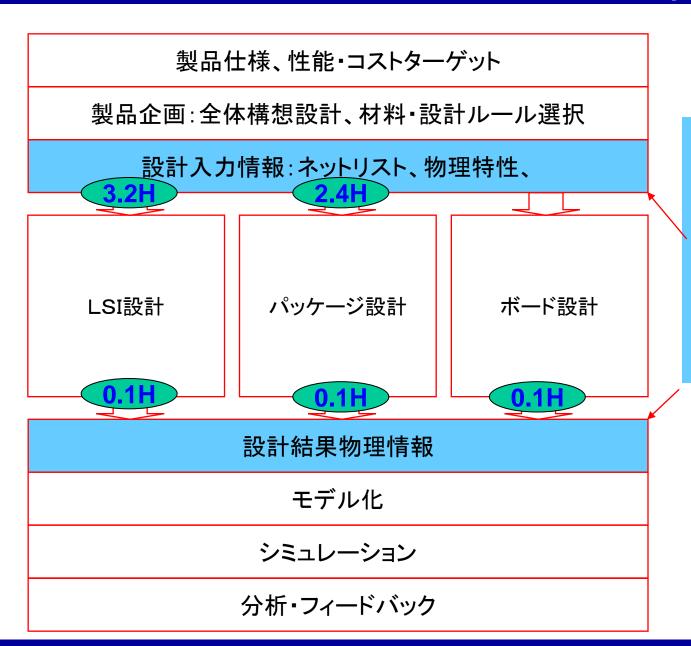

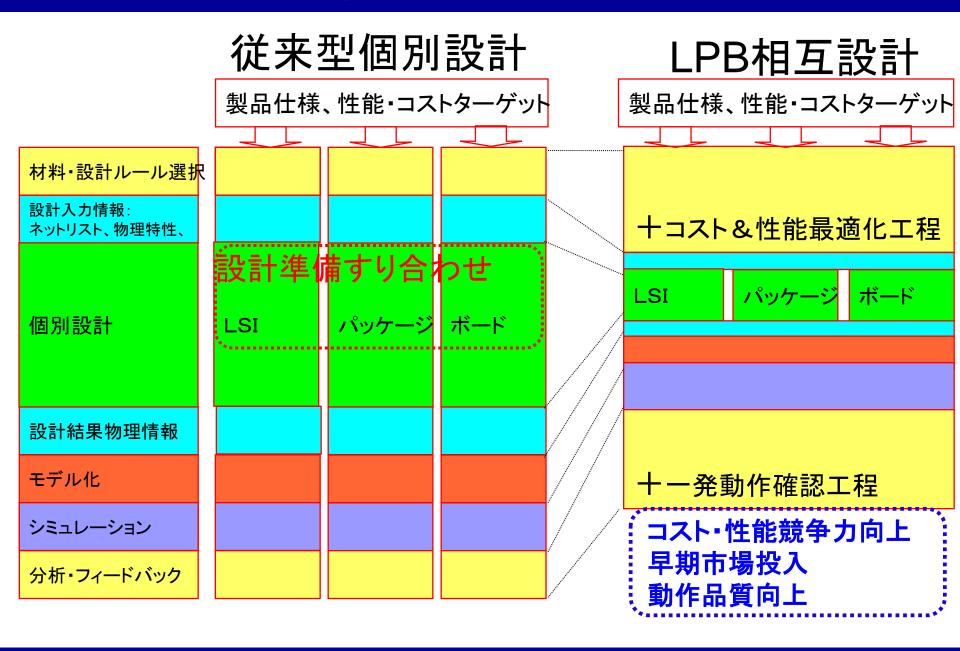

回路の高速化に伴い、設計マージンが厳しくなっている。

LSI、Package、Board全てを考慮した設計が必要となってきている。

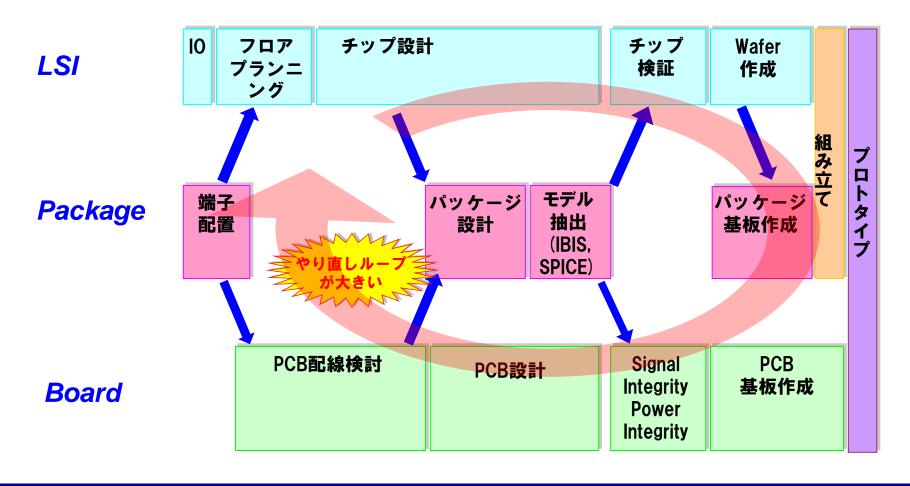

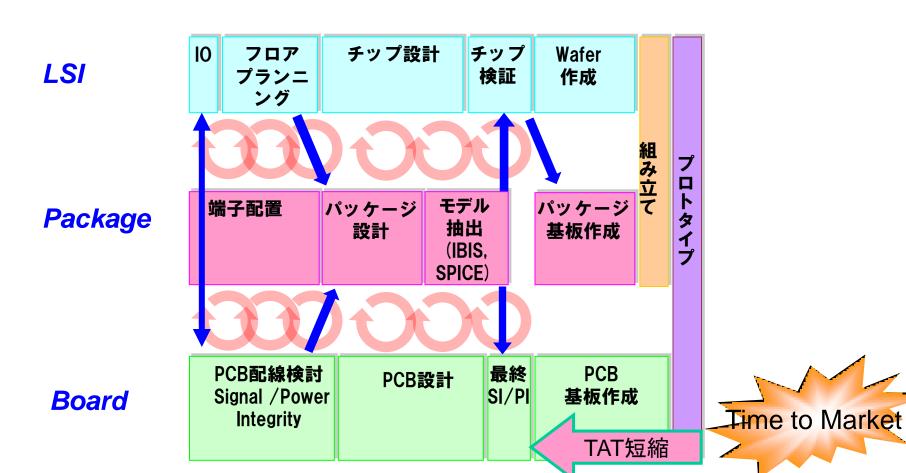

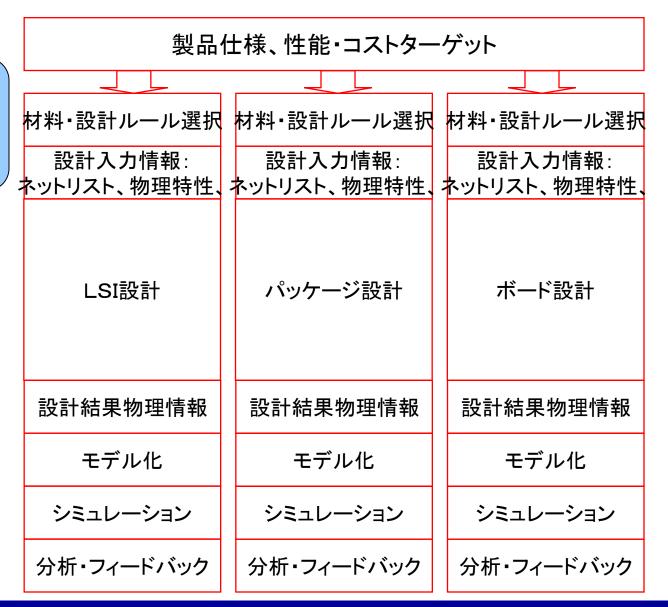

#### ■ 現在の主な設計手法:

LSI、Package、Boardが別々に設計されて最後に 全体の検証を行う。

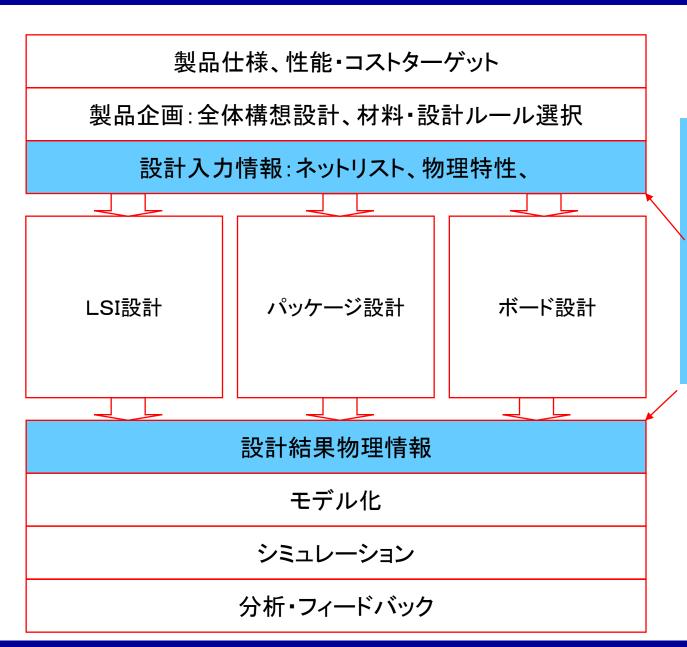

#### ■ LPBコンカレント協調設計:

開発の初期段階からコンカレントに協調しあって最適化設計と検証を進める。

#### 2010年4月より、JEITA LPB相互設計WGが開始

#### LSI - Package - Board Concurrent Co-Design

## 背景 ~課題~

- ✓LSI・パッケージ・ボード各設計の文化の違いによる意思伝達ミス

- ✓必要とする情報の欠落

- ✓情報そのものの流通性の悪さ

## 背景 ~ 従来型個別設計~

# 従来

紙に書いた 仕様書

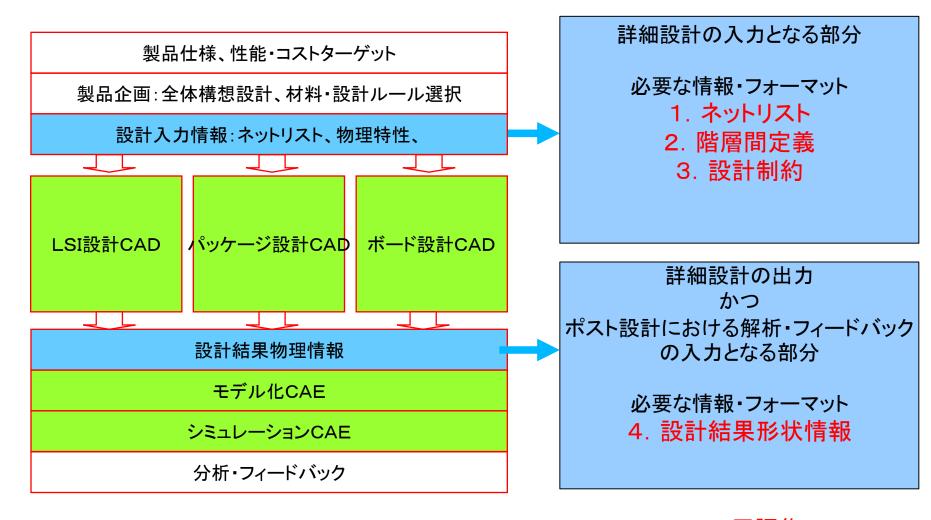

# 背景 ~標準フォーマット化すべき部分~

標化るき分準すべ部分

# 背景 ~標準フォーマット化部分の提案~

5. 用語集

LSI パッケージ パッケージ LSI ボード <SwappablePin> <Group name="DQ BYTE1" part="CHIPA PKG"> <Pin name="AC10"/> <Pin name="AB9"/> </Group> </SwappablePin> <FixedPin> <Pin part="CHIPA\_PKG" name="A1"/> <Pin part="CHIPA\_PKG" name="A2"/> </FixedPin> ネットリスト(論理定義) <DifferentialPairConstraint> <DiffPair name="DQS0" LengthTolerance="0.500" > 階層間定義(物理定義) <Pin part="CHIPA PKG" name="AC8" /> <Pin part="CHIPA\_PKG" name="AC7" /> </DiffPair> </DifferentialPairConstraint>

# アジェンダ

- 背景

- 適用事例の説明

- 従来方式

- LPB方式

- 総括

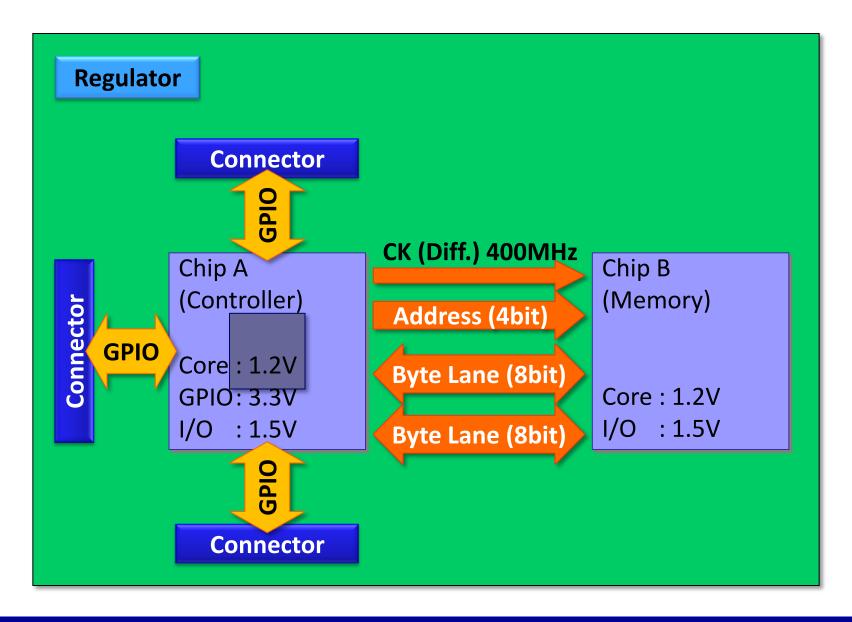

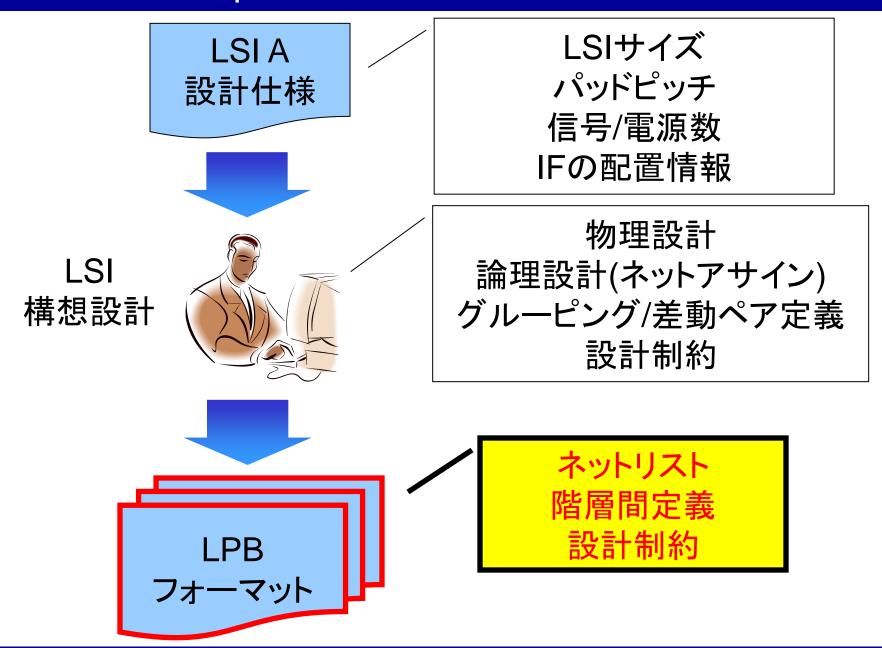

# 適用事例の説明 ~モチーフ~

#### 適用事例の説明 ~モチーフ~

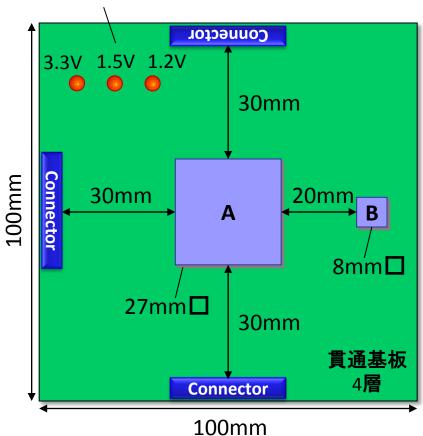

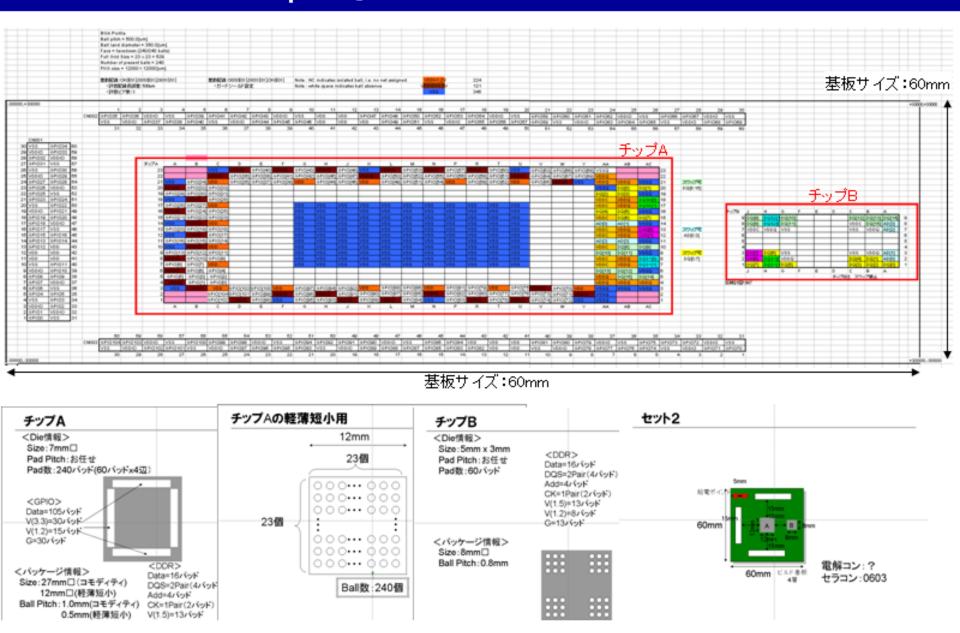

# セット1 (コモディティ)

#### 給電ポイント

4層貫通基板、LSIA:WB

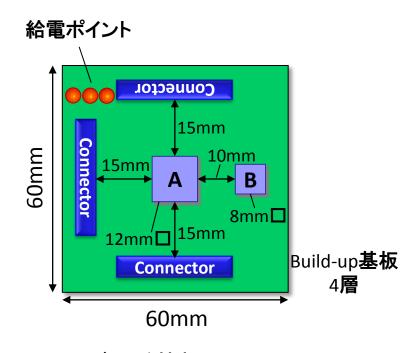

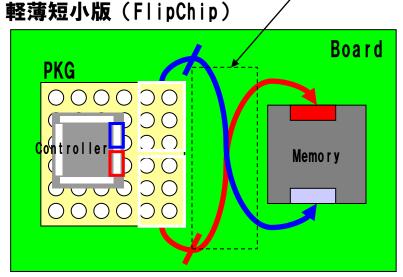

# セット2 (軽薄短小)

4層ビルド基板、LSIA:FC

# 適用事例の説明 ~役割分担~

| ■従来方式                 | Cont     | roller   | Board |          | nory     |

|-----------------------|----------|----------|-------|----------|----------|

|                       | LSI      | Package  | Doalu | Package  | LSI      |

| コモディティ<br>(100×100mm) | Ā≡       | <u>A</u> | キヤノン  | <u>A</u> | <u>A</u> |

| 軽薄短小<br>(60×60mm)     | <u>A</u> | <u>A</u> | キヤノン  |          |          |

| <u> ニ</u> ヽ ハ / |  |

|-----------------|--|

| 「ナンノー           |  |

検証

| ■LPB方式                | Cont       | roller        | Poord       | Memory  |     |

|-----------------------|------------|---------------|-------------|---------|-----|

|                       | LSI        | Package Board |             | Package | LSI |

| コモディティ<br>(100×100mm) | -          | リコー           | Panasonic   | - 図研    | 東芝  |

| 軽薄短小<br>(60×60mm)     | ) <u> </u> | 富士通セミコンダクター   | トッパン<br>NEC |         |     |

# アジェンダ

- 背景

- 適用事例の説明

- 従来方式

- LPB方式

- 総括

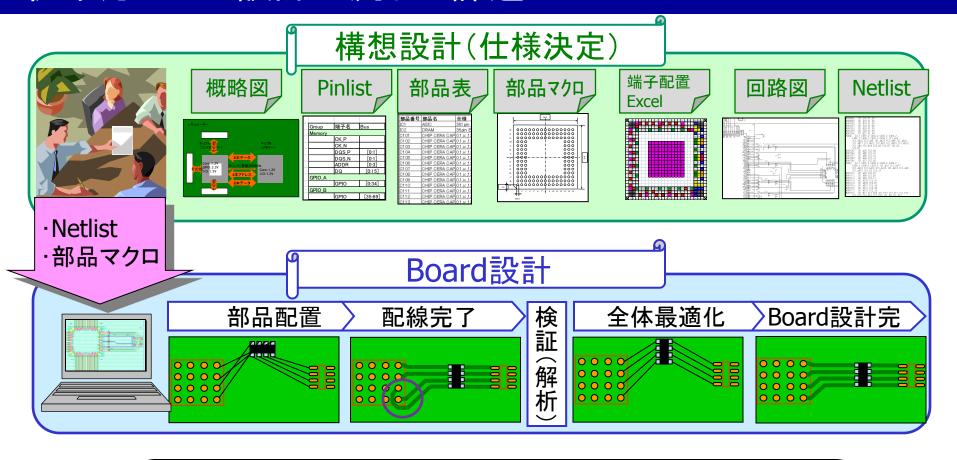

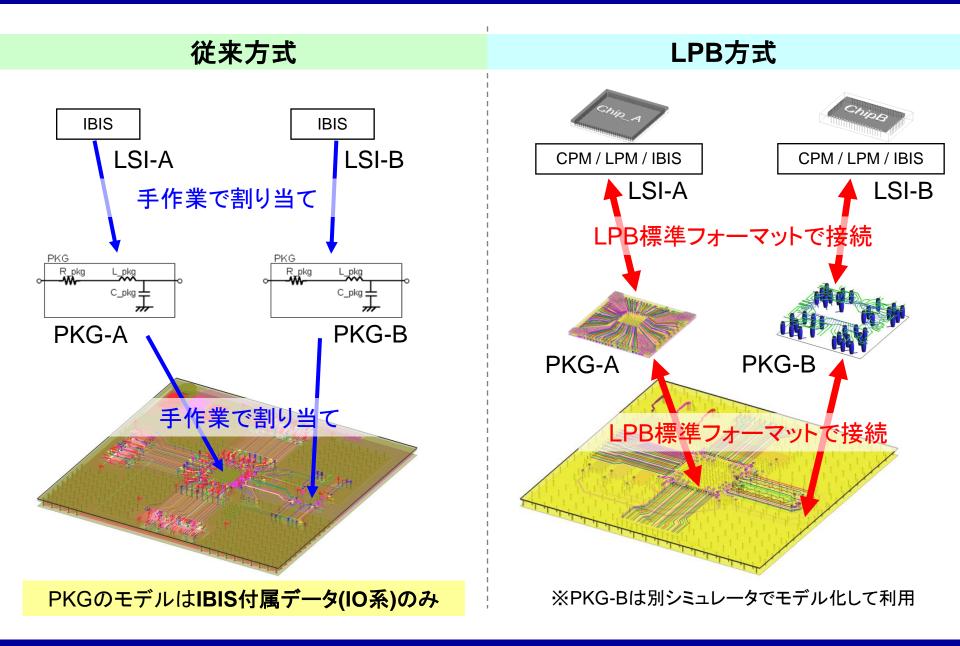

#### 従来方式

■従来方式によるBoard設計(2種類)を担当

|                       | Controller |          | Board | Memory   |          |

|-----------------------|------------|----------|-------|----------|----------|

|                       | LSI        | Package  | Boalu | Package  | LSI      |

| コモディティ<br>(100×100mm) | A          | <u>A</u> | キヤノン  | <u>A</u> | <u>A</u> |

| 軽薄短小<br>(60×60mm)     | <u>A</u>   | <u>A</u> | キヤノン  |          |          |

<u> 従来方式 (今回の適用事例での想定)</u>

- ①LSI,PKG,Board個別設計

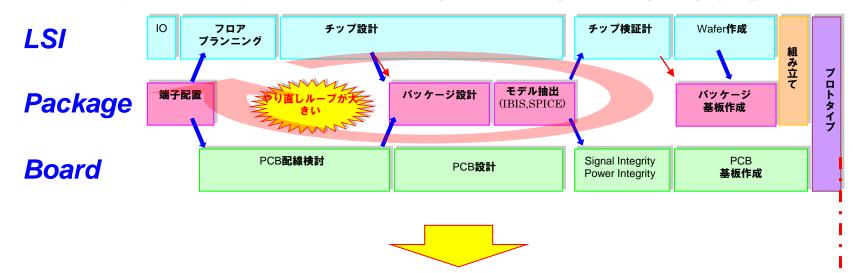

- ②LSI,PKG ⇔ Board 設計情報のやり取りは『紙》

- ③SIのみLSI+PKG+Boardの統合解析実施(※IBIS modelを使用)

※『紙』: CADが直接読み取れないフォーマットの意

#### 従来方式 ~設計の流れと課題~

#### 従来方式の課題

- 1.人為的ミスの発生リスクがある(構想設計時)

- 2.全体最適化が困難

- 3.解析準備に時間がかかる

## 従来方式 ~課題1.人為的ミスの発生リスク~

■多岐にわたるフォーマット間の情報伝達・管理を人が行っている

| フォーマット | 概略図    | ピンリスト                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 部品表  | 部品マクロ    | 端子配置<br>Excel                                                                       | 回路図        | Netlist |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------------------------------------------------------------------------------------|------------|---------|

| 情報     | Man-be | Group   MF-6   Bus   Memory   CK P   CK P   CK N   DoS P   Do1   DoS N   Do1   DoS N   Do1   DoS N   Do1   DoS N   Do1   Do5 N   Do5 N |      |          | A B C D E 23 12 3 3 3 3 3 4000 9704 22 12 13 12 12 12 12 12 12 12 12 12 12 12 12 12 |            |         |

| 信号名    | Δ      | <b>~</b> O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |          |                                                                                     | 0          |         |

| 部品名    | Δ ,    | <b>O</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0    | <b>O</b> | <b>O</b>                                                                            | <b>→</b> △ |         |

| 部品番号   | /<br>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0/   |          |                                                                                     | 0          | 0       |

| 部品外形   | 定義付    | [ <del>†</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 情報伝達 | 0        | Δ                                                                                   |            |         |

| 端子名    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 7        | 0                                                                                   | 0          |         |

| 端子番号   |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 0        | 0                                                                                   | 0          | 0       |

| ネット名   |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |          |                                                                                     |            | (O)     |

フォーマットが集約されれば、 人為的ミスの発生リスクが低減される

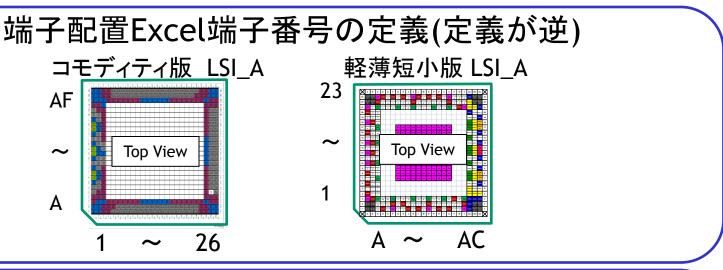

#### 従来方式 ~課題1. 人為的ミスの発生リスク 事例~

#### 関連: Top View / Bottom Viewの定義があいまい

『あいまいさ』が人為的ミスの原因になっている

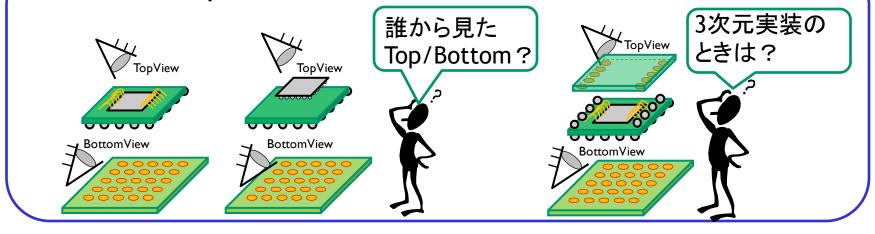

# 従来方式 ~課題2.全体最適化が困難~

■L,P,Bの各設計マージン・制約が不明確で、最適解が見出せない

円滑な議論、相互理解が、L,P,B全体最適を容易化する

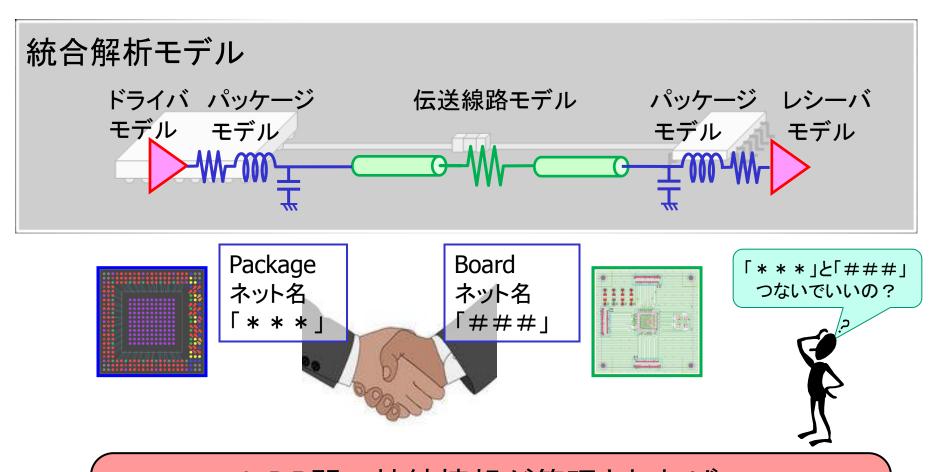

#### 従来方式 ~課題3. 解析準備に時間がかかる~

■L,P,B毎に異なる端子名、ネット名がつけられる為、 確認しながらの統合解析モデル作成には時間がかかる

L,P,B間の接続情報が管理されれば、 統合解析モデルの作成時間が短縮される

#### 従来方式 ~課題3.解析準備に時間がかかる 事例~

解析担当者はCADデータを見て、接続を確認しながら、 統合解析モデルを作成するため、時間がかかる

#### 従来方式 ~まとめ~

■従来方式によって、

コモディティ版、軽薄短小版の2つのBoard設計を行いました

■従来方式による設計における3つの課題を示しました

課題1 人為的ミスの発生リスクがある

課題2 全体最適が困難

課題3 解析準備に時間がかかる

# アジェンダ

- 背景

- 適用事例の説明

- 従来方式

- LPB**方式**

- 総括

# 適用事例の説明 ~役割分担~

| ■従来方式                 | Controller |             | Board       | Memory   |     | 検証         |

|-----------------------|------------|-------------|-------------|----------|-----|------------|

|                       | LSI        | Package     | Doalu       | Package  | LSI |            |

| コモディティ<br>(100×100mm) | <u>A</u>   | <u>A</u>    | キヤノン        | <u>A</u> | A   |            |

| 軽薄短小<br>(60×60mm)     |            | <u>A</u>    | キヤノン        |          |     |            |

|                       |            |             |             |          | -   | <br>  デンソー |

| ■LPB方式                | Controller |             | Doord       | Memory   |     |            |

|                       | LSI        | Package     | Board       | Package  | LSI |            |

| コモディティ<br>(100×100mm) |            | リコー         | Panasonic   |          |     |            |

| 軽薄短小<br>(60×60mm)     | ソニー        | 富士通セミコンダクター | トッパン<br>NEC | · 凶研     | 東芝  |            |

## LPB方式 ~Step~

```

Step1. LSI担当が階層間定義、設計制約を仮決め

(担当:ソニー 濱田)

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

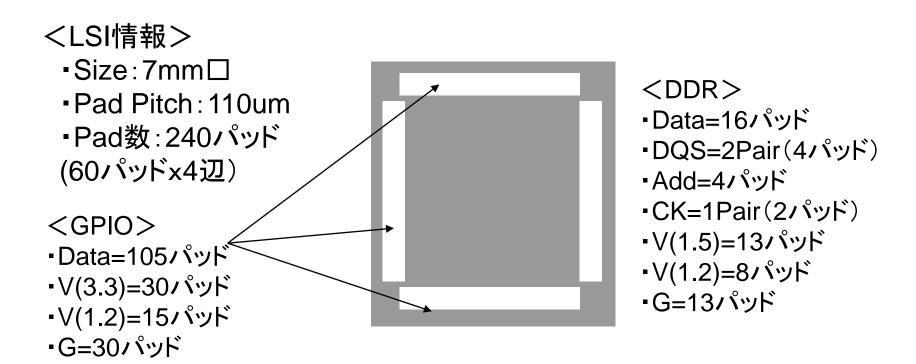

# LPB方式 ~Step1~

Step1. LSI担当が階層間定義、設計制約を仮決め (担当:ソニー 濱田)

```

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

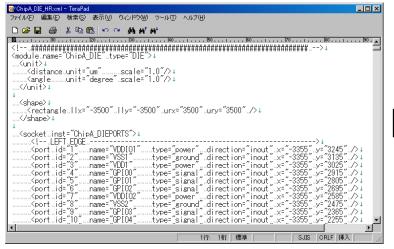

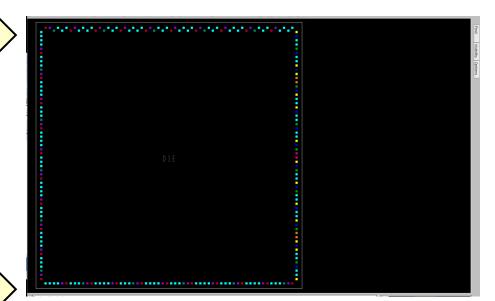

# LPB方式 ~Step1-①~

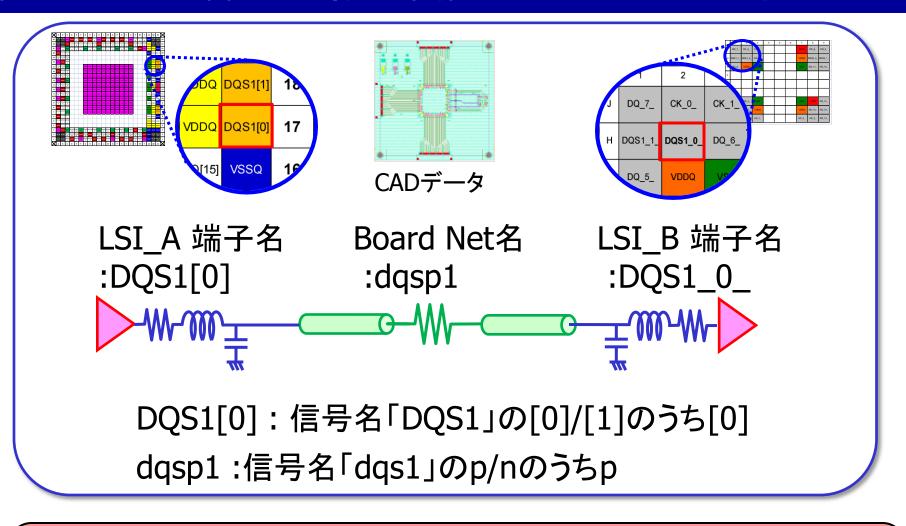

# LPB方式 ~Step1-2.LSI Aの設計仕様~

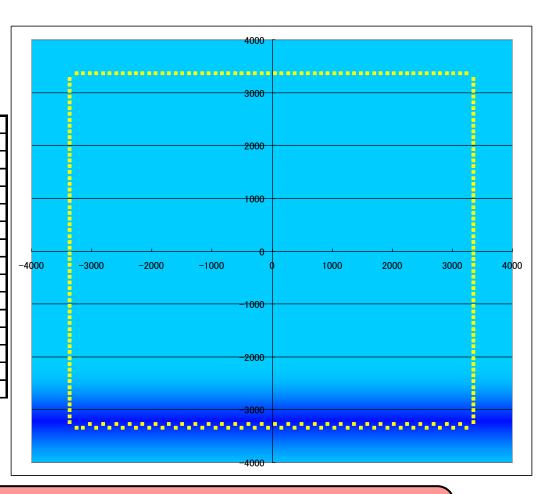

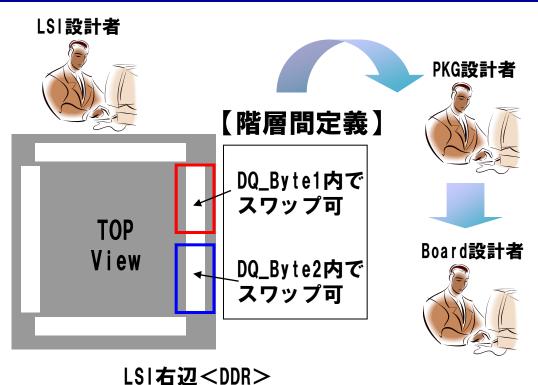

## LPB方式 ~Step1-③. LSI構想設計~

### 【階層間定義】

#### ■ 物理設計/論理設計

| Pad番号 | Pad名   | Pad属性  | I/O   | X座標   | Y座標  |  |  |

|-------|--------|--------|-------|-------|------|--|--|

| 1     | VDDIO1 | Power  | inout | -3355 | 3245 |  |  |

| 2     | VSS1   | GND    | inout | -3355 | 3135 |  |  |

| 3     | VDD1   | Power  | inout | -3355 | 3025 |  |  |

| 4     | GPI00  | Signal | inout | -3355 | 2915 |  |  |

| 5     | GPIO1  | Signal | inout | -3355 | 2805 |  |  |

| 6     | GPIO2  | Signal | inout | -3355 | 2695 |  |  |

| 7     | VDDIO2 | Power  | inout | -3355 | 2585 |  |  |

| 8     | VSS2   | GND    | inout | -3355 | 2475 |  |  |

| 9     | GPIO3  | Signal | inout | -3355 | 2365 |  |  |

| 10    | GPIO4  | Signal | inout | -3355 | 2255 |  |  |

| 11    | GPIO5  | Signal | inout | -3355 | 2145 |  |  |

| 12    | GPIO6  | Signal | inout | -3355 | 2035 |  |  |

| 13    |        |        | inout | -3355 | 1925 |  |  |

| 14    | VSS3   | GND    | inout | -3355 | 1815 |  |  |

| 15    | VDD2   | Power  | inout | -3355 | 1705 |  |  |

LPB方式: 従来方式と大差なし。

従来方式: LPB方式と大差なし。

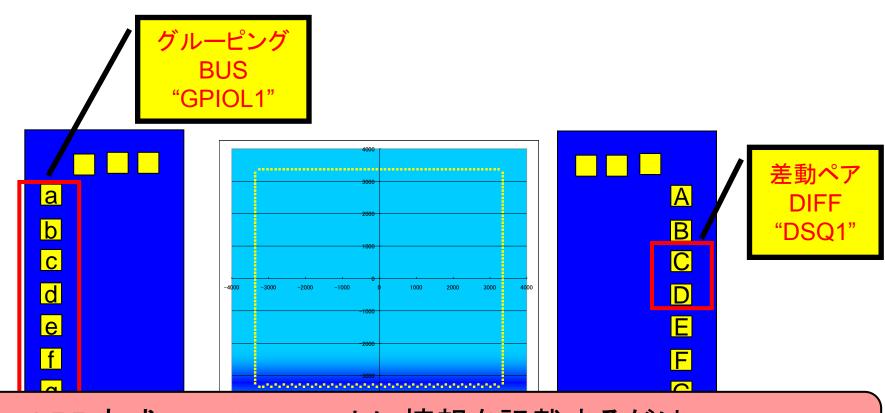

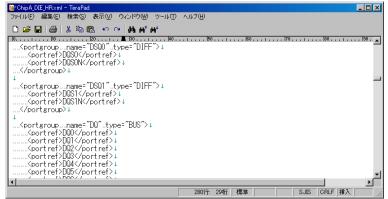

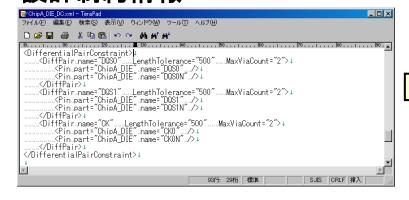

### LPB方式 ~Step1-4. LSI構想設計~

#### 【階層間定義】

■ グルーピング/差動ペアの定義

LPB方式: フォーマットに情報を記載するだけ。

従来方式: 資料作成や打合せによる認識合わせが必要。

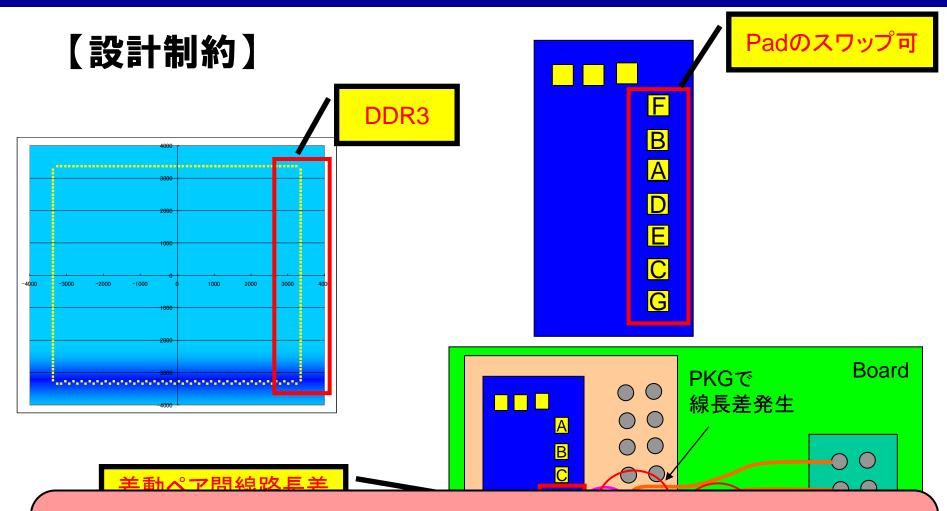

### LPB方式 ~Step1-⑤. LSI構想設計~

LPB方式: フォーマットに情報を記載するだけ。

定義の『あいまいさ』を排除

従来方式: 資料作成や打合せによる認識合わせが必要。

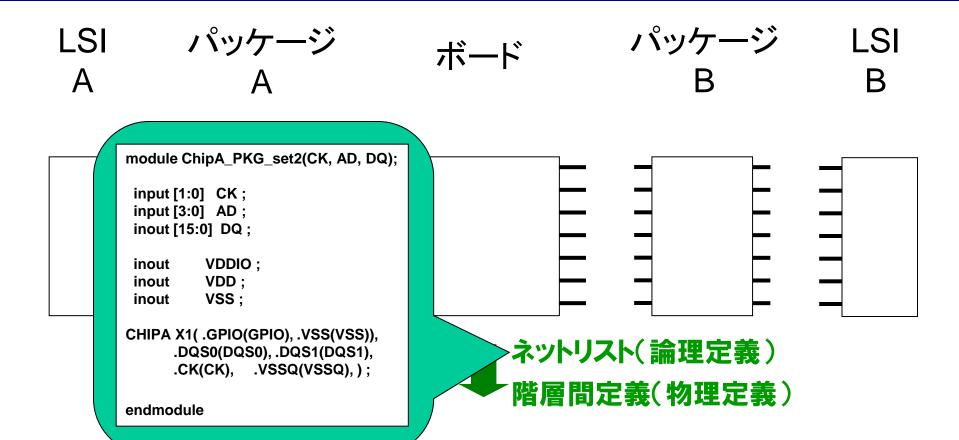

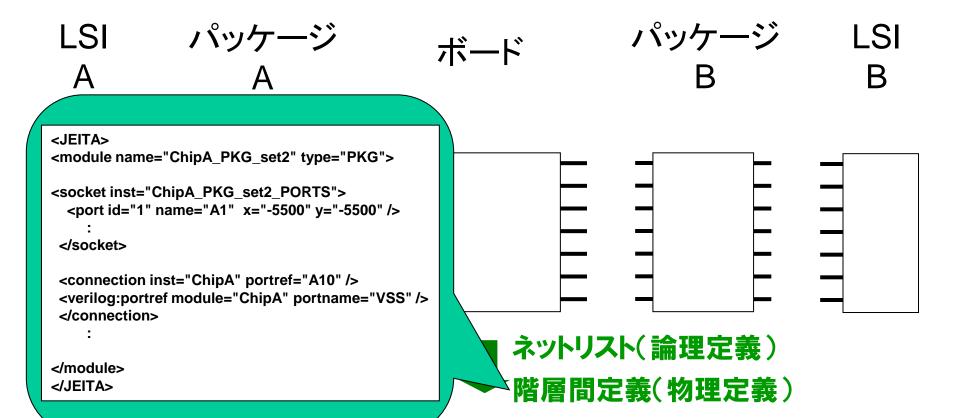

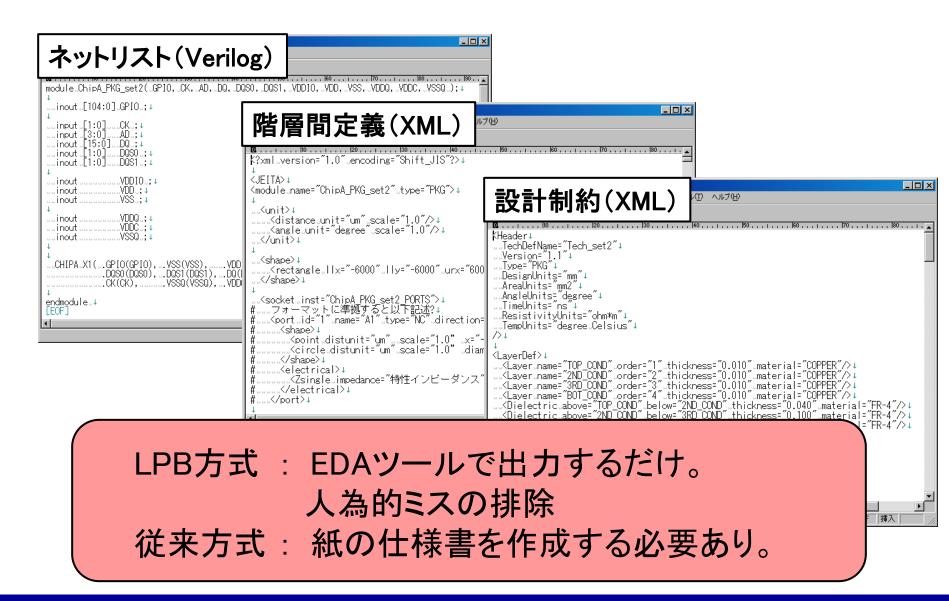

#### LPB方式 ~Step1-6. LPB標準フォーマットへの出力~

## LPB方式 ~Step1. まとめ~

LPB方式作成工数 (EDAツールが対応した場合)

| 工程         | 作業内容                                                   | LPB方式 <sup>※)</sup><br>[hours] |  |

|------------|--------------------------------------------------------|--------------------------------|--|

| 3          | 物理設計/論理設計                                              | 3                              |  |

| 4          | グルーピング/差動ペアを<br>設定                                     | 0.1                            |  |

| <b>(5)</b> | 設計制約を設定                                                | 0.1                            |  |

| 6          | LPB標準フォーマットへの<br>出力<br>・ネットリスト<br>・階層条件XML<br>・設計制約XML | 0.1                            |  |

|            | 合計                                                     | 3.3                            |  |

| _          | 様書作成の工数削減<br>料作成や打合せによる                                | る認識合わる                         |  |

|            | 不要となる事に。                                               | はる効果                           |  |

#### LPB方式 ~Step2~

```

Step 1. LSI担当が階層間定義、設計制約を仮決め

(担当:ソニー 濱田)

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

#### LPB方式 ~Step2-①. LSI作成~

#### 階層間定義情報

#### PKG設計ツール上にLSIを作成

#### 設計制約情報

LPB方式: EDAツールで読み込むだけ

従来方式: 紙の仕様書を解読する必要あり

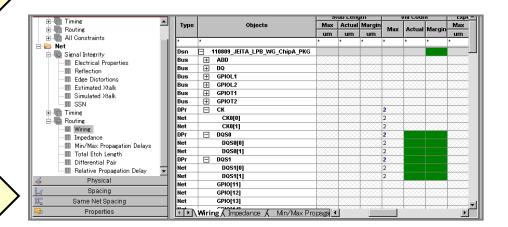

## LPB方式 ~ Step2-②. 設計制約を設定~

#### 階層間定義情報

#### 設計制約情報

#### PKG設計ツールに設計制約を設定

LPB方式: EDAツールで読み込むだけ

従来方式: 紙の仕様書を解読する必要あり

## LPB方式 ~Step2-③. PKG設計ルールを設定~

#### PKG設計ツールに設計ルールを設定

|    | Subclass Name  | Туре       |        | Material       |      | Thickness<br>(UM) | Conductivity<br>(mho/cm) | Dielectric<br>Constant | Loss<br>Tangent | Negative<br>Artwork | Shield |

|----|----------------|------------|--------|----------------|------|-------------------|--------------------------|------------------------|-----------------|---------------------|--------|

| 1  |                | SURFACE    | $\neg$ | AIR            | AIR  |                   |                          |                        | 0               |                     |        |

| 2  | TOP_SR         | DIELECTRIC | T      | RESISTOR_INK   | Ŧ    | 20                | 0                        | 4.5                    | 0.035           |                     |        |

| 3  | TOP_COND       | CONDUCTOR  | ▾      | COPPER         | Ŧ    | 10                | 595900                   | 4.5                    | 0               |                     |        |

| 4  | DIELECTRIC_1_2 | DIELECTRIC | ▣      | FR-4           | •    | 40                | 0                        | 4.5                    | 0.035           |                     |        |

| 5  | 2ND_COND       | PLANE      | •      | COPPER         | •    | 10                | 595900                   | 4.5                    | 0               |                     | ×      |

| 6  | CORE           | DIELECTRIC | P      | FR-4           | •    | 100               | 0                        | 4.5                    | 0.035           |                     |        |

| 7  | 3RD_COND       | PLANE      | •      | COPPER         | •    | 10                | 595900                   | 4.5                    | 0               |                     | ×      |

| 8  | DIELECTRIC_3_4 | DIELECTRIC | ◛      | FR-4           | FR-4 |                   | 0                        | 4.5                    | 0.035           |                     |        |

| 9  | BOT_COND       | CONDUCTOR  | •      | COPPER 💌       |      | 10                | 595900                   | 4.5                    | 0               |                     |        |

| 10 | BOT_SR         | DIELECTRIC |        | RESISTOR_INK 💌 |      | 20                | 0                        | 4.5                    | 0.035           |                     |        |

| 11 |                | SURFACE    |        | AIR            |      |                   |                          | 1                      | 0               |                     |        |

|    |                |            |        |                |      |                   |                          |                        |                 |                     |        |

LPB方式

EDAツールの制限を受けない(容易に変更可)

従来方式: 容易にEDAツールを変更できない

### LPB方式 ~ Step2-4. ボールアサインを設定~

LPB方式 : 従来方式と差なし

従来方式: LPB方式と差なし

### LPB方式 ~Step2-⑤. 仮決めしたPKG情報の出力~

LPB方式 : JEITA LPB標準フォーマットで出力して提供

従来方式: 紙の仕様書を作成して提供(人為的ミスの可能性)

## LPB方式 ~Step2. まとめ~

#### LPB方式作業工数(EDAツールが対応した場合)

| 工程 | 作業内容                                   | LPB方式 [hours] |

|----|----------------------------------------|---------------|

| 1  | LSI作成                                  | 0.1           |

| 2  | 設計制約を設定                                | 0.1           |

| 3  | PKG設計ルールを設定                            | 0.1           |

| 4  | ボールアサインを設定                             | 2.0           |

| 5  | 仮決めしたPKG情報の出力 ・ネットリスト ・階層間定義情報 ・設計制約情報 | 0.1           |

|    | 合計                                     | 2.4           |

#### LPB方式 ~Step3~

```

Step 1. LSI担当が階層間定義、設計制約を仮決め

(担当:ソニー 濱田)

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

## LPB方式 ~Step3-①. PCB仕様の概要~

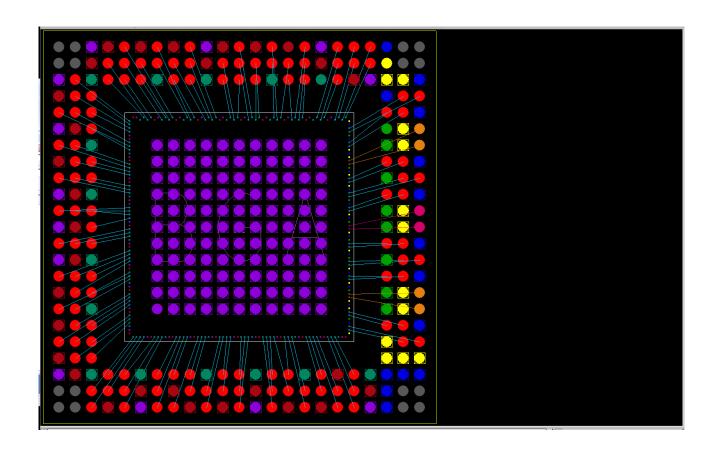

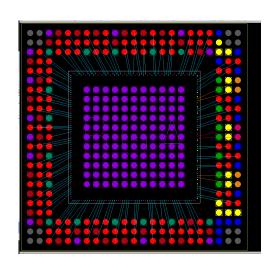

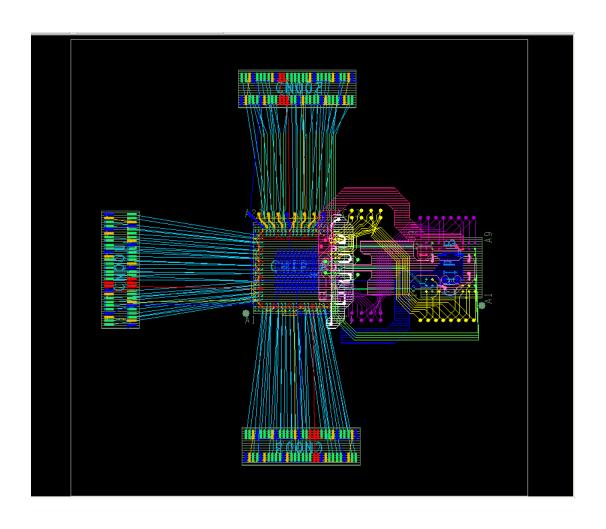

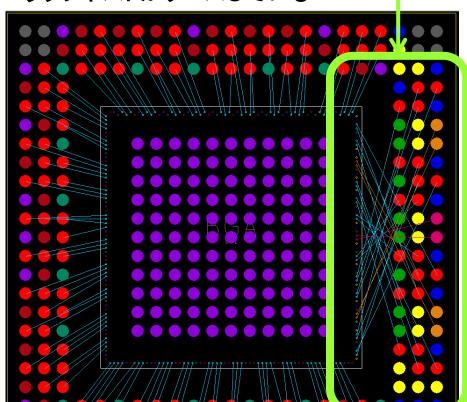

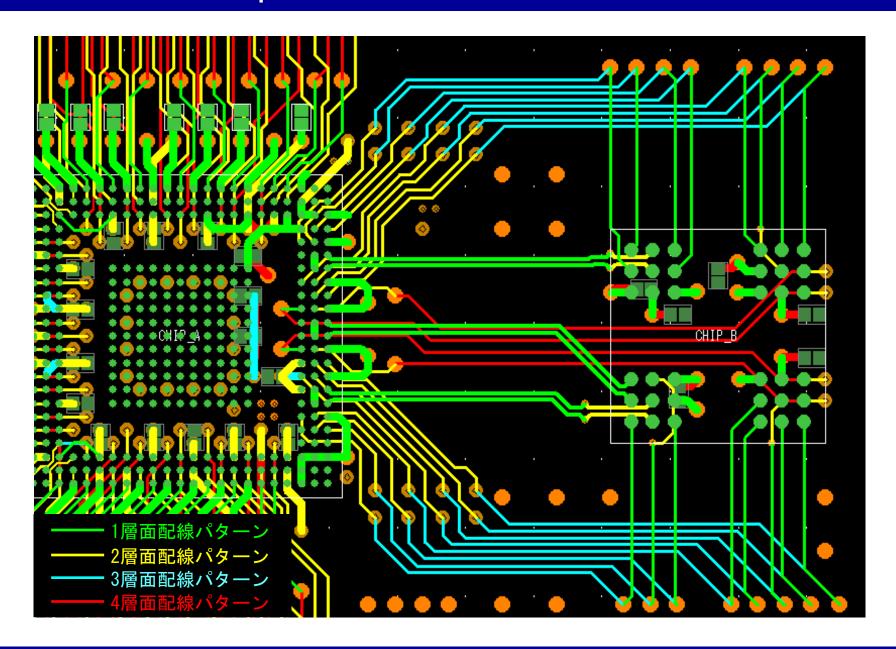

## LPB方式 ~Step3-②. CADによる配置・配線検討~

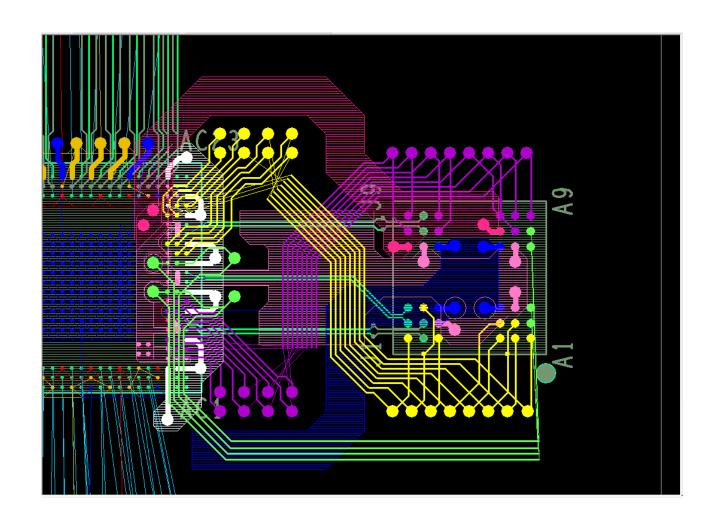

# LPB方式 ~ Step3-③. CADによる配置・配線検討~

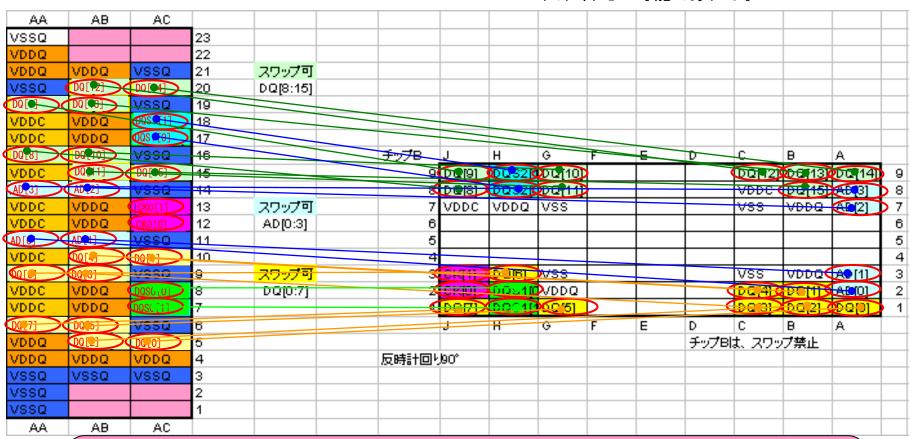

## LPB方式 ~Step3-4. PKG\_Aピン配置の検討~

<メモリ配線部拡大:現状のピン配置>

| 0.0    | 0.0            | 0.0           |    |          |       |               |        |               |             |   |       |        |        |                   |     |

|--------|----------------|---------------|----|----------|-------|---------------|--------|---------------|-------------|---|-------|--------|--------|-------------------|-----|

| AA     | AB             | AC            |    |          |       |               |        |               |             |   |       |        |        |                   | -   |

| VSSQ   |                |               | 23 |          |       |               |        |               |             |   |       |        |        |                   | -   |

| VDDQ   |                |               | 22 |          |       |               |        |               |             |   |       |        |        |                   | _   |

| VDDQ   | VDDQ           | VSSQ          | 21 | スワップ可    |       |               |        |               |             |   |       |        |        |                   |     |

| VSSQ   | <b>D</b> \$191 | DOM           | 20 | DQ[8:15] |       |               |        |               |             |   |       |        |        |                   |     |

|        | [DQ,3]         | VSSQ          | 19 |          |       |               |        |               |             |   |       |        |        |                   |     |

| VDDC   | Appa           | <b>CELLID</b> |    |          |       |               |        |               |             |   |       |        |        |                   |     |

| VDDC   | VDDQ           | OEF-SHID      | 47 |          |       |               |        |               |             |   |       |        |        |                   |     |

| DQ(4!) | DQ[5]          | VSSQ          | 16 |          | チップB  | J             | Н      | G             | F           | E | D     | С      | В      | A                 |     |

| VDDC   | <b>COBI</b>    | DOZD          | 15 |          | 9     | <b>₽₽</b> [9] | 06,321 | <b>∂</b> 0 10 |             |   |       | DQ[12] | DE 131 | <b>BQ[14]</b>     | 9   |

| AD DI  | (AD PH)        | VSSQ          | #4 |          | 3     | 280           | DD-21  | PE 11         | <b>&gt;</b> |   |       | VDDE   | 96, 45 | <del>AB</del> [3] | 8   |

| VDDC   | VDDQ           | CKO(O)        | 43 | フロップ可    | 7     | WDDC          | VDDD   | VSS           |             |   |       | VSS    | VDDQ   | <b>AD</b> [2]     | 7   |

| VDDC   | VDDQ           | CK0[1]        | 12 | Atqui    |       |               |        |               |             |   |       |        |        |                   | - 6 |

| ADV21  | AD(3)          | VSSQ          | 34 |          | 5     |               |        |               |             |   |       |        |        |                   | 5   |

| VDDC   |                |               | 10 |          | 4     |               |        |               |             |   |       |        |        |                   | 4   |

| QQ(40) | <b>D2[11]</b>  | VSSQ          | 9  | 27岁      | 3     | <b>EKMD</b>   | DQ[6]  | VSS           |             |   |       | VSS    | VDDQ   | AP[1]             | 3   |

| VDDC   | VDDQ           | 00.10         | 8  | DQ[0:7]  | 2     | CK[0]         | 0851   | VDDQ          |             |   | ~     | DE [4] | DOM    | A[0[0]            | 2   |

| VDDC   | VDDQ           | 00.4P         | 7  |          |       | D67D          |        |               |             |   |       |        |        | 0000              |     |

| 009131 | D0(12)         | VSSQ          | В  |          |       | J             | Н      | G             | F           | E | D     | С      | В      | Α                 |     |

| VDDQ   | 00(15)         | DQ 14D        | 5  |          |       |               |        |               |             |   | チップBI | ま、スワッ  | グ禁止    |                   |     |

| VDDQ   | VDDQ           | VDDQ          | 4  |          | 反時計回り | J90°          |        |               |             |   |       |        |        |                   |     |

| VSSQ   | VSSQ           | VSSQ          | 3  |          |       |               |        |               |             |   |       |        |        |                   |     |

| VSSQ   |                |               | 2  |          |       |               |        |               |             |   |       |        |        |                   |     |

| VSSQ   |                |               | 1  |          |       |               |        |               |             |   |       |        |        |                   |     |

| AA     | AB             | AC            |    |          |       |               |        |               |             |   |       |        |        |                   |     |

配線が交差して、基板層数の増加が予想される

### LPB方式 ~Step3-⑤. PKG\_Aピン配置の検討~

<メモリ配線部拡大:ピン配置の修正提案>

**DQ[0:7]**と**DQ[8:15]**のグループ同士での 入れ替えが可能であれば。

従来設計:上記のような検討し、半導体メーカーへ提案(3者協議へ)

- →資料作成に手間がかかる。

- →フォーマットがバラバラなので、誤解の元となる。

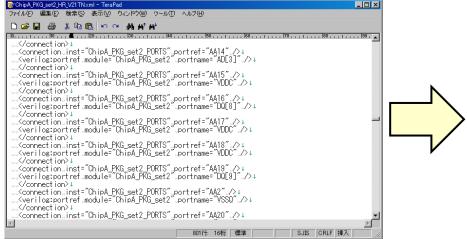

### LPB方式 ~Step3-6. PKG\_Aピン配置の検討~

#### LPB標準フォーマットを使用して修正の提案実施

```

ピン番号

<connection inst="ChipA_PKG_set2_PORTS" portref="AA16" />

<verilog:portref module="ChipA_PKG_set2" portname="DQ[4]"</pre>

</connection>

ネット名

<connection inst="ChipA_PKG_set2_PORTS" portref="AA17" />

<verilog:portref module="ChipA_PKG_set2" portname="YDDC" />

</connection>

<connection inst="ChipA_PKG_set2_PORTS" portref="AA18" />

<verilog:portref module="ChipA_PKG_set2" portname="YDDC" />

ピン番号

</connection>

Koonnection inst="ChipA_PKG_set2_PORTS" portref="AA19" /ア

Kverilog:portref module="ChipA_PKG_set2" portname="DQ[2]"

√

ネット名

</connection>

ピン番号

Kconnection inst="ChipA_PKG_set2_PORTS" portref="AA16" +++

<verilog:portref module="ChipA_PKG_set2" portname="DQ[8]" \( \square\)</p>

</connection>

ネット名

<connection inst="ChipA_PKG_set2_PORTS" portref="AA17" />

<verilog:portref module="ChipA PKG set2" portname="YDDC" />

</connection>

<connection inst="ChipA PKG set2 PORTS" portref="AA18" />

<verilog:portref module="ChipA_PKG_set2" portname="YDDC" />

</connection>

Kconnection inst="ChipA PKG set2 PORTS" portref="AA19" #

ピン番号

<verilog:portref module="ChipA_PKG_set2" portname="DQ[9]"_/>

</connection>

ネット名

LPB標準フォーマット: PKGのピン名称を変更して、半導体メーカーと交渉

→誤解がない。伝えたい内容が明確になる。

→資料作成の手間が減る。※EDAツールでの対応が前提

```

### LPB方式 ~Step3-6. PKG\_Aピン配置の検討~

#### LPB標準フォーマットを使用して修正の提案実施

```

ピン番号

<connection inst="ChipA_PKG_set2_PORTS" portref="AA16" />

<verilog:portref module="ChipA_PKG_set2" portname="DQ[4]"</pre>

</connection>

ネット名

<connection inst="ChipA_PKG_set2_PORTS" portref="AA17" />

<verilog:portref module="ChipA_PKG_set2" portname="YDDC" />

</connection>

<connection inst="ChipA_PKG_set2_PORTS" portref="AA18" />

<verilog:portref module="ChipA_PKG_set2" portname="YDDC" />

ピン番号

</connection>

Koonnection inst="ChipA_PKG_set2_PORTS" portref="AA19" /ア

Kverilog:portref module="ChipA_PKG_set2" portname="DQ[2]"→

ネット名

</connection>

ピン番号

Kconnection inst="ChipA_PKG_set2_PORTS" portref="AA16" +++

<verilog:portref module="ChipA_PKG_set2" portname="DQ[8]" \( \square\)</p>

</connection>

ネット名

<connection inst="ChipA_PKG_set2_PORTS" portref="AA17" />

<verilog:portref module="ChipA PKG set2" portname="YDDC" />

</connection>

<connection inst="ChipA PKG set2 PORTS" portref="AA18" />

<verilog:portref module="ChipA_PKG_set2" portname="YDDC" />

</connection>

Kconnection inst="ChipA_PKG_set2_PORTS" portref="AA19" #

ピン番号

<verilog:portref module="ChipA_PKG_set2" portname="DQ[9]"_/>

</connection>

ネット名

LPB標準フォーマット(現状の問題点)

→いつ誰が記載したと言ったバージョン管理が不明確

→プロジェクト管理の導入

```

#### LPB方式 ~Step4~

```

Step 1. LSI担当が階層間定義、設計制約を仮決め

(担当:ソニー 濱田)

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

## LPB方式 ~ Step4-①. 3者での打ち合わせ~

3者でJEITA LPB 標準フォーマットを用いて、打ち合わせを実施

LSI担当

PKG担当

Board担当

## LPB方式 ~Step4-②. 問題の確認~

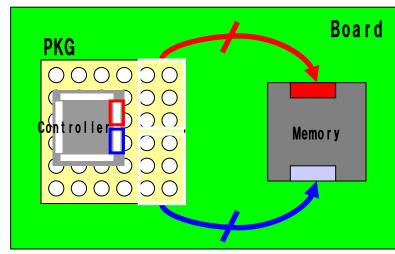

コモディティ版(WireBond)

Board上でクロス

### LPB方式 ~Step4-③. PKGボールアサインの変更~

#### 階層間定義情報(Board担当からFB)

ラッツネストがクロスしている

LPB方式: EDAツールで読み込むだけ

従来方式: 紙の仕様書を解読する必要あり

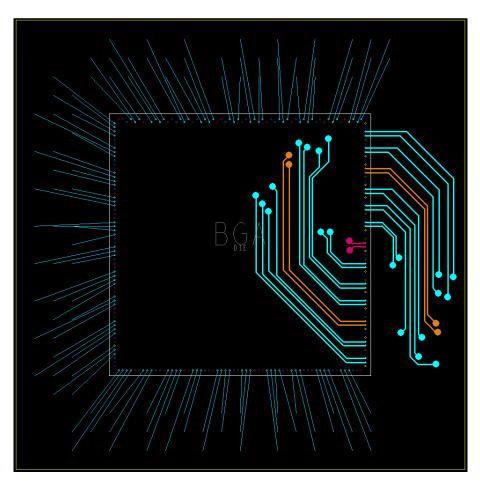

## LPB方式 ~Step4-4. PKGフィージビリティスタディ~

1層目配線パターン

3層目配線パターン

# LPB方式 ~Step4-⑤. PKGレイアウト結果~

1層目配線パターン

3層目配線パターン

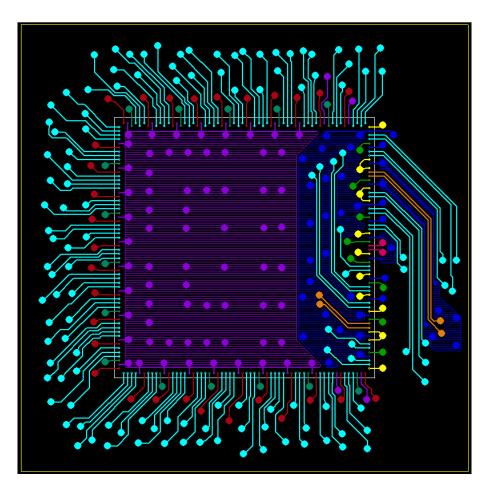

## LPB方式 ~Step4-6. Boardレイアウト結果~

### LPB方式 ~Step4. まとめ~

#### JEITA LPB標準フォーマットについて

### EDAベンダー各位 御検討願います!!

#### メリット

- ・修正内容の伝達が容易になり、 設計するまでの準備時間の大幅な短縮が期待できる。

- ・誤解によるミス防止や確認のための時間短縮が期待できる。

## デ<u>メリット</u>

- ・現時点でEDAツールが対応していない。

- ・やり取りが増えると、バージョン管理が必要。

- ・LPB標準フォーマットは、EDAツールにやさしく人に厳しい。 ※LPB標準フォーマットのViewing機能が必要。

#### LPB方式 ~Step5~

```

Step 1. LSI担当が階層間定義、設計制約を仮決め

(担当:ソニー 濱田)

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

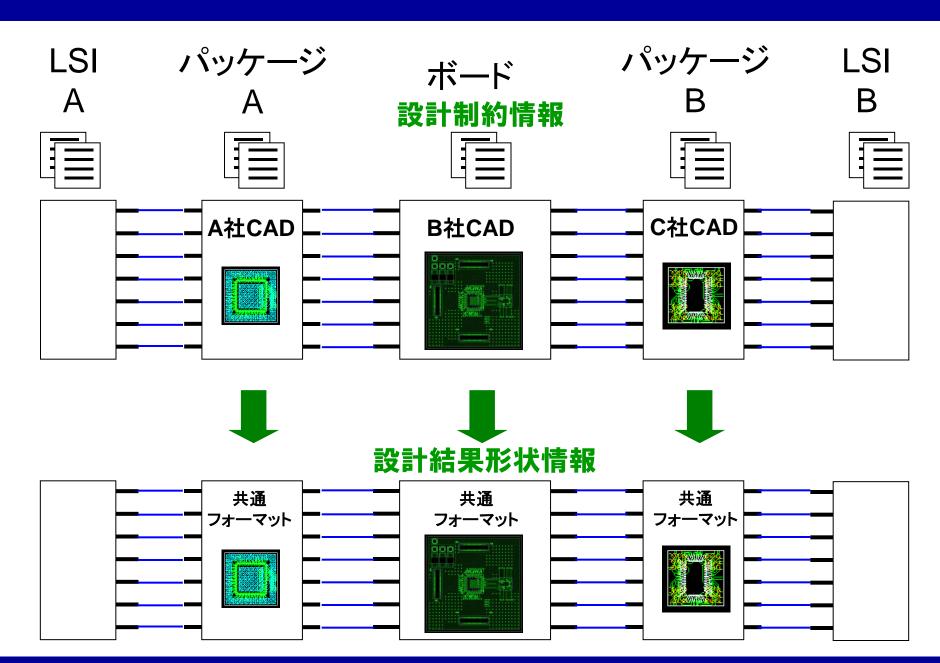

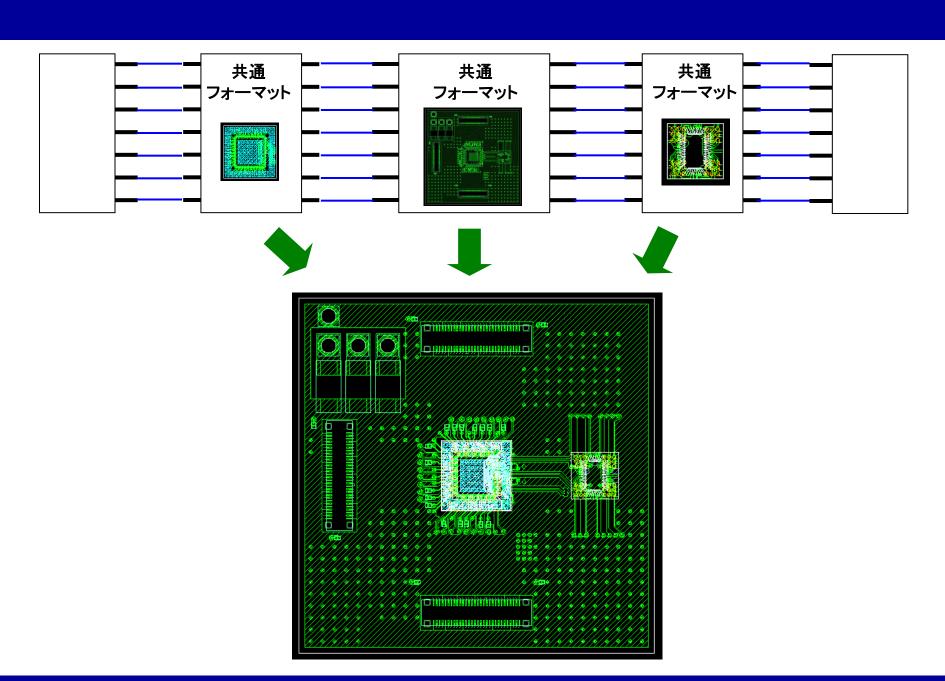

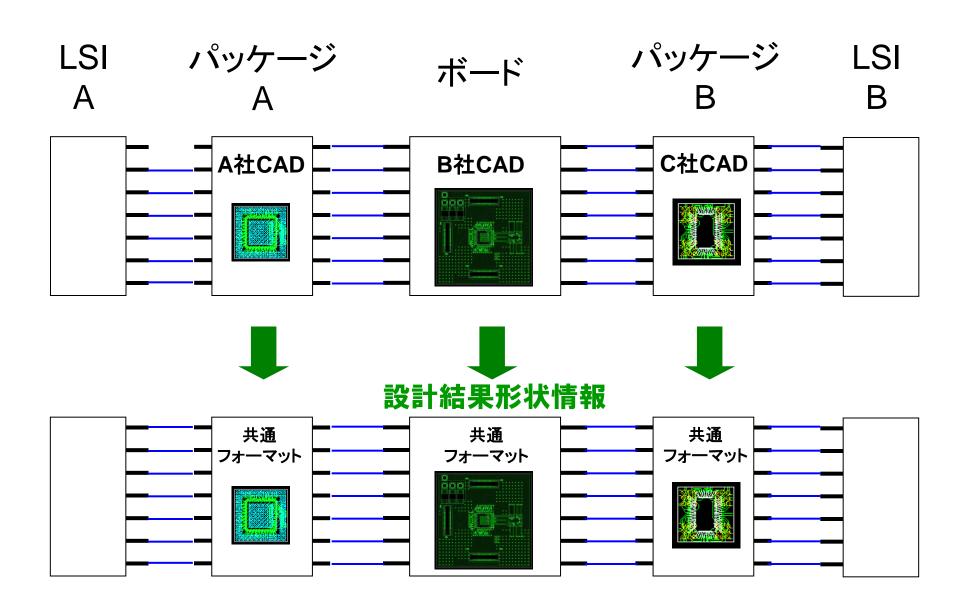

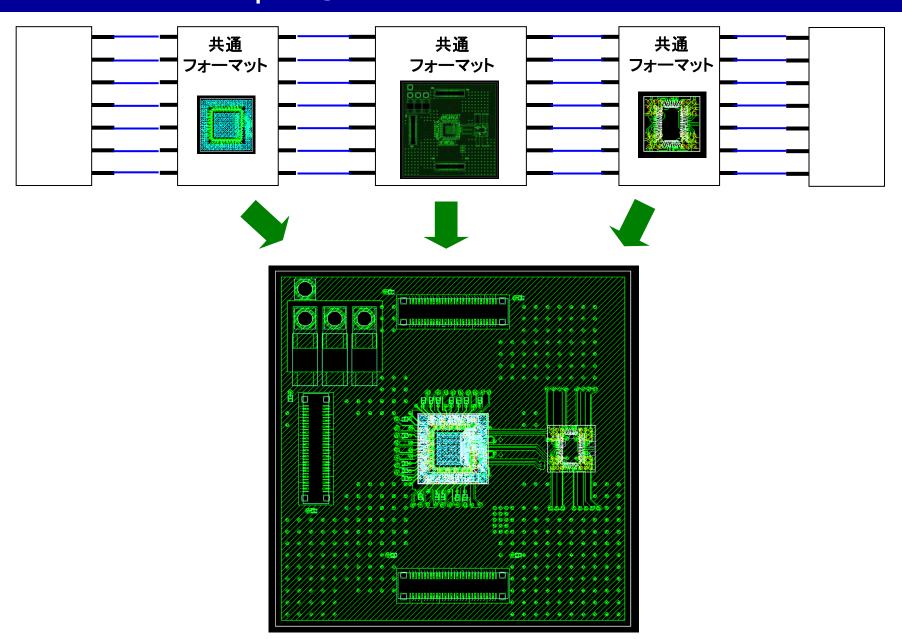

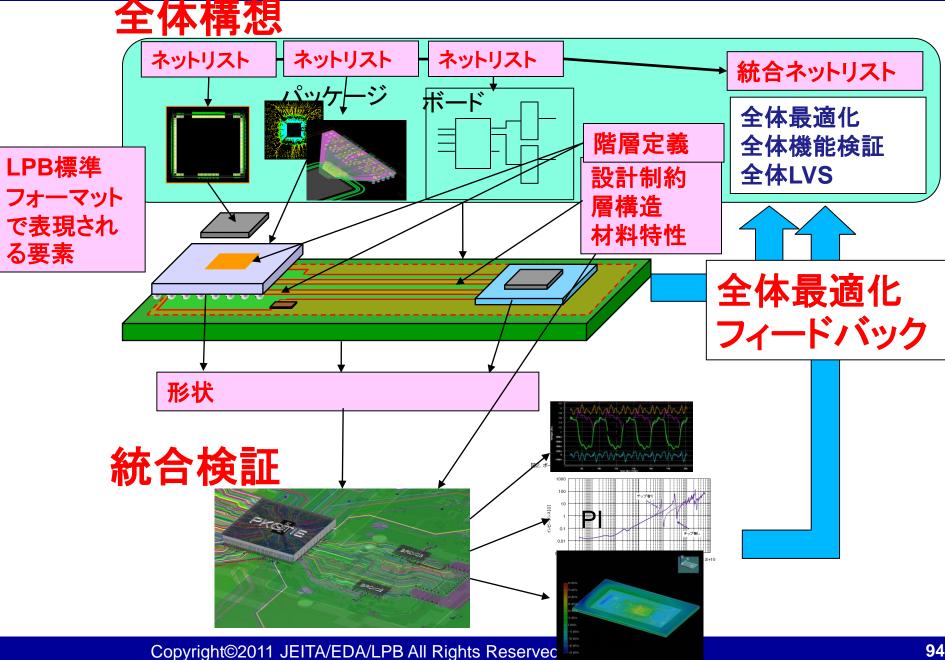

## LPB方式 ~Step5-①. LPB標準フォーマットに変換~

## LPB方式 ~Step5-②. LPBデータの結合~

#### LPB方式 ~Step6~

```

Step 1. LSI担当が階層間定義、設計制約を仮決め

(担当:ソニー 濱田)

Step 2. PKG担当が階層間定義、設計制約を仮決め

(担当:富士通セミコンダクター 小澤)

Step3. Board担当が階層間定義、設計制約を仮決め

(担当: トッパンNEC 金子)

Step4. LPB3者で階層間定義、設計制約について議論を実施し、本決め

Step5. 各担当がレイアウト設計を実施

LSI、PKG、BoardのデータをLPB標準フォーマットに変換

Step6. シミュレーションを使った検証を実施

(担当:デンソー市川、津田)

```

## LPB方式 ~Step6-①.シミュレーションによる設計検証

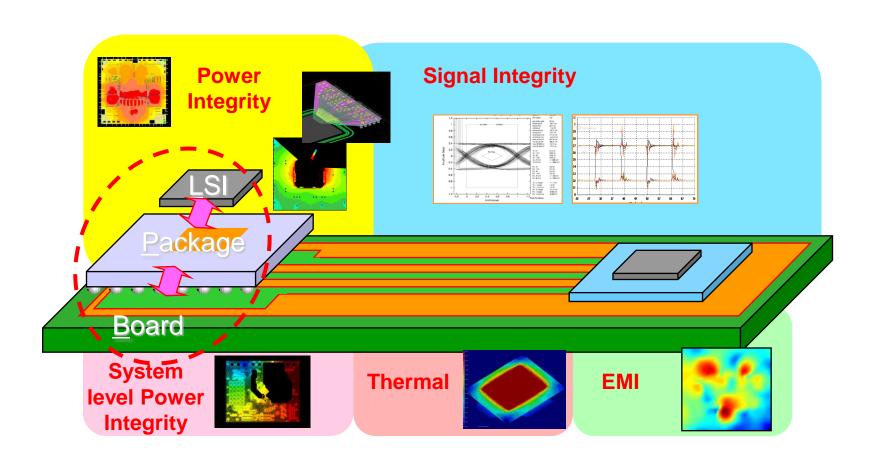

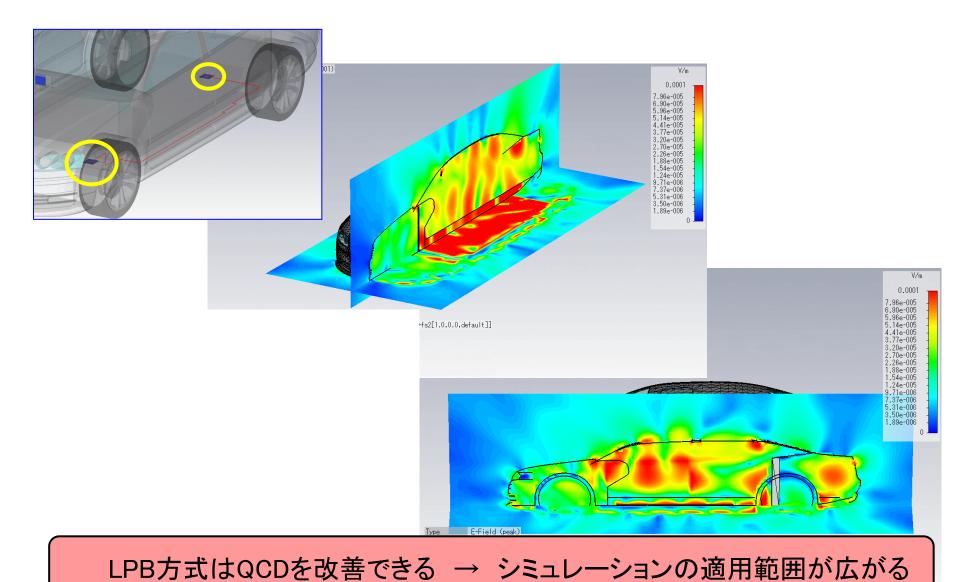

複雑化する設計制約(熱、EMC、SI、PI...)条件 各設計フェーズ、各階層において シミュレーション活用による制約条件の確認

#### シミュレーション環境に関する課題

シミュレーションに必要な事前準備工数・時間が大

- ・LSI、Package、Boardの各CADでのデータを 各シミュレータで扱うための調整

- ・LSI、Packageデータ、特性の入手、準備

十分なシミュレーション時間を確保できない 工数をかけても正確な特性を把握することが難しい

#### 設計検証におけるLPB期待効果

LPBフォーマットによる準備工数の削減 シミュレーションに必要な設計・特性情報、 フォーマットの定義による事前準備時間を削減

LPB協調設計による解析精度向上 解析モデルの流通による精度向上が可能

協調して制約条件を最適化

### LPB方式 ~Step6-②.シミュレーションについて~

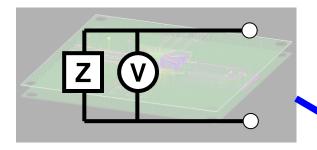

#### 【 解析する対象 】

SI解析 : ドライバ、レシーバのeyeパターン

PI解析: LSIから見た電源インピーダンス

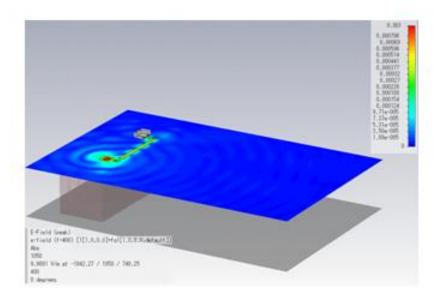

EMI解析①: 基板からの放射ノイズ (ノイズ試験ベンチ)

EMI解析②: LPB + 試験環境 、複数のLPB + 車両

## LPB方式 ~Step6-③.解析モデルの概要~

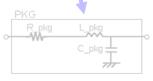

## LPB方式 ~Step6-④.データ入力作業時間 比較1~

従来方式

作業時間:5H 問い合わせ待ち:1日以上

ボータ入手・問い合わせ: Min 1日 加工・ポート割り当て作業: 2H

データ入手・問い合わせ: Min 1日

<u>加工・ポート割り当</u>て作業:1H

基板のインポート/修正:2H

※各社固有のCADデータを想定

■:待ち ■:手作業 ■:自動作業 LPB方式

作業時間:1日未満 問い合わせ待ち:ゼロ

ほぼ自動化 → 手作業ミスの低減

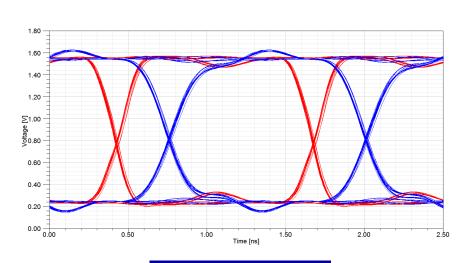

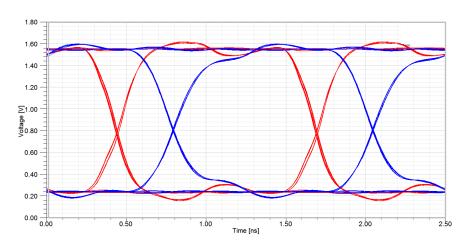

#### LPB方式 ~Step6-⑤.SI解析の比較 (eyeパターン)~

#### <SI解析条件> DDR2 SDRAM

対象ネット: DQ8 条件: Write時、PRBS7、400MHz

赤:コントローラ(LSI-A)

青:メモリ(LSI-B)

従来方式

LPB方式

SI解析では解析結果に差はない

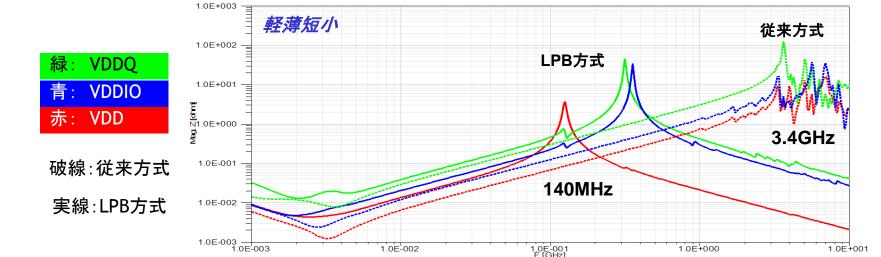

#### LPB方式 ~Step6-⑥. PI解析の比較(インピーダンス)~

#### <PI解析条件> 電源系インピーダンス 対象ネット: VDD、VDDIO、VDDQ

#### LSI及びPKGのモデル有無によりインピーダンスは大きく異なる

#### 【解析範囲と対象】

従来方式 : 対象=Board 、 Board上のPKG用PADから見たインピーダンス

1.0E-001

1.0E+000

LPB方式 : 対象=LSI+PKG+Board 、 ダイから見たインピーダンス

差

1.0E-002

厳しい設計制約に応えるには、LPB方式で用意できるLSI+PKGのモデルが必要

1.0E+001

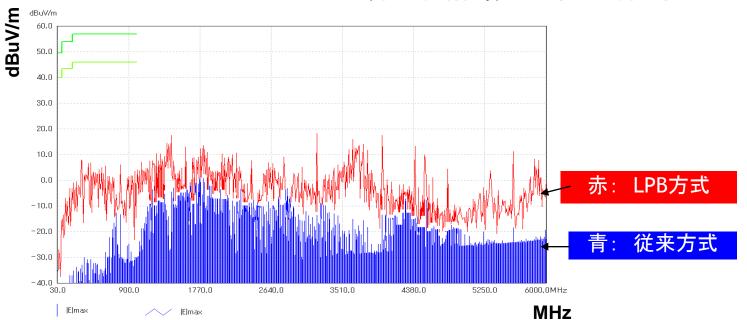

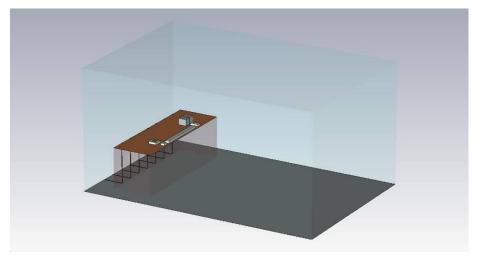

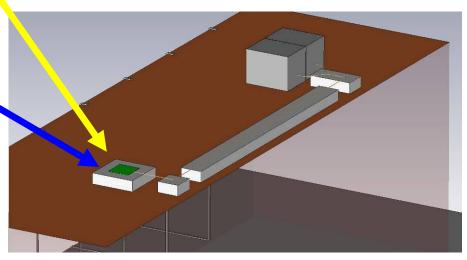

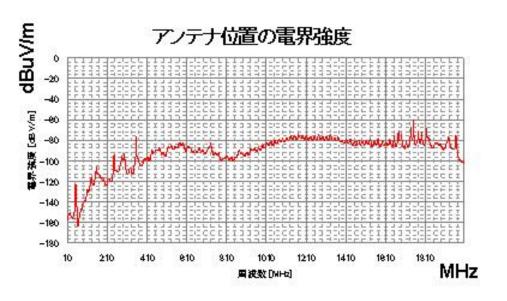

#### LPB方式 ~Step6-⑦. EMI解析①の比較 (放射ノイズ)~

#### <EMI解析条件> 電源系+IO系

対象ネット: VDD、VDDIO、VDDQ、DQ8、DQS

【解析条件】

CISPR22想定の環境 、条件: 30MHz~6GHz 、10m位置の電界強度

床面: 反射計算なし、壁/天井: オープン

#### 【解析対象】

従来方式 : 対象= LSI(IBIS) + PKG(RLC)+ Board

LPB方式 : 対象=LSI(CPM / LPM + IBIS) + PKG(CAD) + Board

電源系LSIモデルを入れなければ放射ノイズ解析として利用できない

#### LPB方式 ~Step6-⑧.データ入力作業時間 比較2~

従来方式(LPB方式と同等)

作業時間: 15H 問い合わせ待ち: 1週間以上

データ入手・問い合わせ: Min 1週間

加工・ポート割り当て作業:2H

データ入手・問い合わせ:Min 1週間

PKG形状調査 / データ作成: 10H

加工・ポート割り当て作業:1H

基板のインポート/修正:2H

※各社固有のCADデータを想定

■:待ち ■:手作業 ■:自動作業 LPB方式

作業時間:1H未満 問い合わせ待ち:ゼロ CPM / LPM / IBIS CPM / LPM / IBIS 割り当て:3min 割り当て:3min 修正:0.5H 基板のインポート/設計条件入力

ほぼ自動化 → 手作業ミスの低減

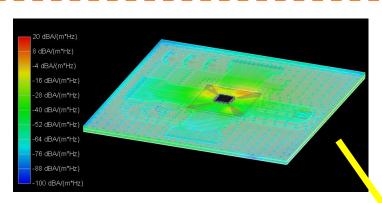

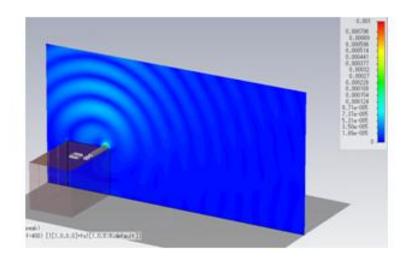

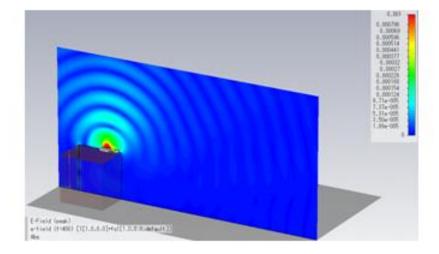

#### LPB方式 ~Step6-9. EMI解析② [LPB+試験環境]~

Near-Fieldデータ(基板放射源のモデル)

基板モデル+コネクタ間電圧値 (伝導ノイズ源のモデル)

LPBモデルをシミュレータで作成

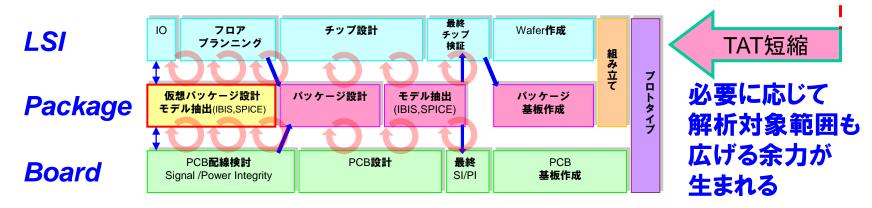

LPBまでのシミュレーションに必要な時間を大幅に 短縮できるため、さらに大きな範囲でのシミュレー ションを検討する時間が作れる

CISPR25 試験環境の3Dモデル

モデルとして統合し、スケール差を吸収

# LPB方式 ~Step6-⑩. EMI解析② [LPB+試験環境] ~

#### LPB方式 ~Step6-①. EMI解析② 【複数のLPB+車両】~

#### アジェンダ

- 背景

- 適用事例の説明

- 従来方式

- LPB方式

- 総括

#### 総括 ~実施内容~

✓開発の初期段階からLPBがコンカレントに協調し合い最適化 検証を進められるように、LPB相互設計WGを行なっている。

✓その手段として、LPB各設計の入出力の標準化を行なった。 (4つのLPB標準フォーマットと用語集を用意)

✓LPB標準フォーマットの有効性を検証するため、従来型と LPB型で実際に設計をし、検証を行なった。

#### 総括 ~検証結果~

#### ✓その結果、従来型は

- 人為的ミスの発生リスクが高い(あいまいさが原因)

- 資料作成に時間を要する

- 設計前の全体最適化が困難

- ・解析までに時間がかかる(LPBの接続確認が困難) ことが改めて確認された。

### 一方、LPB型は

- ・フォーマットに記載する為、定義の「あいまいさ」が排除

- •EDAツールが対応すればフォーマット出力が容易

- •EDAツールが対応すれば構想設計検証が容易になり、 設計前に全体最適しやすい

- •EDAツールが対応すればLPBモデルの作成が容易になることが検証できた。

# 総括 ~LPB標準フォーマット作成時間~EDAツール対応が前提

標化るき分

#### 総括 ~検証結果~

#### ■現在の主な設計手法:

•チップ、パッケージ、システムが別々に設計されて最後に全体の検証を行う。

#### ■ LPBコンカレント協調設計:

•開発の初期段階からコンカレントに協調しあって最適化設計と検証を進める。

#### 総括 ~まとめ~

Q 解析精度向上、作業ミスの防止が期待できる

C 作業工数の大幅な削減が可能

D 問い合わせ待ち時間ゼロ化による納期短縮

+α 解析対象範囲を広げる余力が生まれる

#### 総括 ~課題~

- ✓EDAツールがLPB標準フォーマットに対応する必要がある。

- ✓LPB標準フォーマットのバージョン管理が不明確である。 →プロジェクト管理の導入が必要?

- ✓LPB標準フォーマットの文法チェックが必要である。

- ✓レビュー用に、LPB標準フォーマットの内容をViewingできる 必要がある。

#### LPB標準フォーマットの次バージョンで検討中。

# LPB相互設計のwebページよりプレビュー版として ver1.0が入手可能

http://www.jeita-edatc.com/wg\_lpb/home/lpb.html

# 2部

LPB相互設計と標準フォーマットの普及について

#### アジェンダ

- メンバー紹介

- ASP-DAC お知らせ

- ■討議

- LPB相互設計による設計スタイル変革

- LPB標準フォーマットのEDAへの採用

- 総括

# Designers' Forum 2011 Co-Chair)中川 祐之富士通VLSI(株) ASIC・COT 開発統括部 第三設計部田中 修治ソニー(株) プロフェッショナル・デバイス&ソリューショングループ 半 導体事業本部 設計基盤技術部門 ミックスシグナルデザインソリューション部 担当部長

リーダー

ニア

スペシャリスト

会社•団体名 所属

出演者氏名

永田 真

齊藤 義行

第2部司会

吉田 敦史

総合司会

福場 義憲

澤田修メンター・グラフィックス・ジャパン(株) マーケティング部フィールド・マーケティング・マネージャー古賀 一成(株) 図研 技術本部 ELNセクション コデザイングループ チーフエンジ

神戸大学大学院 システム情報学研究科 教授 ASP-DAC

パナソニック(株) PE技術開発室 EMCデザイン第一チーム チーム

(株)リコー 電子デバイスカンパニー 第一生産室 第一技術グループ

JEITA EDA技術専門委員会LPB相互設計WG 主査、 (株) 東芝 セミコ

#### ASP-DAC のご案内 (1/2)

米国のDAC, ICCAD, 欧州のDATEと並び、アジア・南太平洋地区最大のLSIの設計・設計自動化に関する国際会議

基調講演、一般講演、特別セッション、デザイナーズフォーラム、 ユニバーシティLSIデザインコンテスト等、 多数の最先端設計技術に関する講演をご用意

EDSFairとの連携企画も実施(本セッション)

#### ASP-DAC のご案内 (2/2)

今年度: ASP-DAC 2012 2012年1月30日~2月2日 シドニーコンベンションセンター 参加者募集中

次年度: ASP-DAC 2013 2013年1月22日~25日 パシフィコ横浜(予定)

第一線の設計者の皆様にも魅力的なプログラムをご用意致しますので、是非ともご参加をお願い致します 詳細は、http://www.aspdac.com をご覧下さい

#### LPB相互設計の効果 (縦軸:時間)

#### 設計・検証環境とLPB標準フォーマット

#### 総括

- ■LPB相互設計により設計の分業・連携の構造 変革が進み、競争力強化につながる。

- ■LPB標準フォーマットはその変革の道具となる。

■EDAのLPB標準フォーマット採用が必須。

- > 今後

- 正式版 LPB V2.0の策定 (2012年3月LPB-WGにて)

#### お知らせ

## LPB相互設計のwebページ LPB V1.0ダウンロード可能

http://www.jeita-edatc.com/wg\_lpb/home/lpb.html