# ばらつきの現状と将来動向

京都大学情報学研究科 通信情報システム専攻 小野寺秀俊

### ばらつきの現状と将来動向

- ばらつきの要因

- ■ばらつきの分類

- ばらつきを観察する

- 0.35μm

- 0.18μm

- 0.13μm

- 90nm

- ばらつきの将来動向

- 物理量のばらつき

- 製造プロセス/素子構造のばらつき

- 環境(電圧、温度)のばらつき

- 設計量のばらつき

- ▶予測誤差

- 評価誤差

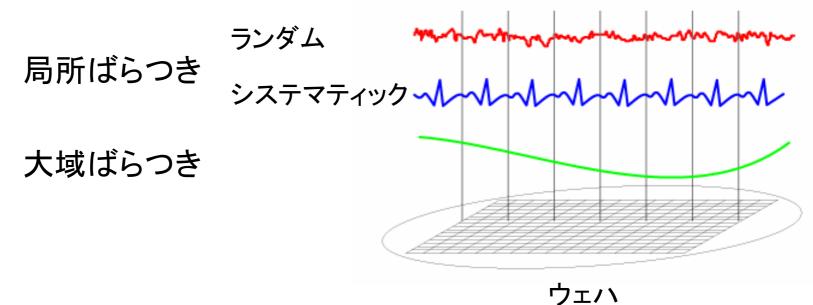

## ばらつきの分類

- 大域ばらつき(Inter-die)

- ロット間(L2L), ウェハー間(W2W), チップ間(D2D)ばらつき

- 局所ばらつき(Intra-die)

- チップ内(WID, OCV, ACV, etc.), セル内ばらつき

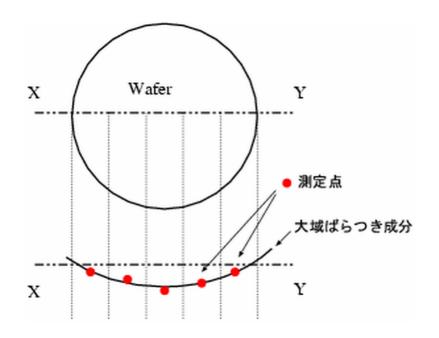

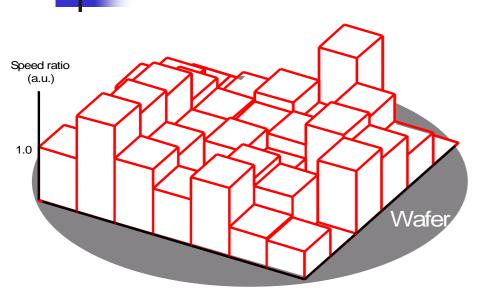

#### 大域ばらつき

- ロット間、ウェハ間のばらつき

- ウェハ内での位置に依存してなだらかに変動

- 製造時のウェハ内温度勾配やレチクル内の光路差など

## 局所ばらつき (Intra-die variations)

- ランダムばらつき

- 製造時のガウス雑音

- 物理パラメータや環境パラメータが確率分布を持つ

- 実測値の集合として表現したり、正規分布などの確率密度関数でモデル化

- 空間的相関(spatial correlation)を持つ場合がある

- システマティックばらつき

- レイアウト依存ばらつき(パターン密度、OPE, CMP, STI等)

- レンズ収差などによるチップ内の線幅変動(ACLV: Across-Chip Line-width Variation)

## ばらつきを観察する

- 0.35μm

- Lot-to-Lot, Wafer-to-Wafer, Die-to-Die(D2D)

- 多くは D2D

- 0.18μm

- システマティックなチップ内ばらつきが存在

- D2D vs. WID

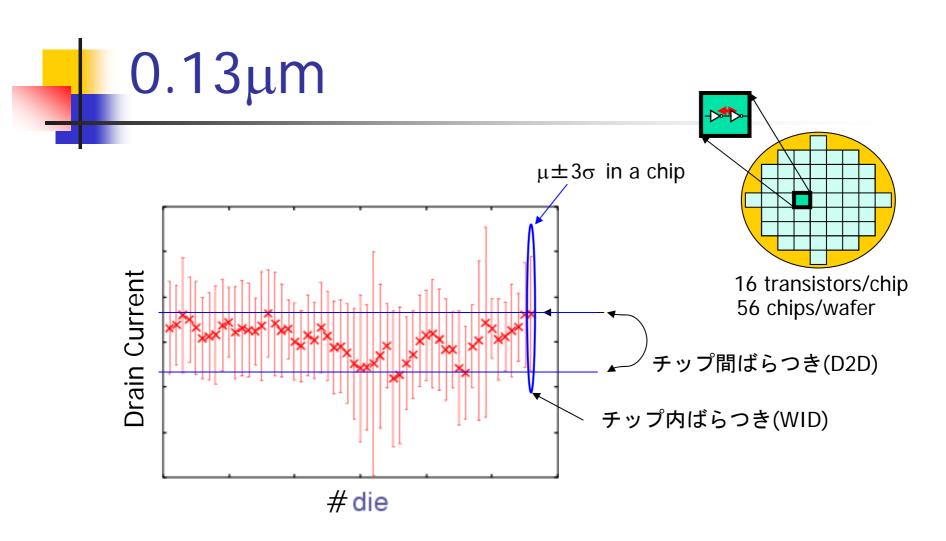

- 0.13μm

- D2D vs. WID

- 90nm

- D2D vs. WID

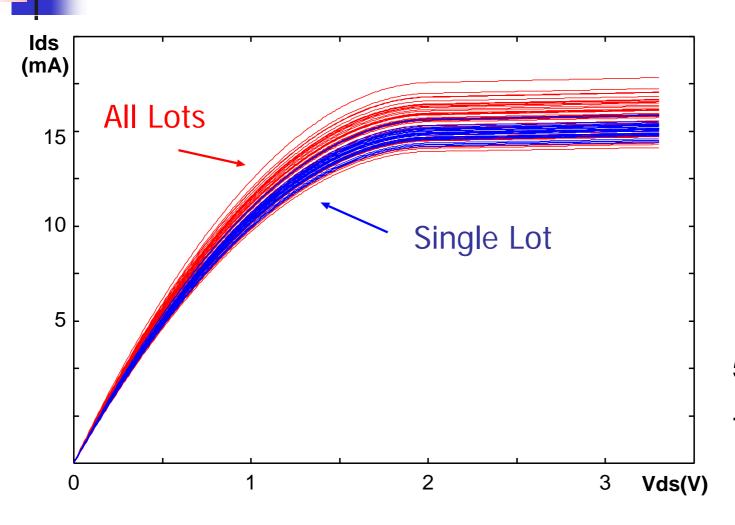

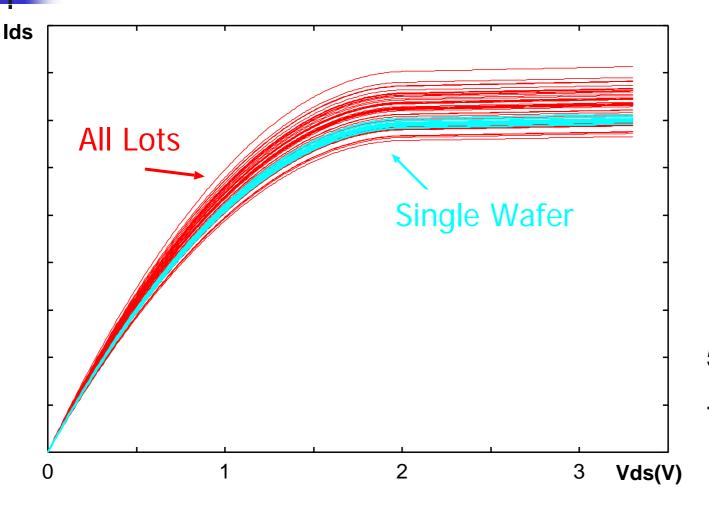

## 0.35μm:Good Old Days

58 Lots,797 Wafers

## 0.35µm, 大部分がD2D

58 Lots,797 Wafers

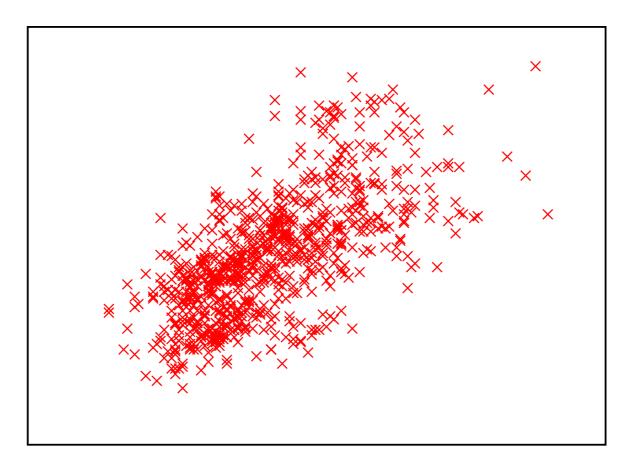

### 0.35μm Id\_sat (pMOS vs nMOS)

相関を含むモデル化が重要(どのように予想できるか?)

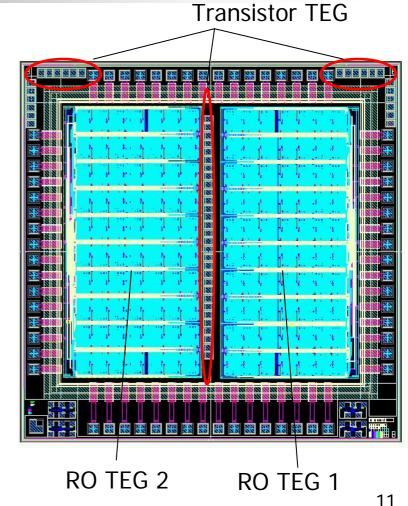

## $0.18\mu m$

- ばらつき評価 TEG 0.18µm, 2.9 mm 角, 20 チップ

- トランジスタTEG

- Ids ばらつきの測定

- 16 Transistors/chip

- Ring OSC TEGs

- 発振周期のばらつき測定

- 20 種類のRO 合計2,800個

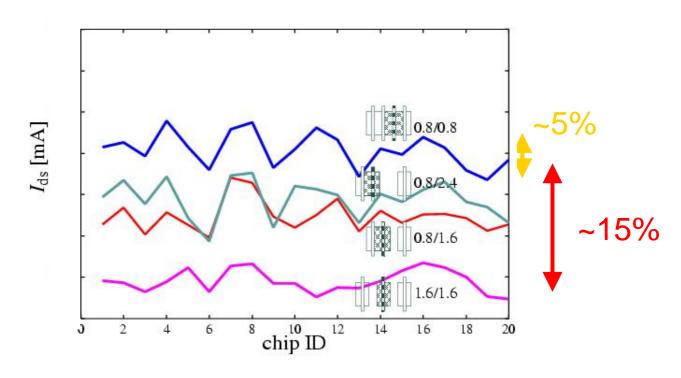

## 0.18μm, システマティックなWID ばらつき

- 各レイアウトスタイル内で約 5% のばらつき

- 稠密なレイアウトと疎なレイアウトで、約 15% の差

- レイアウト依存の(システマティックな)ばらつきのモデル化が重要

## 0.18μm: Ring OSC TEG

- 発振周期のばら つきの測定

- Inv のRO

- 段数:7,13,19,29

- 駆動力:5,10,20,40,60,

- NAND2, NAND4ØRO

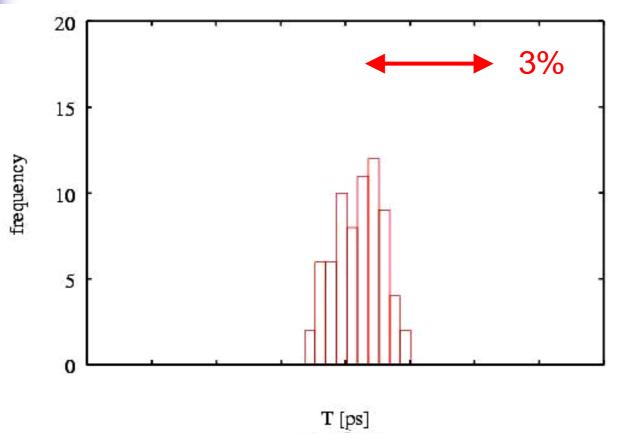

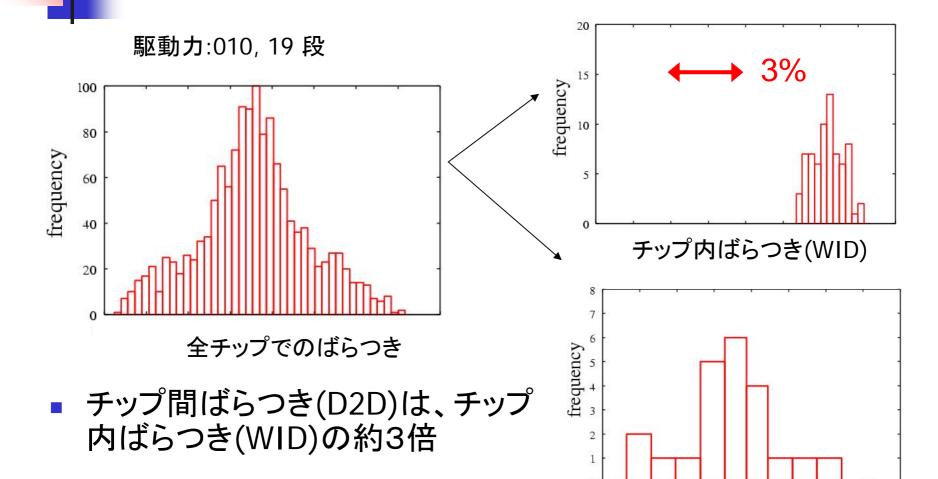

## 発振周期のヒストグラム: チップ内(WID)

段数: 19 駆動力:010 合計70 回路

チップ毎に平均値は異なるが、ばらつきの幅はほぼ同じ

#### 発振周期のヒストグラム

チップ間ばらつき(D2D)

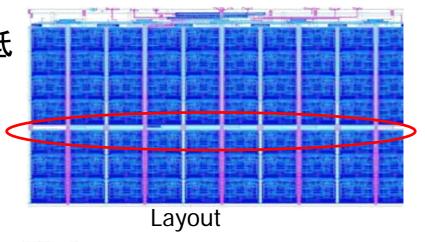

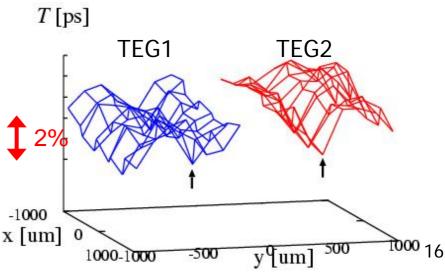

## 発振周期のチップ面内分布

電源線近傍で発振周期の低下を観測

下を観測ポリ密度: 小さい

Ids: 大きい

発振周期:短い

発振周期に約 1% の差 TEG 1 < TEG 2</li>

ポリ密度に1%の差 TEG 1 < TEG 2</li>

レイアウト依存ばらつき

チップ内ばらつき(WID)がチップ間ばらつき(D2D)より大きくなる

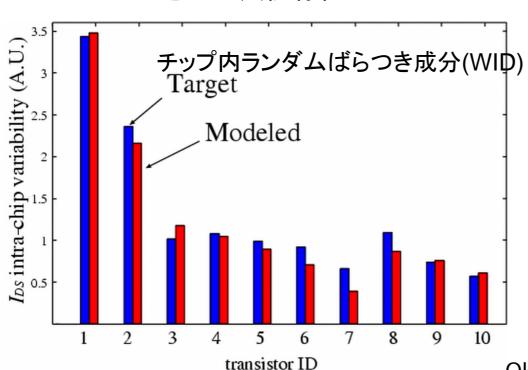

## 0.13μm: Ids ばらつき

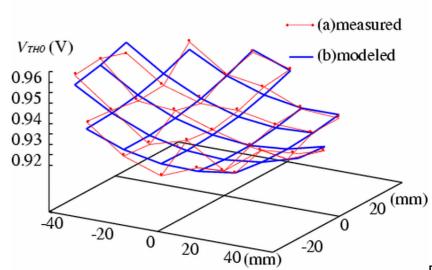

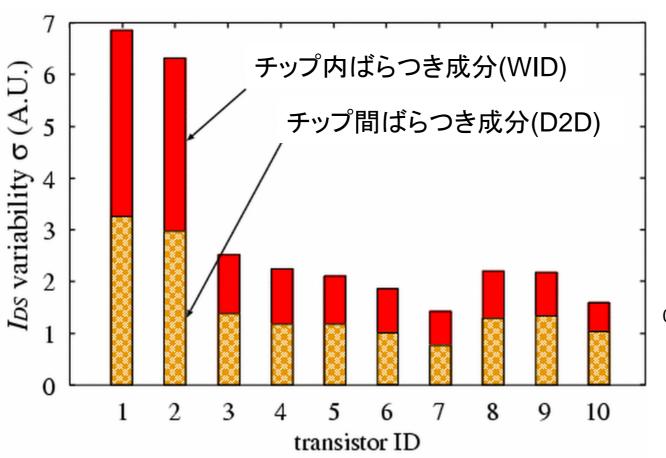

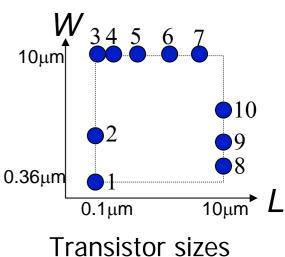

## チップ内ばらつき成分のモデル化

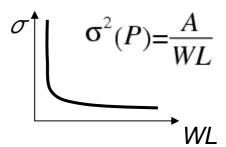

#### Ids ばらつきの寸法依存性

$$V_{DS}=0.1(V)$$

,  $V_{GS}=1.0(V)$

[Pelgrom, et al., J-SSC 1989]

Okada et.al., JJAP, p.131, 2005

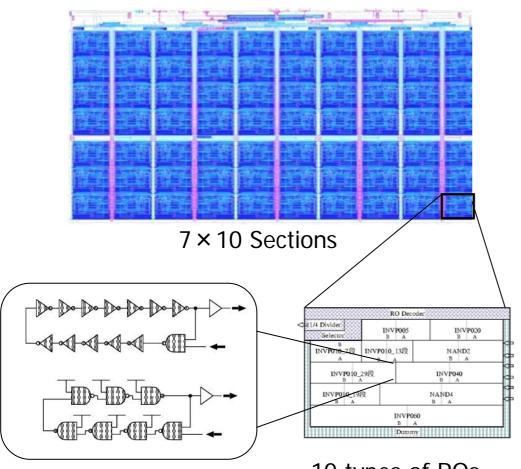

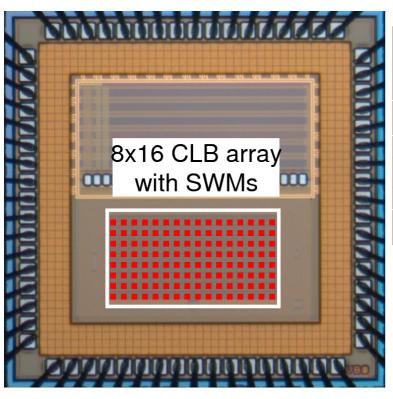

#### 90nm FPGA

| Process   | 90nm 6Layer-Metal              |

|-----------|--------------------------------|

|           | CMOS                           |

| # of Trs. | .5M                            |

| Area      | $2.5$ mm $\times 2.5$ mm(Die), |

|           | 0.6mm <sup>2</sup> (FPGA core) |

| # of IOs  | 16 (for FPGA)                  |

Kotani et.al., ESSCIRC'06, p.110.

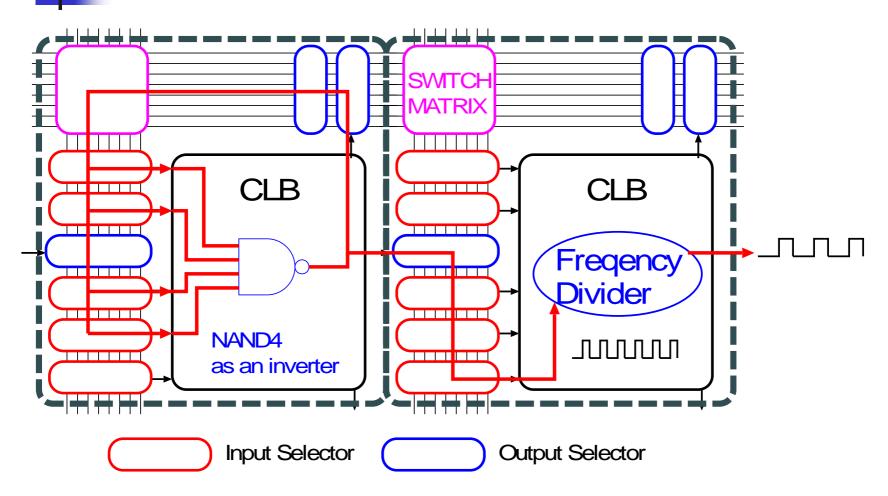

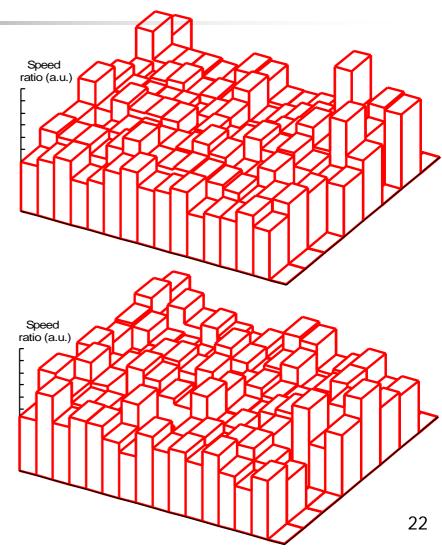

## CLBによるRing OSC

## 動作速度のばらつき

■ D2D ばらつき

■ WID ばらつき

### ばらつきの将来動向

- 露光波長(193nm)を遥かに超えた微細化

- 露光性、加工性の劣化によるばらつき増加

- 微細化に内在する本質的な揺らぎの増加

- チャネル内不純物数減少による不純物の数 や場所の揺らぎ (Discrete Dopant Fluctuation)

- ゲートエッジの粗さ (LER:Line Edge Roughness)

- ばらつきを知る

- ばらつきの計測と解析技術

- ばらつきのモデリング技術

- ばらつきの影響を評価する

- 統計的STAの実用化技術

- ばらつきを克服する

- ばらつきを許容する回路技術

## ばらつきの現状と将来動向

- ばらつきの要因

- ■ばらつきの分類

- ばらつきを観察する

- 0.35μm

- 0.18μm

- 0.13μm

- 90nm

- ばらつきの将来動向