主査 松下電器 川上 善之 |

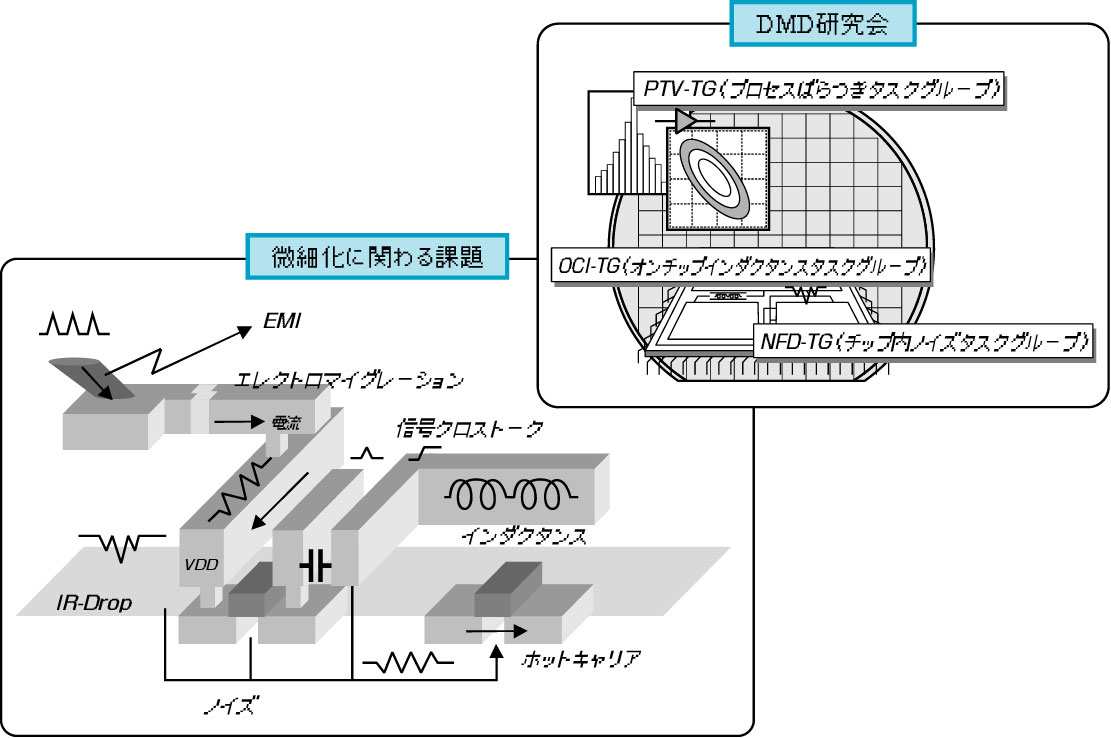

| ■ 目的 0.1ミクロンルール時代の到来を目前にして、システムオンチップ化と超微細プロセスに起因する種々の問題が顕在化しつつある。すなわち、1)スケールダウンしない配線容量および配線抵抗の増加による配線ディレイの大幅増加、2)IRドロップ、クロストークノイズ・EMIノイズ等のシグナルインテグリティー問題、3)製造プロセスや周囲環境によるLSIの性能ばらつきの増大、4)消費電力の増大、などである。 本研究会は、デシミクロン時代におけるLSI設計のこれら諸問題について、半導体メーカー・EDAベンダーの間で課題を共有し、これらの解決に向けて取り組む。 ■ 活動内容 次の3つタスクグループにおいて、設計ソリューションの視点で検討と提案、並びに、EDA環境(ツール)の整合化・標準化を目指していく。 (1)オンチップインダクタンスタスクグループ(OCI-TG) タイミング解析・検証の高精度化のために、特に配線インダクタンスに関する課題を検討テーマとする。具体的には、(1)遅延計算に関連した文献調査及び(2)インダクタンスが設計に与える影響の定量的な把握、を行い、結果を広く公開する。 <主な対外活動成果> 1)「インダクタンスが配線遅延に及ぼす影響の定量的評価方法」:第15回回路とシステム 軽井沢ワークショップにて発表(2002年4月) 2)「0.1μm級LSIの遅延計算における寄生インダクタンスを考慮すべき配線の統計的選別手法」:情報処理学会 DAシンポジウム2002にて発表(2002年7月) 3)「インダクタンスに起因する配線遅延変動の統計的予測手法」: 電子情報通信学会 秋季ソサイエティ大会チュートリアル講演(2002年9月) 4)"An Accurate Prediction of the Impact of On-Chip Inductance on Interconnect Delay Using Electrical and Physical Parameter-based RSF":ASP-DAC2003(2003年1月) (2)プロセスばらつきタスクグループ(PTV-TG) LSIの微細加工技術の進展に伴い、温度、電圧などの使用条件の変動や製造プロセスのばらつきに起因するLSI性能のばらつきが増大している。こうしたばらつきを設計段階で高精度に見積もる技術について検討する。 <主な対外活動成果> 「プロセスばらつきを考慮した遅延計算モデルの提案とばらつき要因解析」 電子情報通信学会秋季 ソサイエティ大会チュートリアル講演(2002年9月) (3)チップ内ノイズタスクグループ(NFD-TG) デバイス・配線の微細化と高密度化、さらには動作の高速化や低電圧化などの要因により、デジタル回路であっても設計過程でノイズを考慮することが必須となっている。設計の煩雑化を避けながらノイズによるLSIの誤動作を避けるため、設計者にノイズを意識させないNoise-Free Design(NFD)を実現するための設計手法、EDAツールを検討する。 <主な対外活動成果> 「インダクタンス起因ノイズのトレンド - クロストークとdI/dtノイズ」: 電子情報通信学会秋季 ソサイエティ大会チュートリアル講演(2002年9月) ■ 関連機関 (1) SI2:IEEE1481 DPCS(Delay and Power Calculation System)の標準化等を推進。 http://www.si2.org/ (2) Accellera:IEEE1603 ALF(Advanced Library Format)の標準化等を推進。 http://www.accellera.org/ (参加メンバ) 14社/17名 (主査:川上善之/松下電器)、 ほか客員2名 |

JEITA/EDA技術専門委員会ホームページに戻る |